Duty ratio correcting circuit

A duty cycle correction and duty cycle technology, which is applied in the field of signal processing, can solve the problems that the operating frequency cannot be too high, the correction result cannot be obtained, and the correction accuracy is discrete, so as to achieve strong anti-interference ability, avoid flipping and timing disorder. , the effect of suppressing temperature drift

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

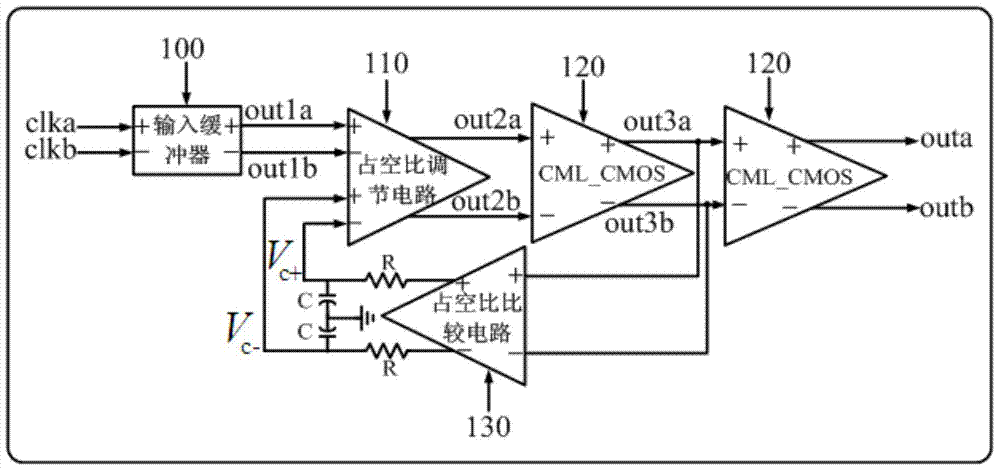

[0047] see figure 1 and image 3 , a duty ratio correction circuit provided by an embodiment of the present invention is used to adjust the duty ratio of a differential signal in real time; including:

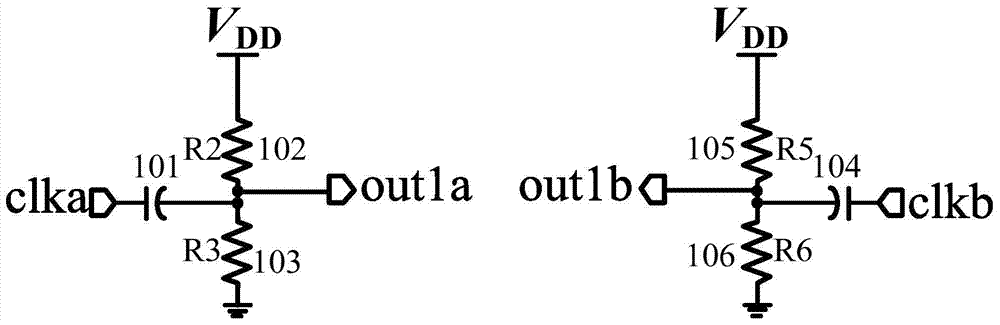

[0048] The input buffer 100 is used to receive the differential signals clka and clkb, realize the preliminary adjustment of the duty cycle of the differential signal by setting the common mode level, and output the signals out1a and out1b;

[0049] A duty cycle adjustment circuit 110, configured to receive signals out1a and out1b, adjust the duty cycle, and output signals out2ah and out2b;

[0050] The first-stage CML-to-CMOS circuit 120 is used to receive the signals out2a and out2b, amplify and shape the swing, and output the signals out3a and out3b;

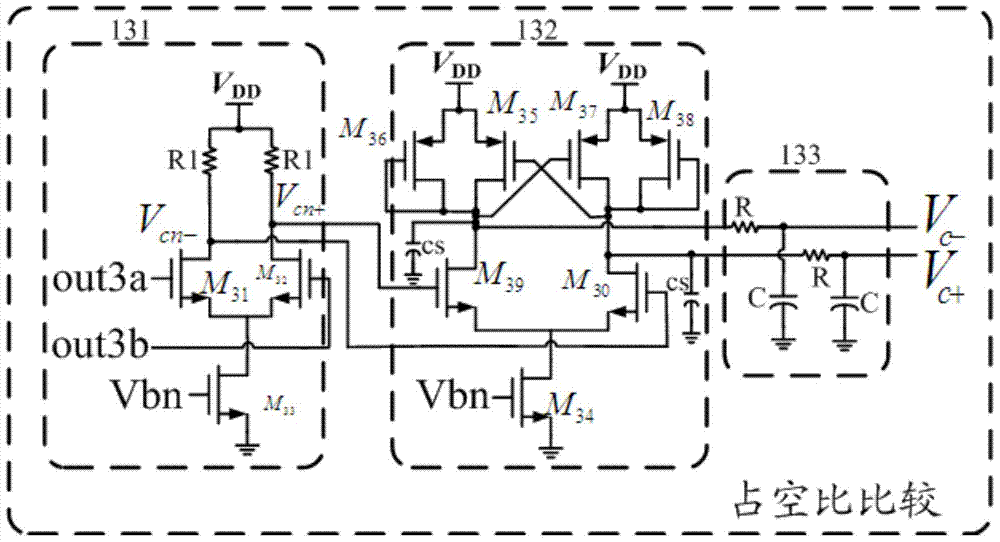

[0051] The duty cycle comparison circuit 130 receives the signals out3a and out3b, extracts the duty cycle information, amplifies and integrates the duty cycle error, and outputs the differential control voltage V c + and V...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More