Multi-PDN type current mode RM logic circuit

A logic circuit and current mode technology, applied to logic circuits with logic functions, etc., can solve the problems of no RM logic compound gate logic unit, no power consumption optimization RM logic standard unit, etc., to achieve good power consumption effect, low Effects of Power Consumption, Latency, and Power Delay Product Reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

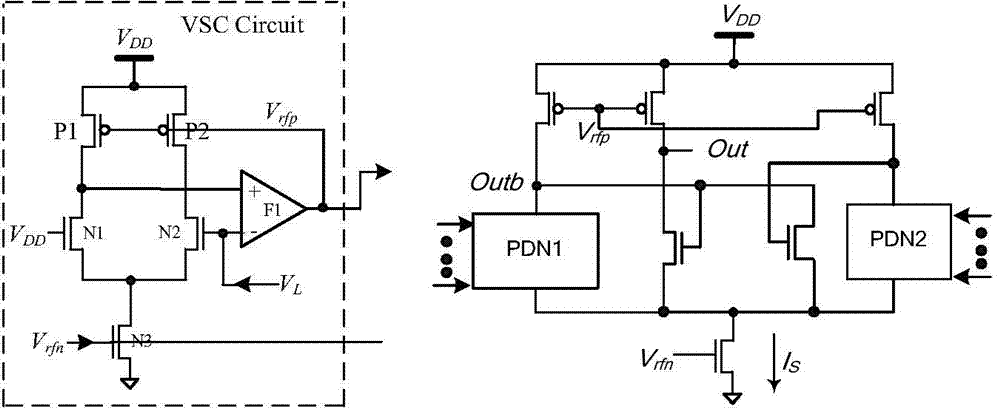

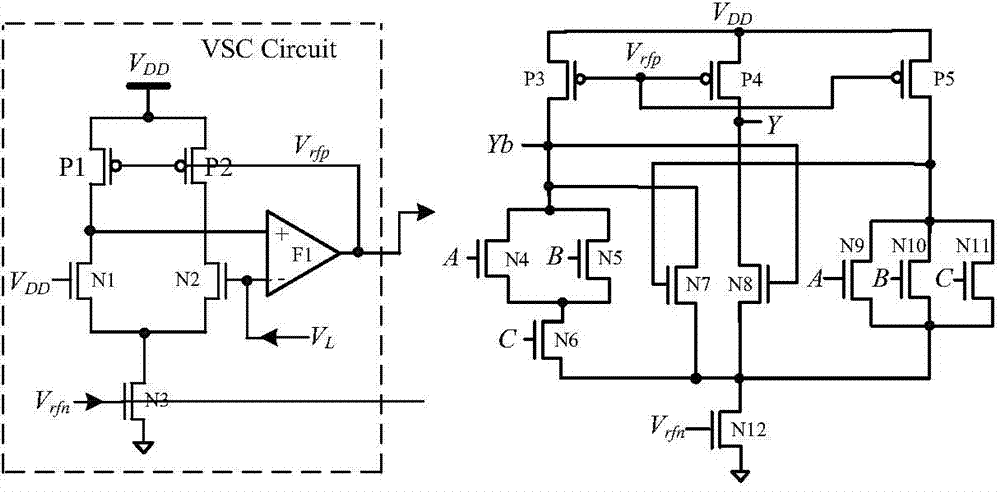

[0028] Embodiment one: if figure 1 with figure 2 As shown, a multi-PDN type current mode RM logic circuit includes a voltage swing control circuit VSC and a composite gate logic circuit, and the voltage swing control circuit VSC includes a first PMOS transistor P1, a second PMOS transistor P2, a first NMOS transistor N1, the second NMOS transistor N2, the third NMOS transistor N3 and the first operational amplifier F1, the source of the first PMOS transistor P1, the substrate of the first PMOS transistor P1, the source of the second PMOS transistor P2, the second PMOS The substrate of the transistor P2 and the gate of the first NMOS transistor N1 are connected to the power supply V DD connected, the substrate of the first NMOS transistor N1, the substrate of the second NMOS transistor N2, the substrate of the third NMOS transistor N3 and the source of the third NMOS transistor N3 are all connected to the ground V SS The drain of the first PMOS transistor P1, the drain of th...

Embodiment 2

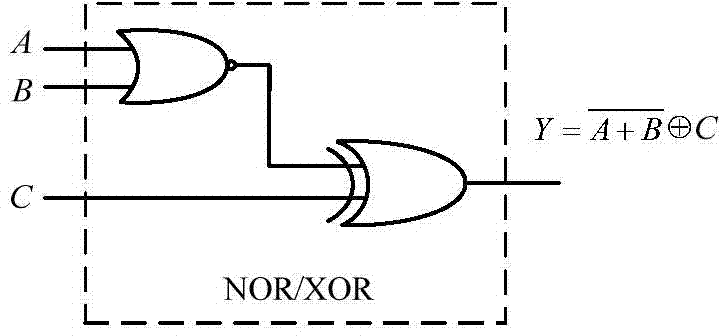

[0049] Embodiment 2: The circuit structure of this embodiment is exactly the same as that of Embodiment 1. By changing the first input logic signal, the second input logic signal and the third input logic signal in the input RM circuit, the following can be obtained: Figure 4 The composite gate composed of the NAND gate and the XOR gate is shown, and its symbol diagram is as follows Figure 5 shown.

[0050] In this embodiment, the first input logic signal connected to the first signal input end of the RM logic circuit is Ab, the second input logic signal connected to the second signal input end of the RM logic circuit is Bb, and the second input logic signal of the RM logic circuit is Bb. The third input logic signal connected to the three-signal input terminal is Cb, wherein, is the inversion signal of A, is the inverse signal of B, Inverted signal for C.

[0051] Analyze the RM logic circuit of the present embodiment, can obtain:

[0052] PDN ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More