Solid-state imaging device, manufacturing method thereof, and electronic device

A solid-state imaging device and logic circuit technology, which is applied in semiconductor/solid-state device manufacturing, radiation control devices, televisions, etc., can solve problems such as deterioration of flash, and achieve the effect of reducing flash components

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

[0048] 2. First Embodiment (Configuration Example of Laminated Back-illuminated Solid-State Imaging Device)

no. 2 example

[0049] 3. Second Embodiment (Configuration Example of Non-Laminated Back-illuminated Solid-State Imaging Device)

[0050] 4. The third embodiment (retaining ring structure with arcuate shape)

[0051] 5. Fourth Embodiment (Trench structure between pixels with arcuate profile)

[0052] 6. Application of electronic equipment

[0053]

[0054]

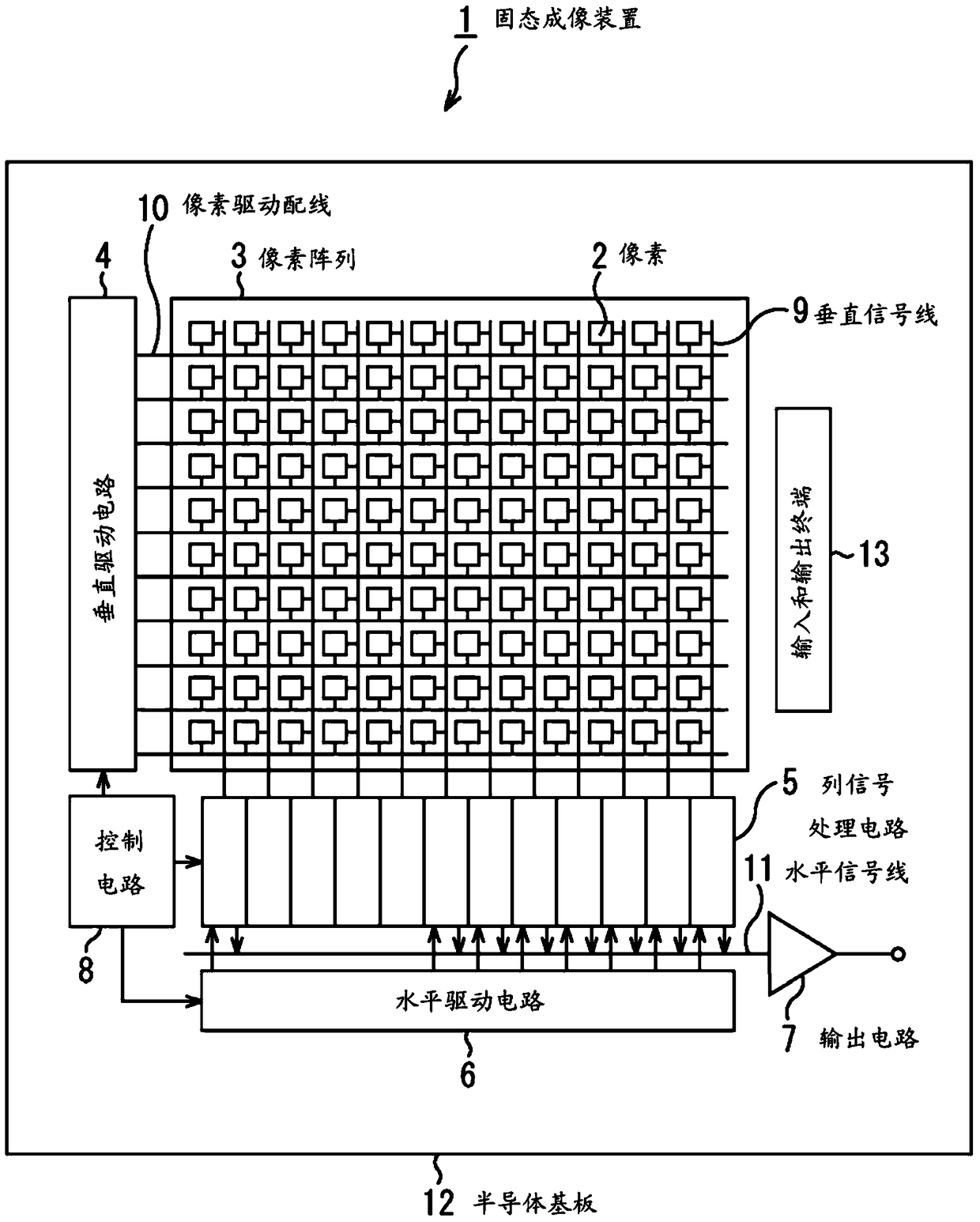

[0055] figure 1 A schematic configuration of a solid-state imaging device according to an embodiment of the present disclosure is shown.

[0056] figure 1 The illustrated solid-state imaging device 1 includes a semiconductor substrate 12 using silicon (Si) as a semiconductor, a pixel array 3 in which pixels 2 are arranged in a two-dimensional array, and peripheral circuits. The peripheral circuit includes a vertical drive circuit 4 , a column signal processing circuit 5 , a horizontal drive circuit 6 , an output circuit 7 and a control circuit 8 .

[0057] Each pixel 2 includes a photodiode as a photoelectric conversion element a...

no. 3 example

[0205]

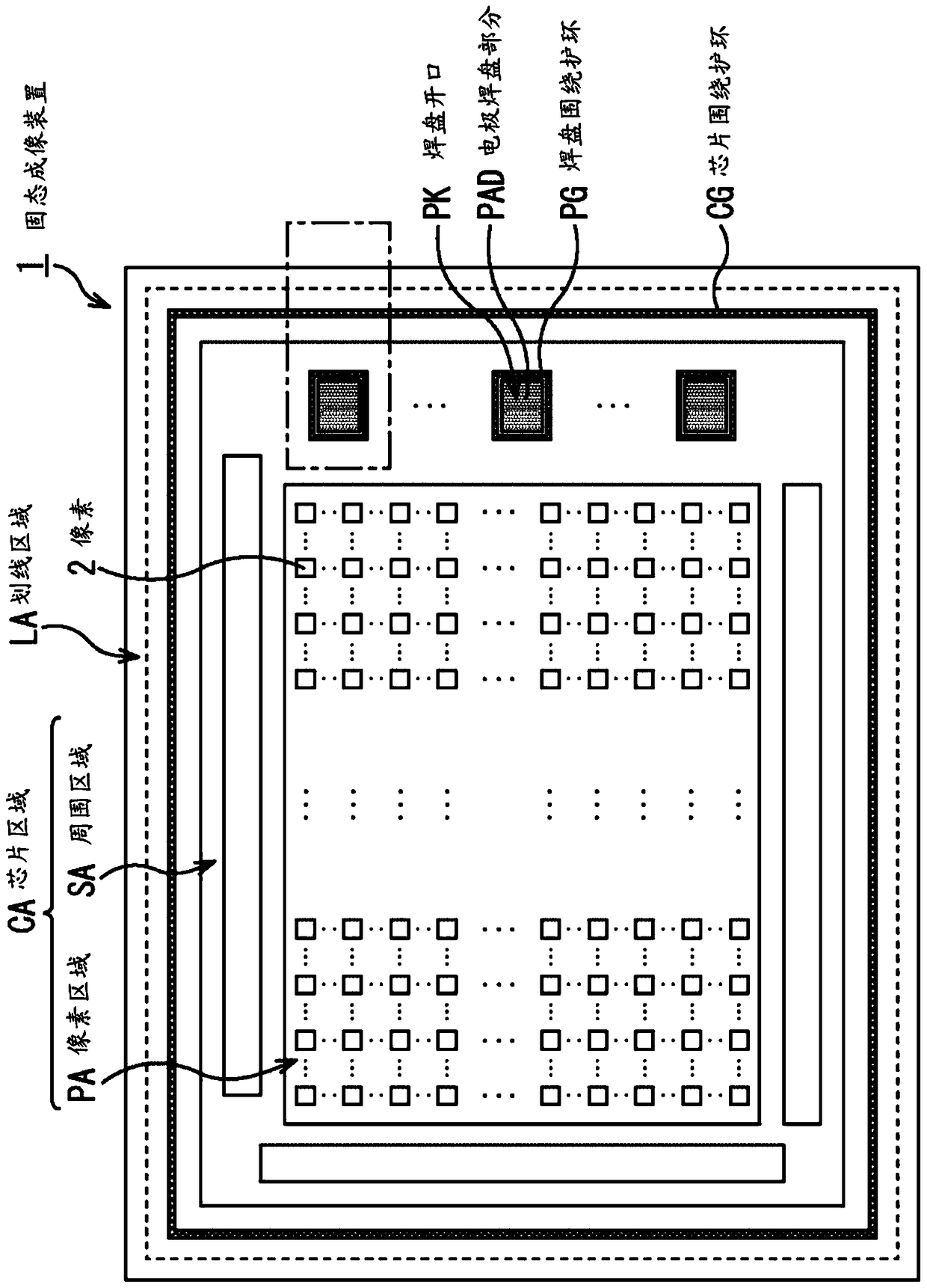

[0206] In the above-described embodiments, each of the pad surrounding guard ring PG and the chip surrounding guard ring CG has a forward tapered shape in which the top diameter on the light incident surface side is larger than the bottom diameter on the bottom. Other structures of the pad surrounding guard ring PG and the chip surrounding guard ring CG will be described below.

[0207] The pad surrounding guard ring PG and the chip surrounding guard ring CG may be formed by forming an opening 202 having a high aspect ratio to a semiconductor substrate 201 by a dry etching process and spin-coating a coating material 203 by a spin coating method to fill the opening 202 with the coating material 203. ,Such as Figure 21 shown.

[0208] However, depending on the shape of the opening 202, the coating material 203 on the upper part of the opening 202 may spill due to the centrifugal force of the rotation, as Figure 21 shown. Once the coating material 203 spills out a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More