Shallow-trench isolation structure and forming method thereof

A technology of isolation structure and shallow trench, which is used in the manufacture of electrical components, electrical solid-state devices, semiconductor/solid-state devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] As mentioned in the background art, the isolation effect of the existing shallow trench isolation structure needs to be further improved.

[0030] Research has found that the shallow trench isolation structure formed in the prior art will generate leakage when the chip has a relatively high operating voltage, resulting in reduced circuit reliability and chip failure.

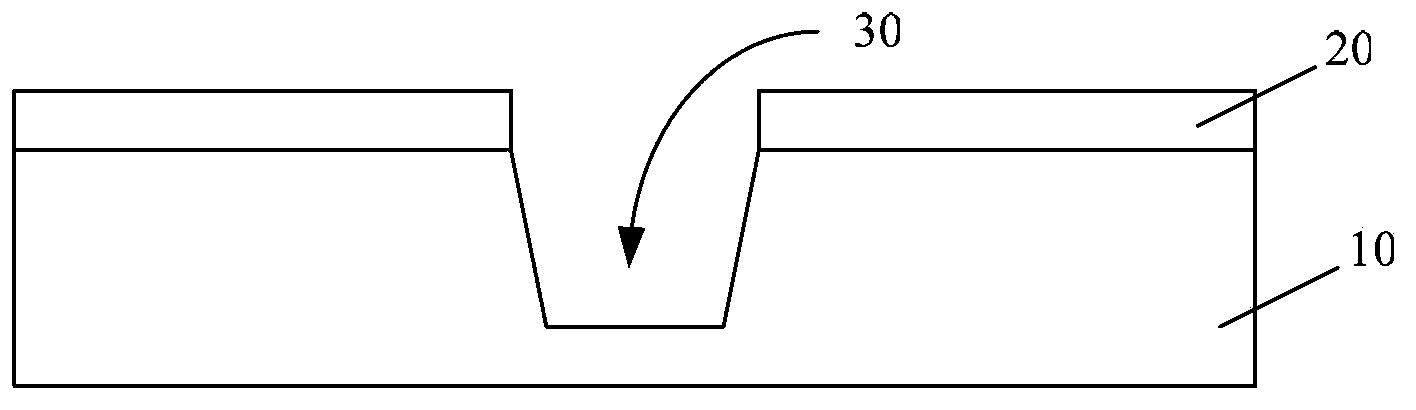

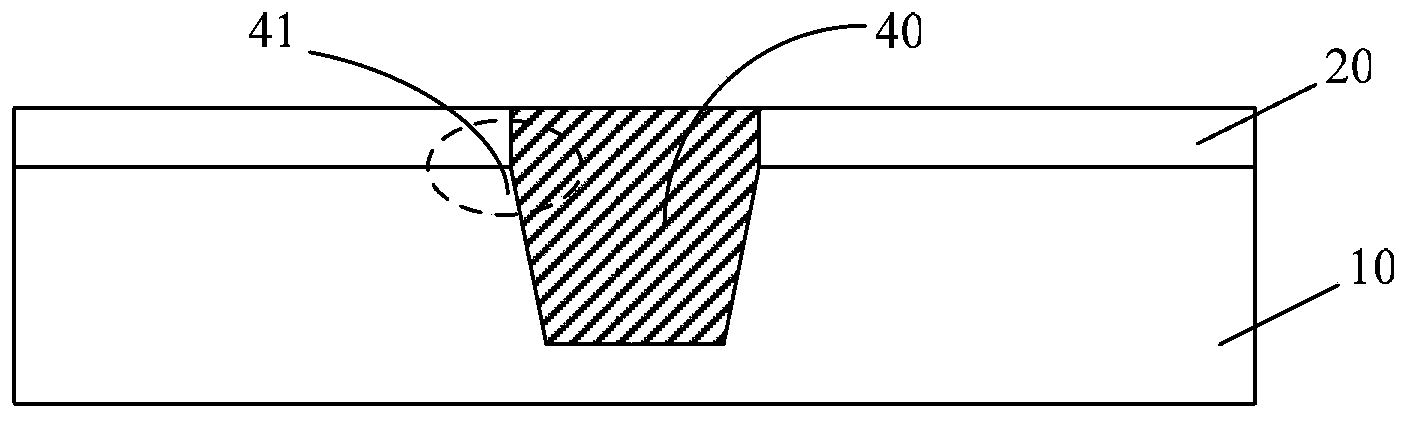

[0031] Further, research has found that under high-voltage environments, leakage is likely to occur mainly at the top corners where the semiconductor substrate and the shallow trench isolation structure are connected. Please refer to figure 2 , the angle of the vertex 41 where the semiconductor substrate 10 meets the shallow trench isolation structure 40 is relatively sharp, and in the case of a high voltage, the electric field density at the position of the vertex is relatively large, and electric leakage etc. are likely to occur phenomenon, and because the angle of the vertex 41 is relatively sharp an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More