Electrostatic discharge protection method of chip with multiple power systems and multiple package types

A technology of power supply system and chip, which is applied in the direction of circuits, electrical components, electric solid devices, etc., can solve the problems of high substrate potential, damage of internal devices, increase of chip area, etc., and achieve the effect of small chip area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

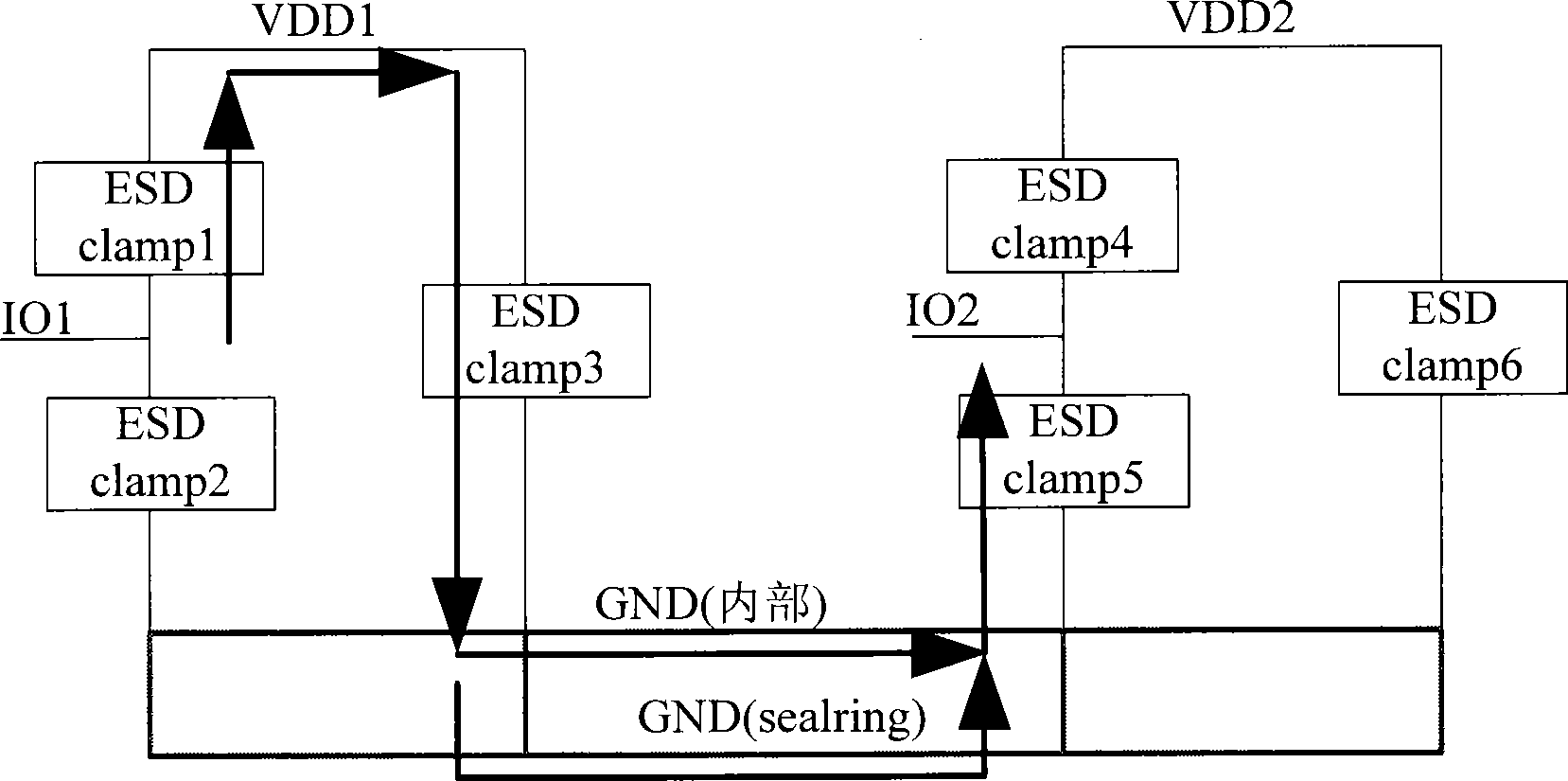

[0019] Such as figure 1 As shown, the ESD current of IO1 pin flows to VDD1 through ESD clamp1, flows to GND inside the chip through ESD clamp3, and flows to sealring GND at the same time, GND inside the chip and sealring GND form a parallel path, and reaches the GND node of IO2. Foot discharge.

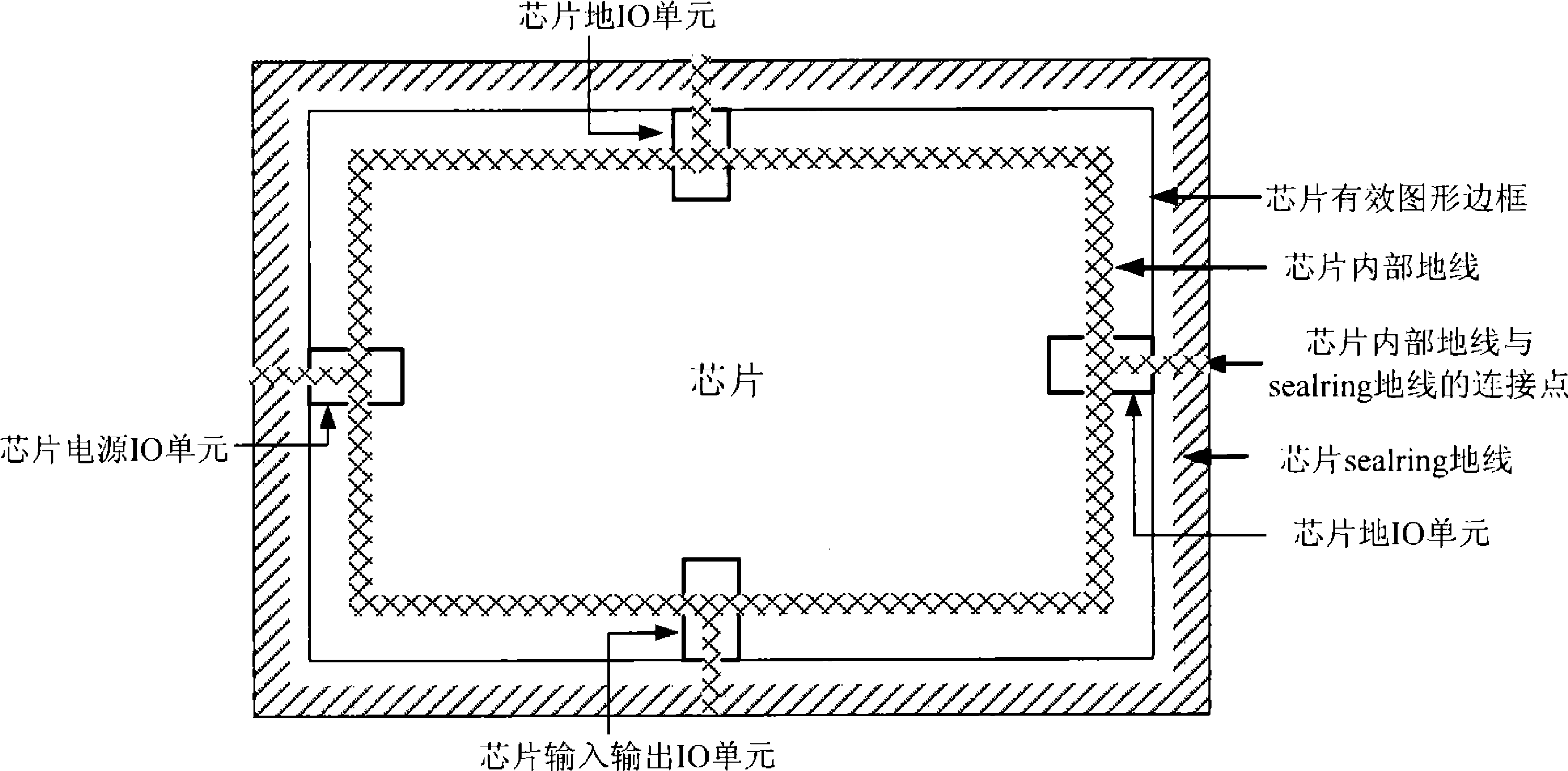

[0020] Such as figure 2 As shown, taking a chip with an area of 4mm*4mm as an example, the internal ground wire of the chip is metal2, the width is 40um, and it is closed to form a ring in the chip; the ground wire of the seal ring outside the chip is metal1~metal4, and the width is 10um. As shown in the figure, the black line is the effective graphic frame of the chip; the slanted line is the sealring of the outer ring of the chip; the grid line is the annular ground wire inside the chip and the ground wire connected to the sealring. The connection between each IO and the sealring can be connected according to the number of metal layers and the metal width actually allowed by th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More