Method for verifying scrambled address of chip storage unit

A technology of storage unit and verification method, applied in static memory, instrument, etc., can solve the problems of low success rate, long analysis cycle, low efficiency, etc., and achieve the effect of improving the success rate and reducing the sample preparation cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

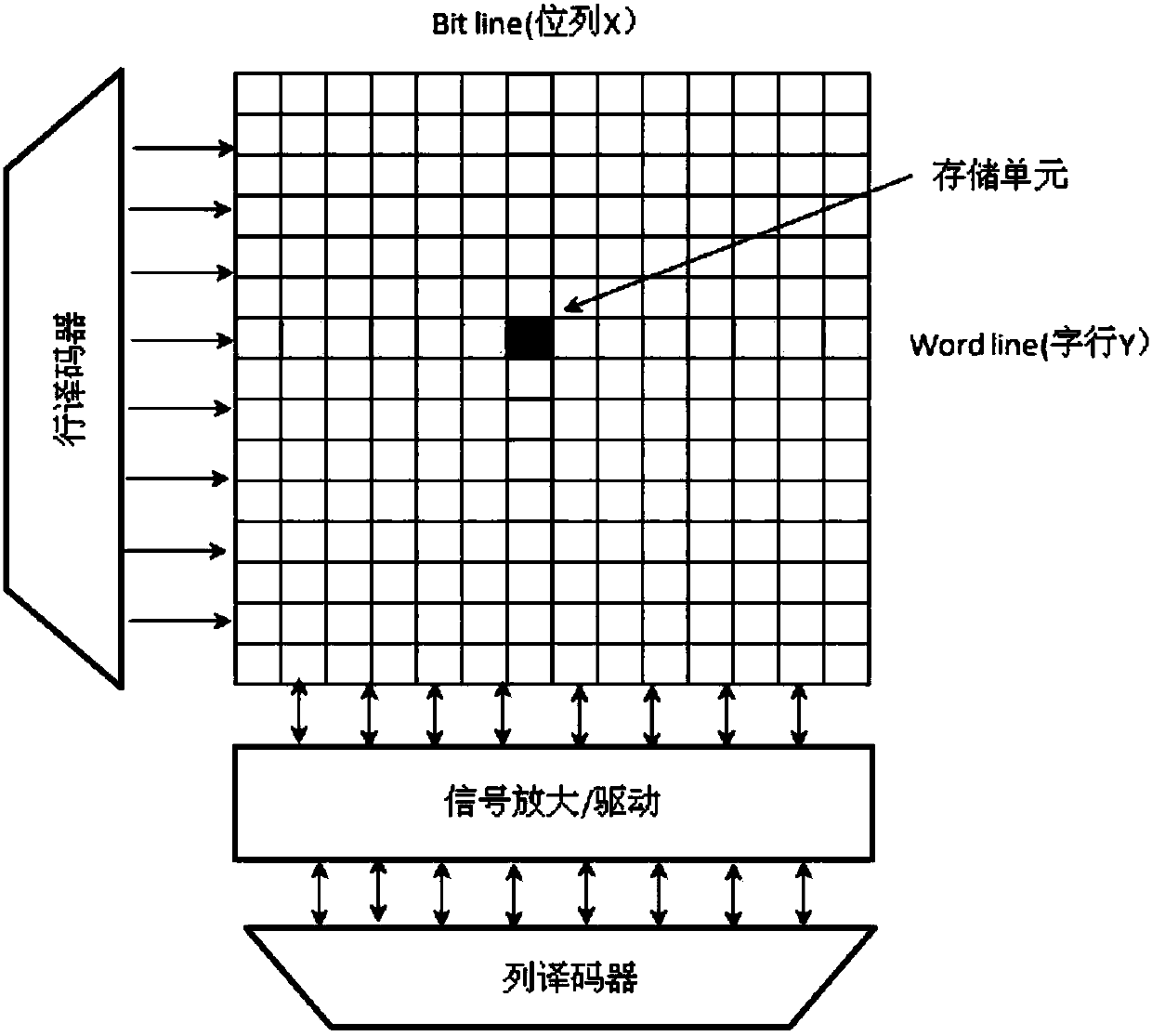

[0032] The method for verifying the scrambled address of the chip storage unit of the present invention includes the following steps:

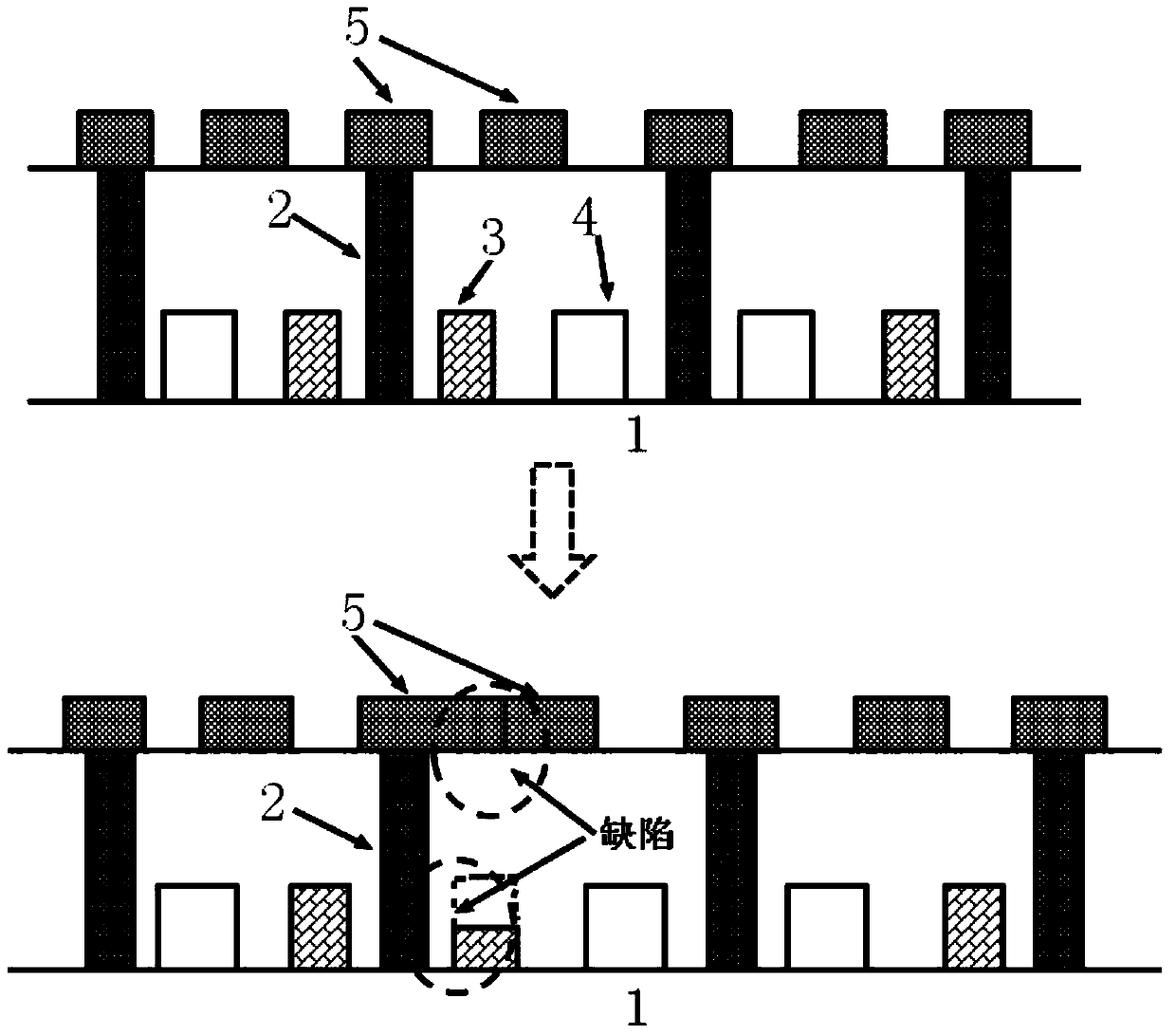

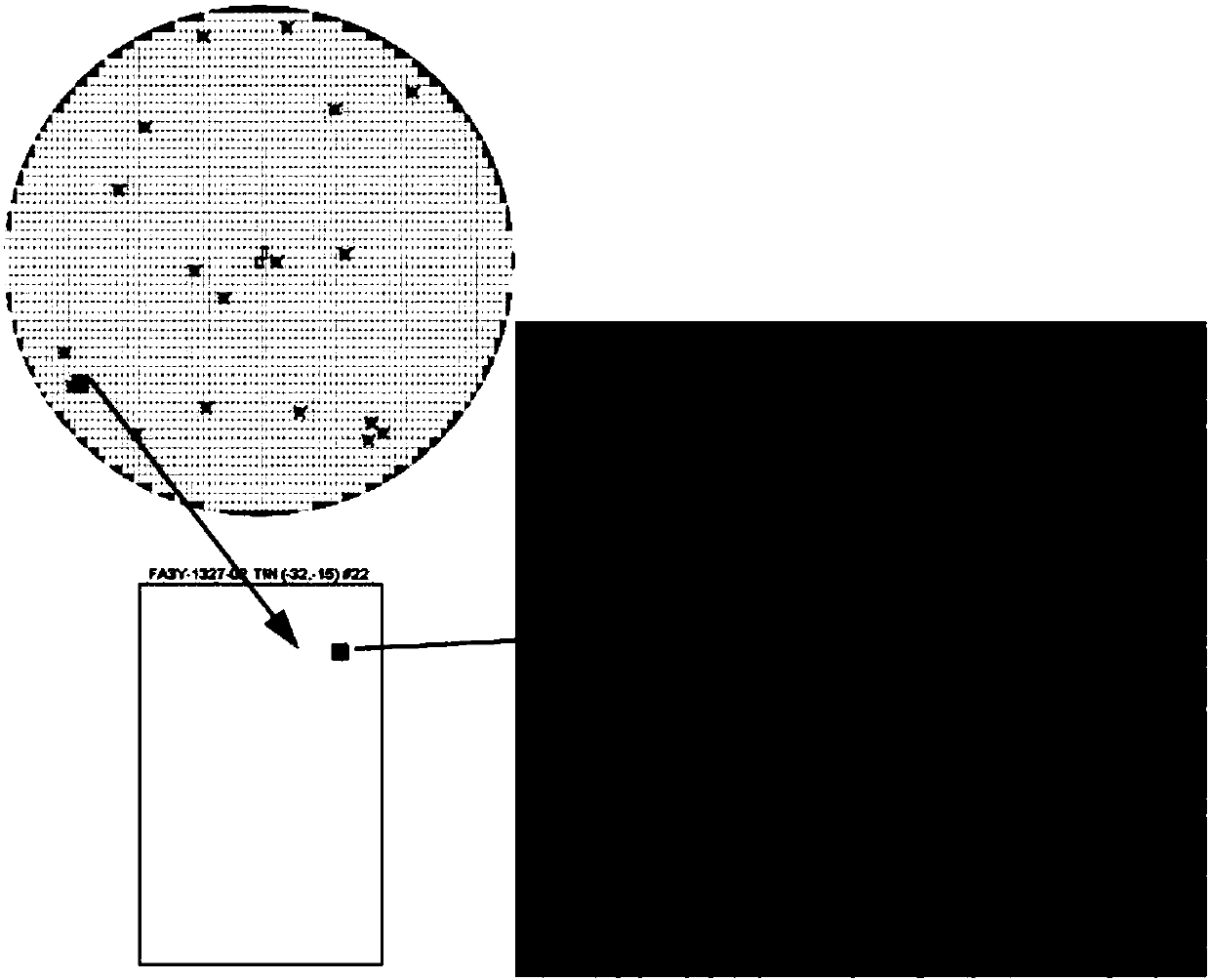

[0033] In the first step, in the process of mass production of the chip, the failure defect inside the memory is captured in the online defect detection.

[0034] Use the fatal flaws captured in the online inspection of the target product to perform post-scrambling address verification. On-line (silicon wafer production process) defect detection is a necessary step in the chip manufacturing process. The purpose is to: firstly catch the abnormality of the equipment or process in time to prevent the abnormal expansion; secondly, if there is a possibility of rework, rework in time to save losses . Utilizing the irreparable fatal defects that fall in the memory area, these fatal defects can be clarified in the storage area when they are caught, which is convenient for recording and later use.

[0035] In addition, or using a focused ion beam to bombard...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More