Planar gate IGBT with low-reverse transfer capacitance and anti-latch-up structure and manufacturing method of planar gate IGBT

A technology of reverse transmission and planar gate, which is applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve the problem of ineffective reduction of hole current flow path resistance, easy occurrence of LC oscillation, and insufficient P well concentration, etc. problem, achieve the effect of reducing the risk of LC oscillation, suppressing latch-up, and reducing the reverse transmission capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings.

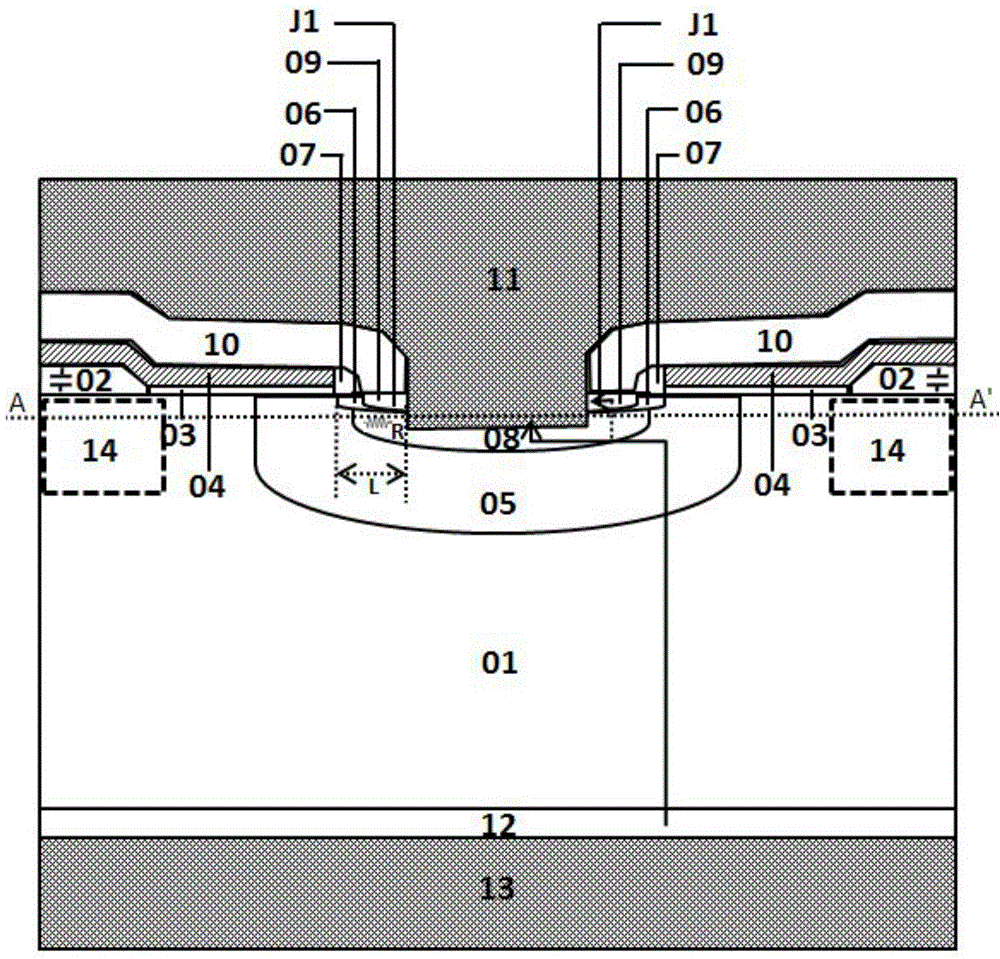

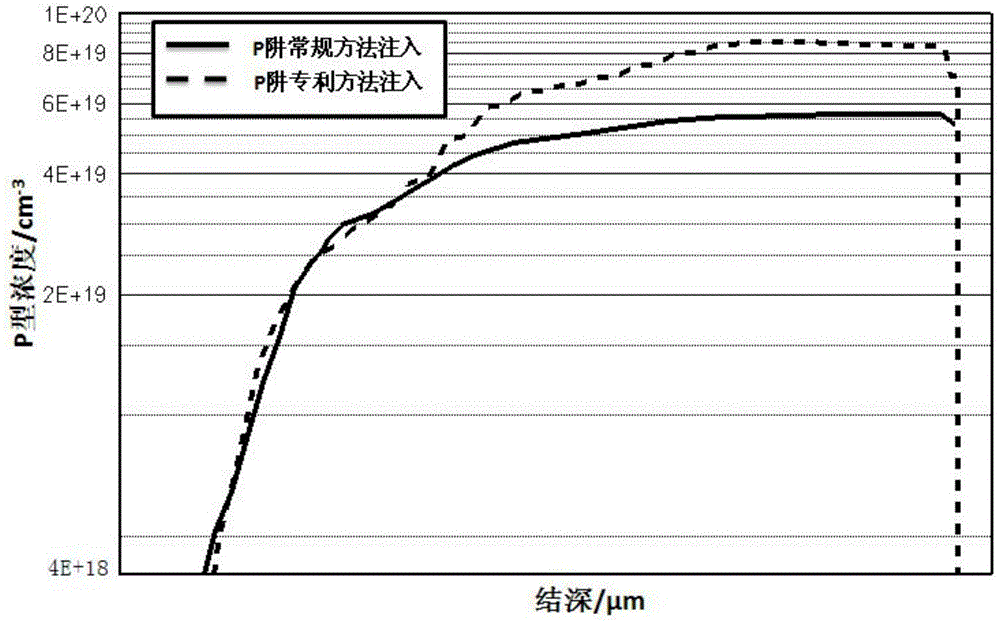

[0034]The present invention provides a planar gate IGBT with a low reverse transmission capacitance anti-latch-up structure. The planar gate IGBT includes a substrate 01, a field oxide layer 02 and a gate oxide layer 03 on the surface of the substrate, deposited on the gate oxide layer The polysilicon gate 04 on 03 and the P well region 05 between the gate oxide layer 03 and the substrate 01, the N well region 06 located on the surface of the P well region 05, and the P+ type in the P well region 05 are sequentially arranged from bottom to top The doped region 08 and the N+ type doped region 09, the JFET region is located between two P well regions 05; the P well region 05 is formed by multiple implantation and push junction processes, and the total implantation dose is between 6E13-8E13, A field oxide layer 02 is grown ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More