Breakdown-preventing SOI folding gate insulated tunneling bipolar transistor and making method thereof

A bipolar transistor and gate insulation technology, which is applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as the inability to substantially improve the tunneling probability of silicon materials, increase in static power consumption, and increase process difficulty.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

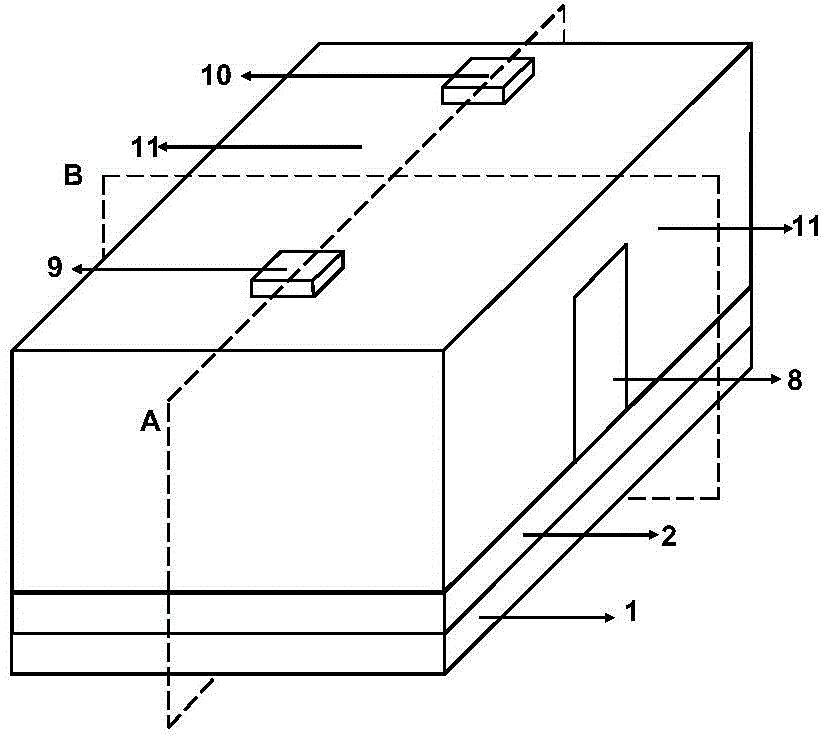

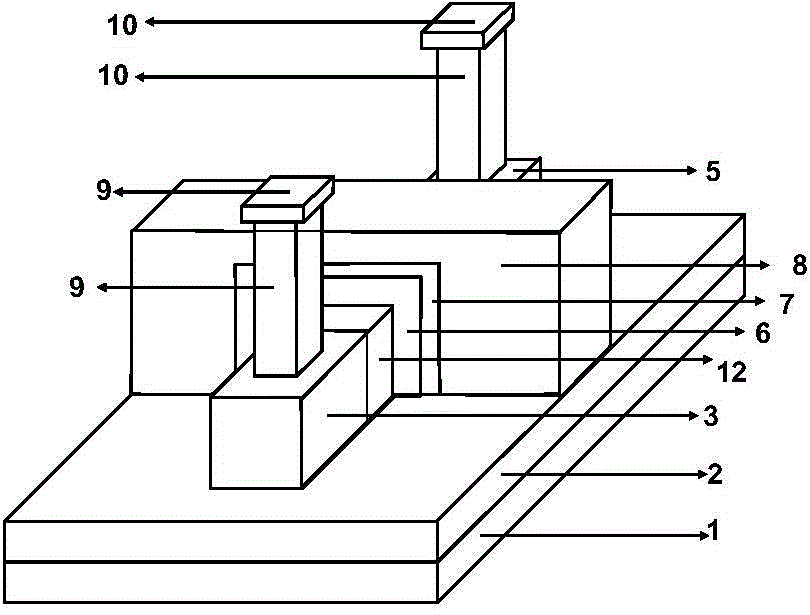

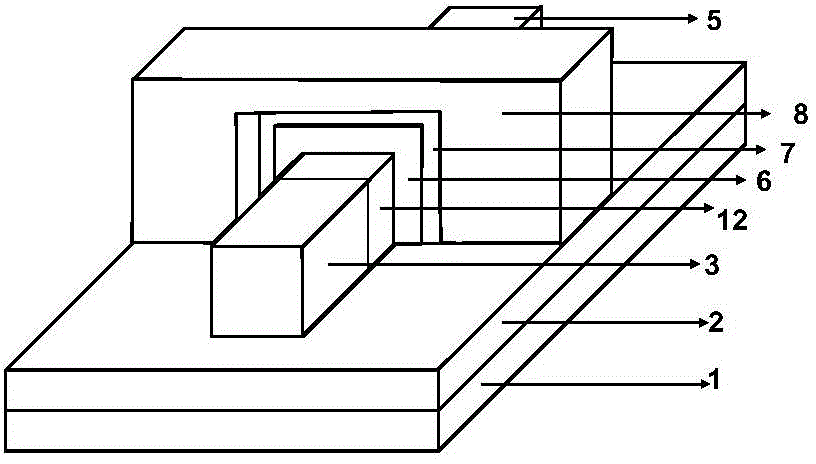

[0084] Below in conjunction with accompanying drawing, the present invention will be further described: figure 1 It is a schematic diagram of a three-dimensional structure of an anti-breakdown SOI folded gate insulated tunneling bipolar transistor formed on an SOI substrate in the present invention; figure 2 A schematic diagram of a three-dimensional structure after peeling off the blocking insulating layer 11 for the anti-breakdown SOI folded gate insulated tunneling bipolar transistor of the present invention; image 3 A schematic diagram of a three-dimensional structure after peeling off the emitter 9, the collector 10 and the blocking insulating layer 11 for the anti-breakdown SOI folded gate insulated tunneling bipolar transistor of the present invention; Figure 4 A schematic diagram of a three-dimensional structure after peeling off the emitter 9, the collector 10, the blocking insulating layer 11 and the folded gate electrode 8 for the anti-breakdown SOI folded gate i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More