Soi substrate bidirectional breakdown protection double gate insulation tunneling enhanced transistor and manufacturing method

A technology of breakdown protection and gate insulation, applied in SOI substrate bidirectional breakdown protection double-gate insulation tunneling enhanced transistor and its manufacturing field, can solve the problem of increasing tunneling probability transfer characteristics, increasing static power consumption, tunneling field Problems such as limited improvement of transfer characteristics of effect transistors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0100] Below in conjunction with accompanying drawing, the present invention will be further described:

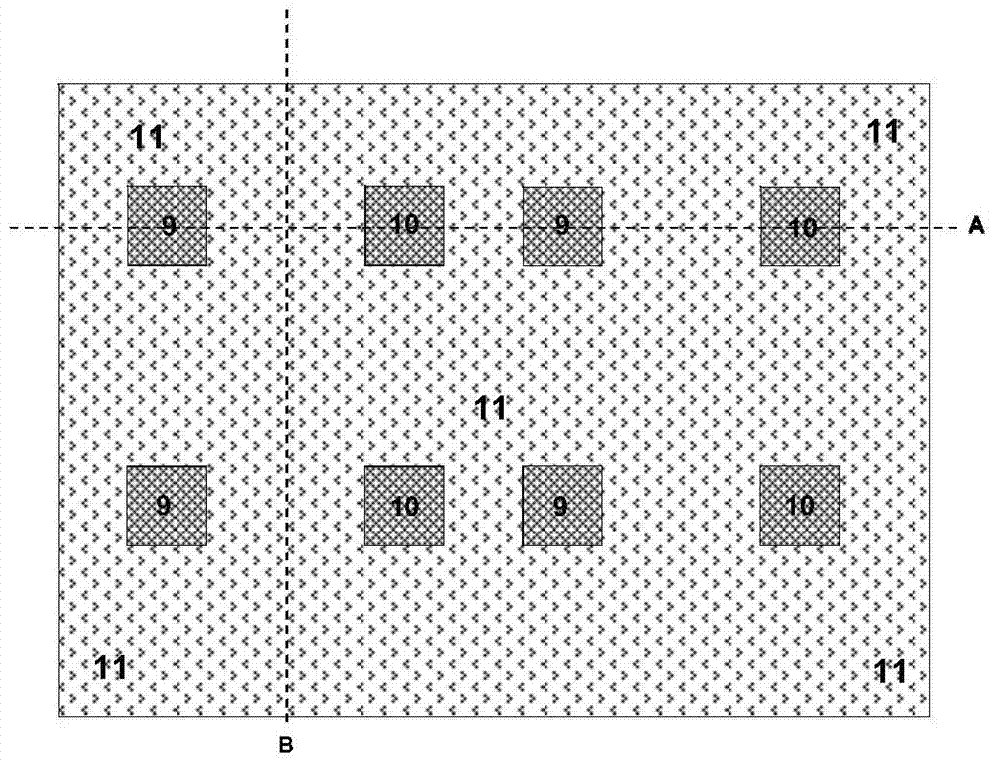

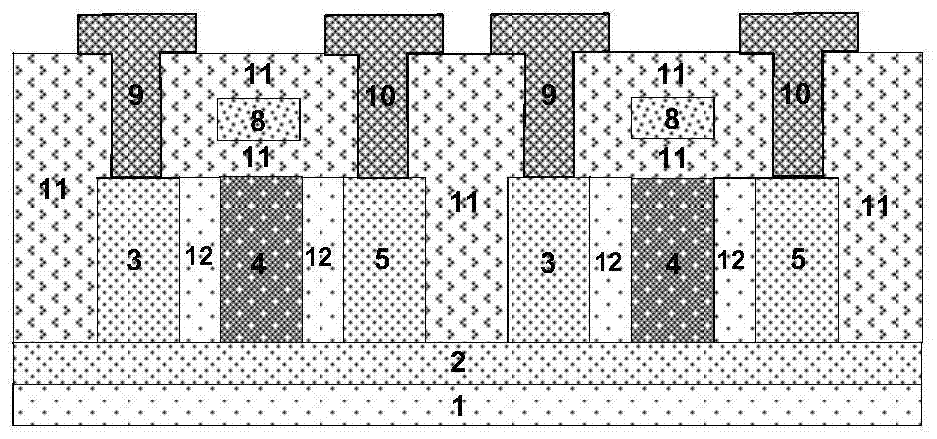

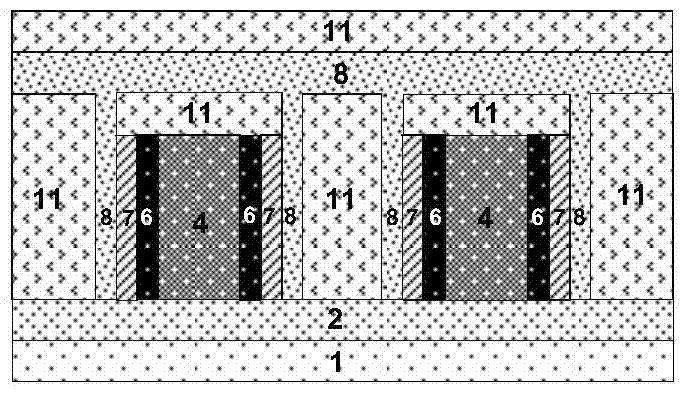

[0101] Such as figure 1 It is a top view schematic diagram of a two-dimensional structure of an SOI substrate bidirectional breakdown protection double-gate insulation tunneling enhancement transistor of the present invention; figure 2 yes figure 1 Schematic diagram of the cross-section obtained by cutting along the tangent line A; image 3 yes figure 1Schematic cross-sectional view obtained by cutting along tangent line B; specifically includes single crystal silicon substrate 1; wafer insulating layer 2; emitter region 3; base region 4; collector region 5; conductive layer 6; tunneling insulating layer 7; gate electrode 8 ; Emitter 9; Collector 10; Blocking insulating layer 11;

[0102] SOI substrate bidirectional breakdown protection dual-gate insulation tunneling enhanced transistor, using an SOI wafer including a single crystal silicon substrate 1 and a wafer ins...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More