Low subthreshold oscillation range and high voltage withstanding insulated gate tunneling transistor and preparing method thereof

A sub-threshold swing, tunneling transistor technology, used in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problem of increasing production costs, not substantially improving the tunneling probability of silicon materials, and increasing process difficulty. and other problems, to achieve the effect of good forward withstand voltage and reverse withstand voltage characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] Below in conjunction with accompanying drawing, the present invention will be further described:

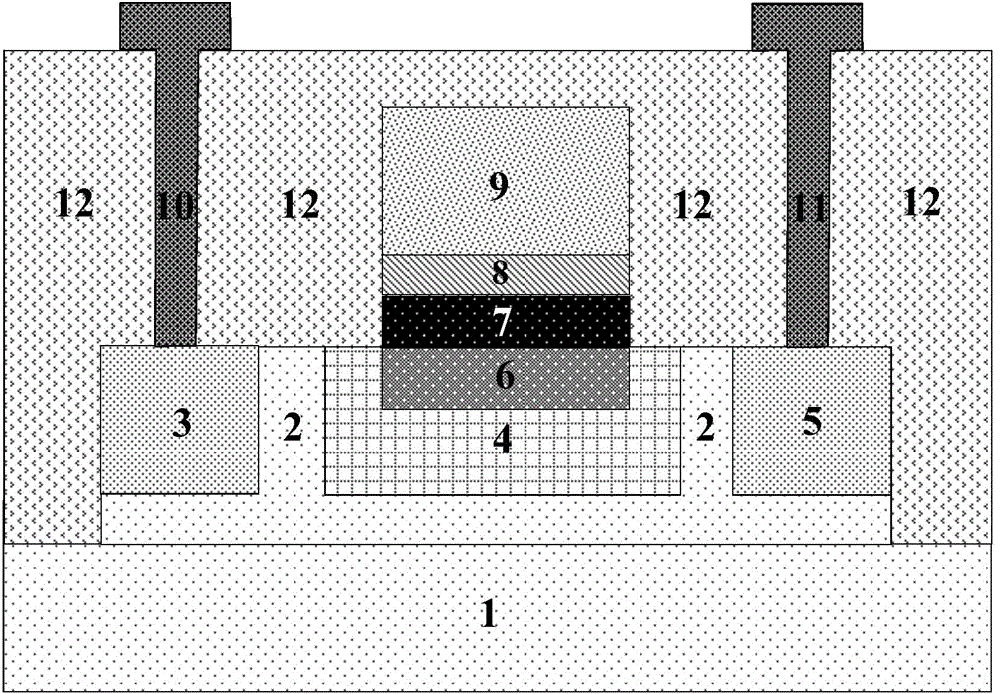

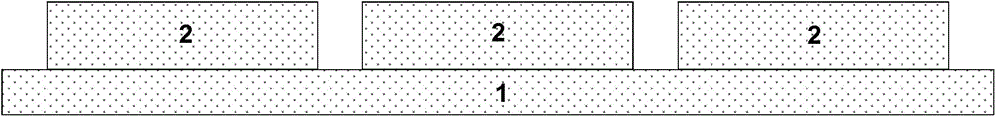

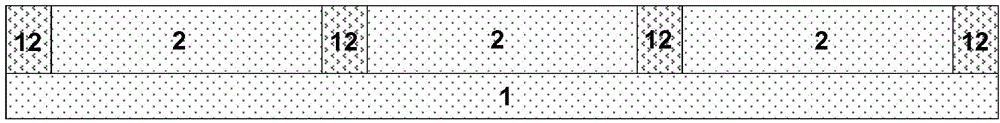

[0046] Such as figure 1 It is a schematic diagram of a two-dimensional structure of a low subthreshold swing high withstand voltage insulated gate tunneling transistor formed on a bulk silicon substrate in the present invention; it specifically includes a single crystal silicon substrate 1; a withstand voltage layer 2; an emitter region 3; a moderately doped Impurity base region 4; collector region 5; heavily doped base region 6; conductive layer 7; tunnel insulating layer 8; gate electrode 9; emitter 10; collector 11; blocking insulating layer 12.

[0047] Low sub-threshold swing high withstand voltage insulated gate tunneling transistor, the substrate 1 uses a single crystal silicon wafer as the substrate for forming the device, or uses an SOI wafer as the substrate for forming the device; a withstand voltage layer 2 is formed above the substrate The emitter region 3, t...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More