Method for confirming position alignment in wafer test

A wafer testing and wafer technology, which is applied in the field of confirmation of position alignment in wafer testing, can solve the problems of wasting wafer testing time, affecting product quality, and wrong wafer map position correspondence, and avoiding position The effect of shifting alignment, preventing position alignment errors, and saving test time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

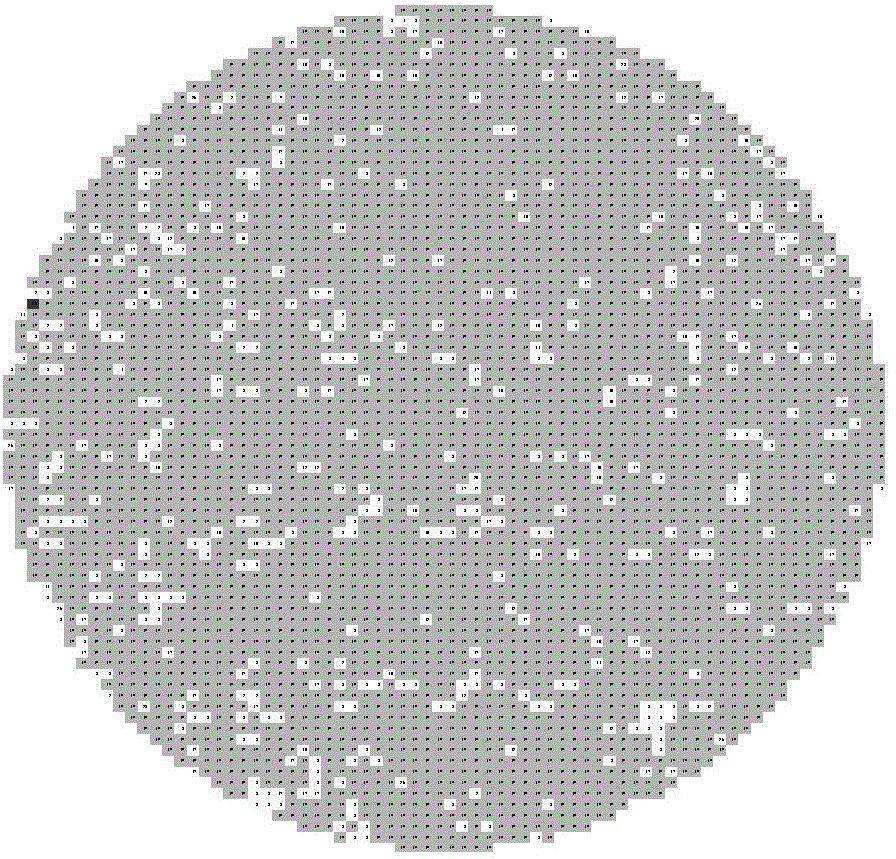

[0019] The method for confirming the position alignment in the wafer test of the present invention is to perform more than two test processes on the wafer containing the NVM IP (non-volatile memory Intellectual Property) chip Alignment confirmation method, its steps include:

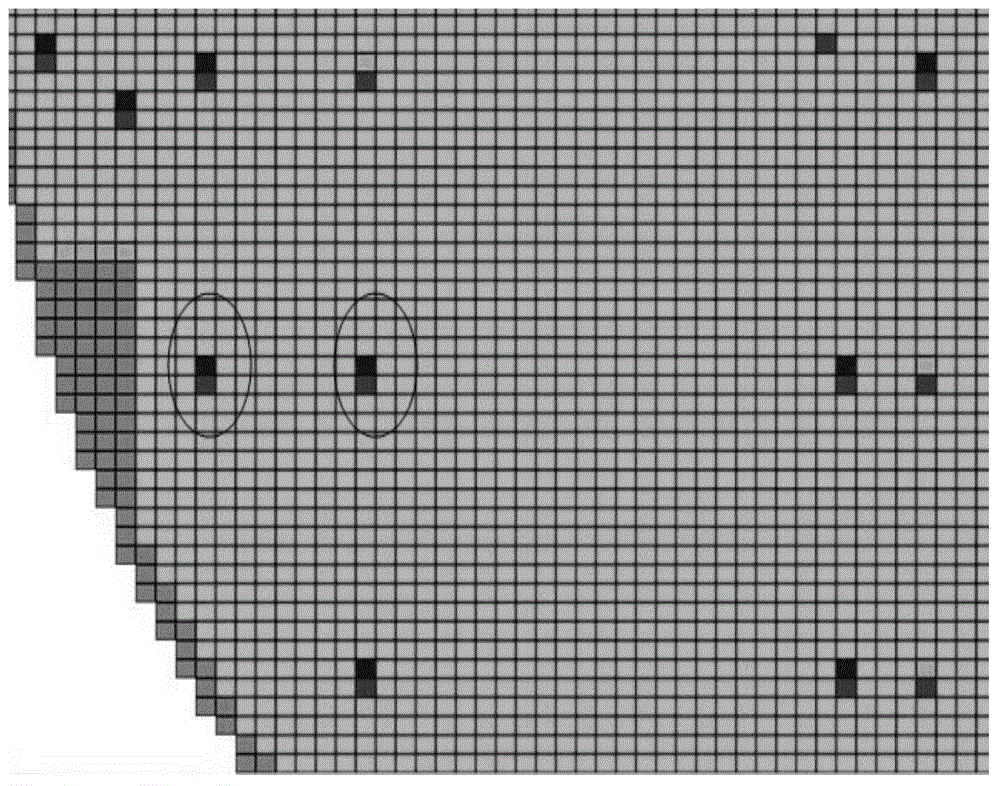

[0020] 1) First specify that the address Z in the memory area of the chip is the location where the mapped address is stored. Address Z contains at least one byte; the chip also contains the chip status flag bit, which can be composed of one byte;

[0021] If the chip with the address Z area is normal, you can write information such as 0X5A in the flag bit. According to the needs, there is at least one target chip Tai, where "i" can be 1, 2, 3 and above. If there is one time, it is recorded as Ta1; if there are two, it is recorded as Ta1, Ta2; and so on.

[0022] In order to improve the test efficiency, Tai position confirms that the target chip selection is often in the starting area of the wafer chip te...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More