FPGA-based (Field Programmable Gate Array-based) IO (Input/Output) bus device with automatic recognition function

A bus device and self-identification technology, applied in the bus field, can solve problems such as unreliable connection between boards and backplanes, inability to plug in other types of boards, wrongly plugging in wrong power boards, etc., to save query or interruption time, Easy to program processing, easy to update the effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

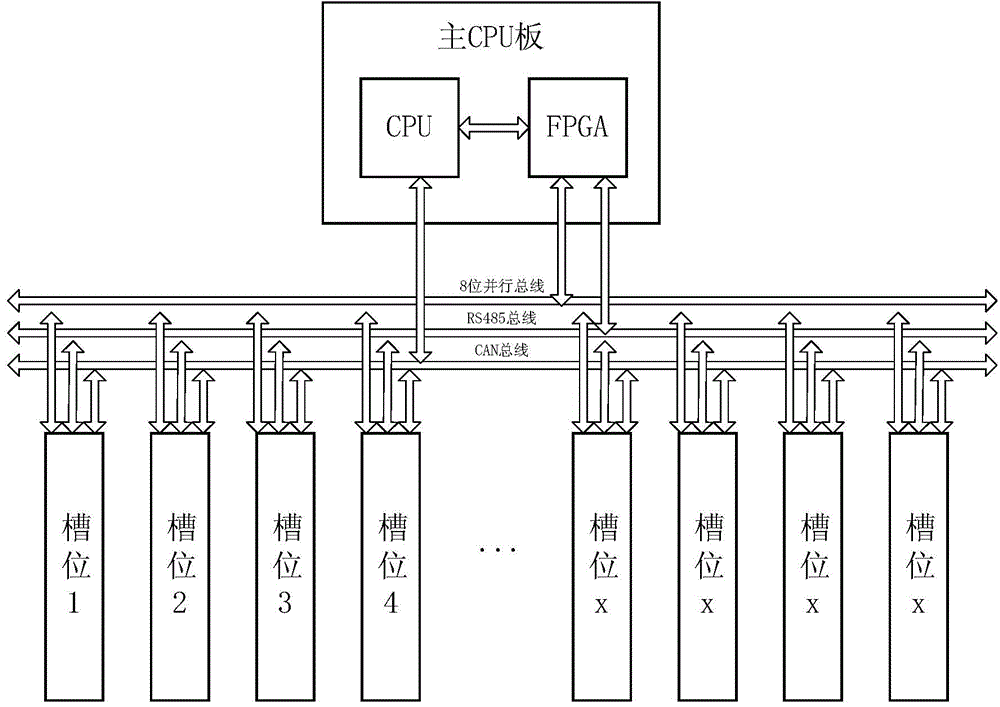

[0028] Such as figure 1 As shown, the present embodiment includes a main CPU board, slots for plug-in boards, three types of bus parallel bus, serial bus and field bus, and the main CPU board includes a CPU module and an FPGA module. These three buses are all connected to the slots. Each slot can use these three buses to send data. Except that the CAN bus is directly connected to the slot by the CPU, the rest are connected to the slot by the FPGA to manage the parallel bus and the RS485 bus in a unified manner.

[0029] Each slot has its own differences, and each slot has a CS chip select line connected to the FPGA, so that the FPGA can time-division multiplex the parallel bus.

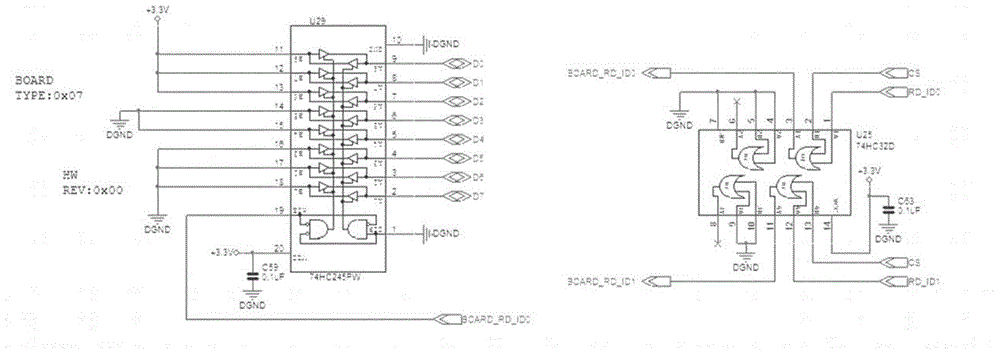

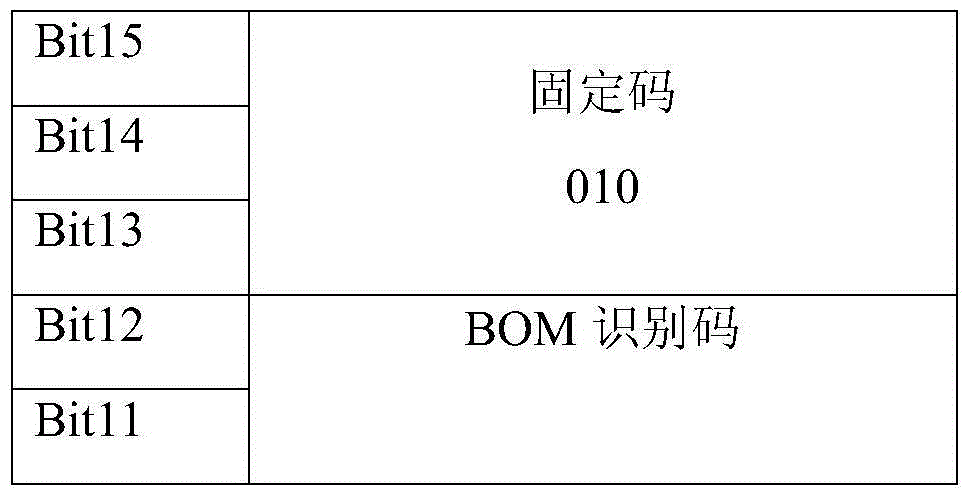

[0030] The parallel bus is composed of CS chip select line, 2 RD_ID, 4 RD, 4 WR and 8 data lines, as shown in Table 1.

[0031] Table 1 Definition table of specific terminals of the bus

[0032]

[0033] The state machine of FPGA reads and writes data through chip select, read and wri...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More