Semiconductor assembly and manufacturing method thereof

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as manufacturing yield reduction and circuit short circuit

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] The following descriptions of the various embodiments refer to the accompanying drawings to illustrate specific embodiments in which the present invention can be practiced. Furthermore, the directional terms mentioned in the present invention are, for example, up, down, top, bottom, front, back, left, right, inside, outside, side, surrounding, central, horizontal, transverse, vertical, longitudinal, axial, The radial direction, the uppermost layer or the lowermost layer, etc. are only directions referring to the attached drawings. Therefore, the directional terms used are used to illustrate and understand the present invention, but not to limit the present invention.

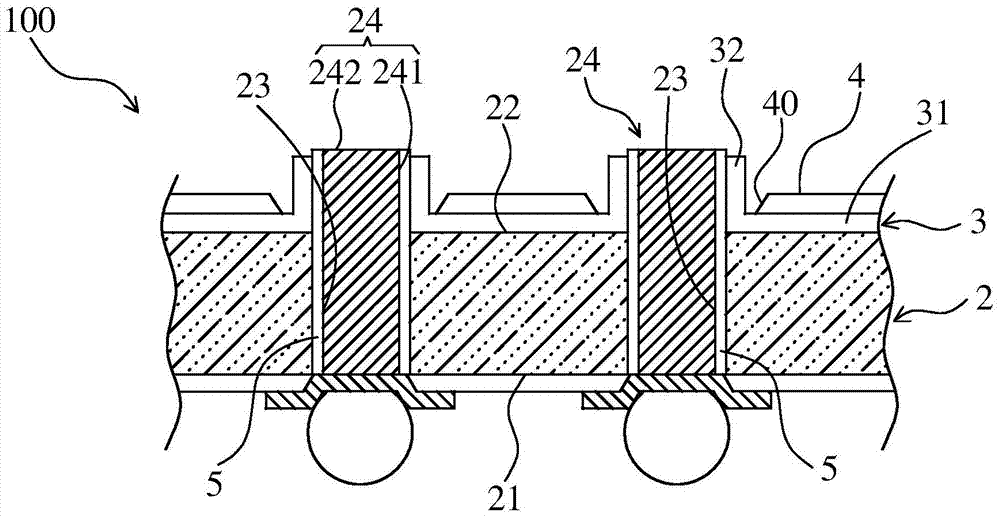

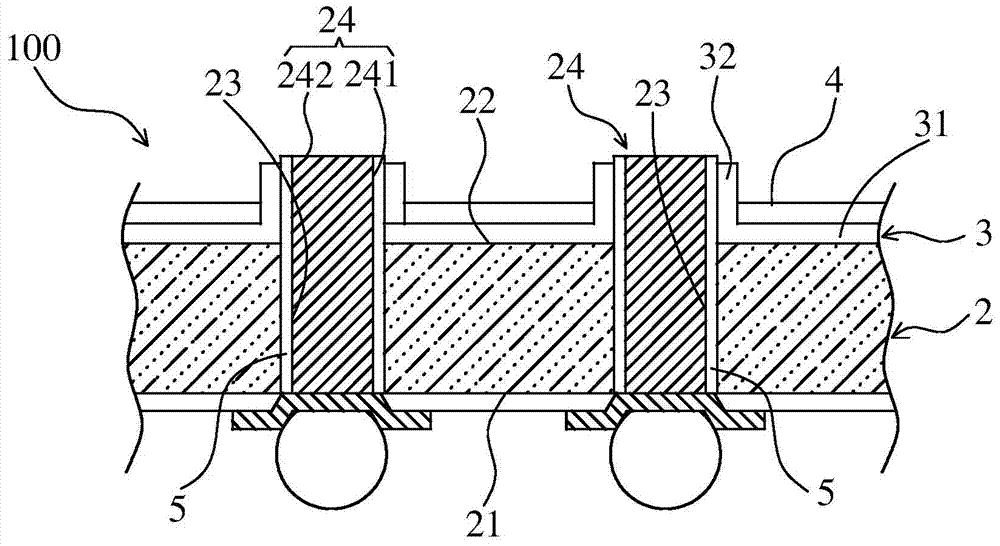

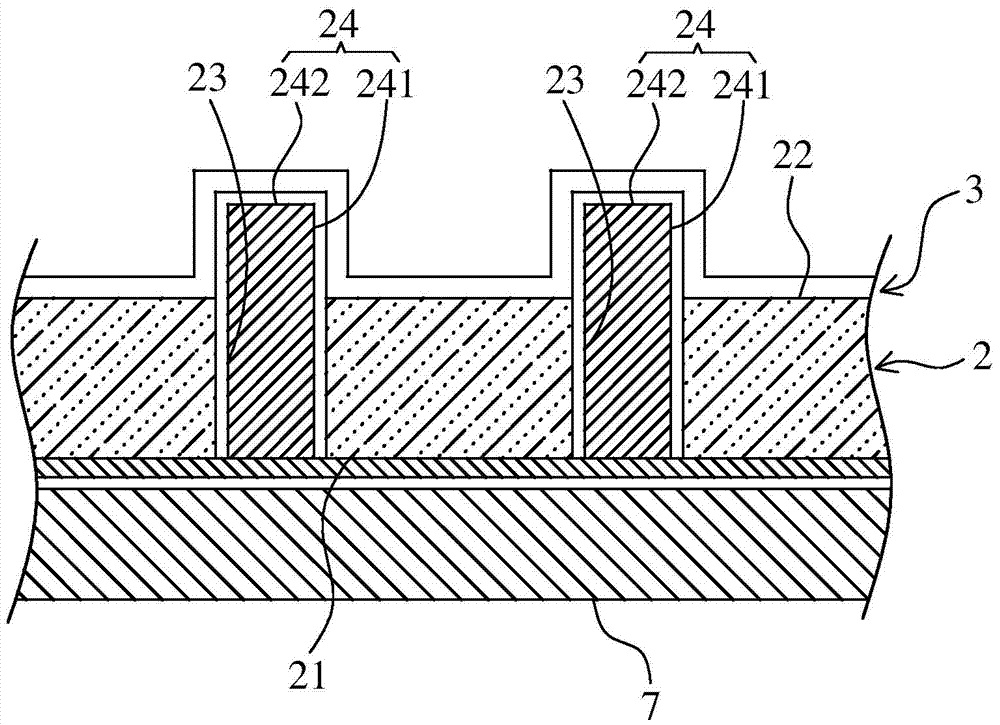

[0017] Please refer to figure 1 As shown, the semiconductor device 100 according to an embodiment of the present invention mainly includes a silicon substrate 2 , a first passivation layer 3 and a second passivation layer 4 . The present invention will describe in detail the detailed structure, assembly...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More