Array substrate, manufacturing method of array substrate and display device

A technology of an array substrate and a manufacturing method, which is applied in the display field and can solve problems such as short circuit of signal lines and gate lines.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0054] This embodiment provides a method for manufacturing an array substrate, including the following steps:

[0055] Coating photoresist on the insulating layer covering the conductive pattern or semiconductor pattern;

[0056]Exposure to at least form a photoresist partially reserved area and a photoresist completely removed area, wherein the photoresist partially reserved area corresponds to the area where the first via hole is formed, and the photoresist completely removed area corresponds to the area where the second via hole is formed Specifically, the thickness of the photoresist in the photoresist partially reserved region is smaller than the thickness of the photoresist in the photoresist completely reserved region, and the thickness of the photoresist in the photoresist partially reserved region is greater than that of the photoresist completely removed The thickness of the photoresist in the area;

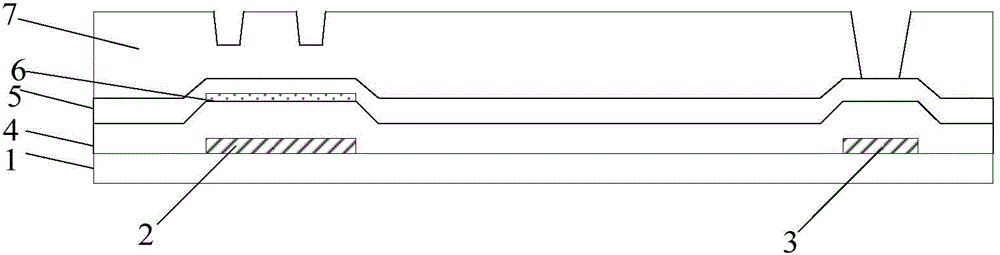

[0057] Etching, at least partially removing the insulating layer ...

Embodiment 2

[0085] Taking the array substrate as an oxide thin film transistor array substrate as an example, the fabrication method of the array substrate of this embodiment will be described in detail below with reference to the accompanying drawings. Apparently, the described embodiments are only some of the embodiments of the present invention, but not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

[0086] It should be noted that the terms "upper", "lower", "inner" and "outer" in the embodiments of the present invention are only used to describe the embodiments of the present invention with reference to the drawings, and are not used as limiting terms.

[0087] The manufacturing method of the present embodiment comprises the following steps:

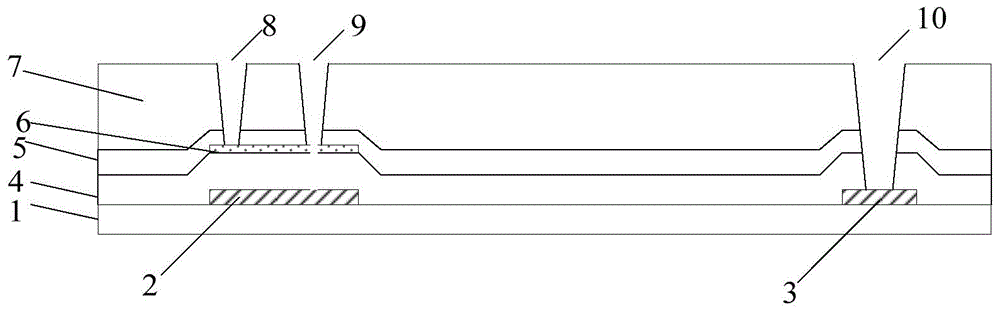

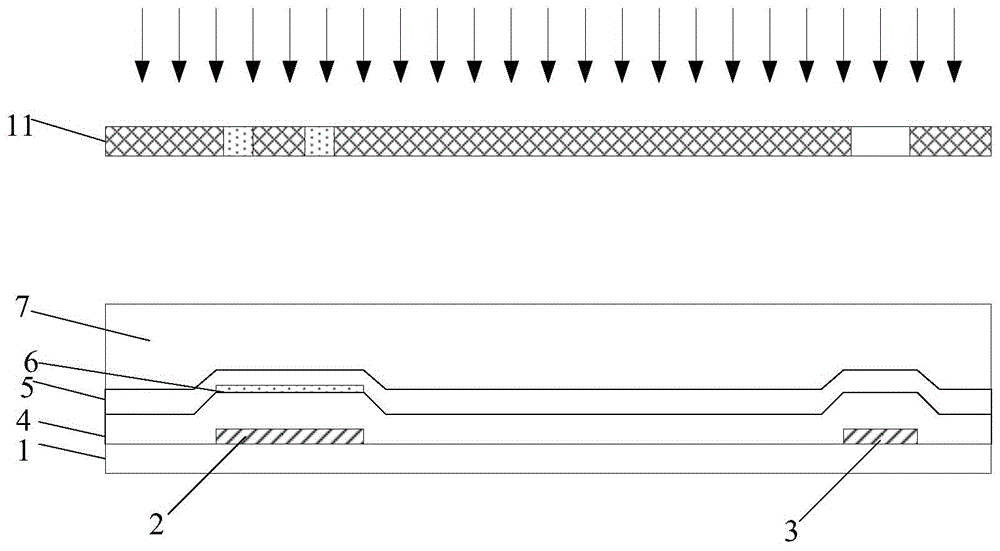

[0088] Step e, such as figure 2 As shown, the photoresist 7 is c...

Embodiment 3

[0115] This embodiment also provides an array substrate, which is manufactured by using the above method for manufacturing an array substrate.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More