Packaging structure and method of double-sided radiating semiconductor

A packaging structure, double-sided heat dissipation technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve problems such as difficulty in ensuring accuracy, overflow of heat sink glue, chip damage, etc., to improve Package quality, the effect of improving the overall heat dissipation performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

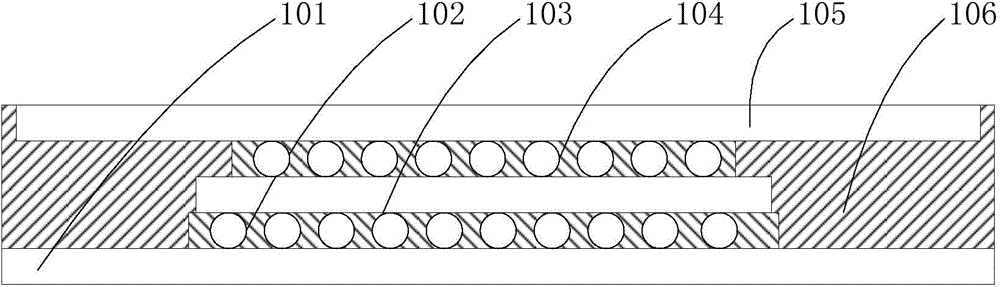

[0030] figure 1 It is a package structure diagram of a double-sided heat dissipation semiconductor provided by the first embodiment of the present invention. Such as figure 1 As shown, the double-sided heat dissipation semiconductor package structure includes:

[0031] The lead frame 101 includes a chip holder, inner leads, and outer leads.

[0032] The first bonding material 102 is located on the chip holder.

[0033] The chip 103 is located on the first bonding material 102.

[0034] The second bonding material 104 is located on the chip 103.

[0035] The heat sink 105 is located on the second bonding material 104.

[0036] Colloid 106, the colloid 106 covers the lead frame 101, the chip 103 and the heat sink 105, and the bottom surface of the chip holder and the top surface of the heat sink 105 leak out of the colloid;

[0037] The first bonding material 102 and the second bonding material 104 contain high temperature resistant equal diameter balls.

[0038] Wherein, the first bonding ...

Embodiment 2

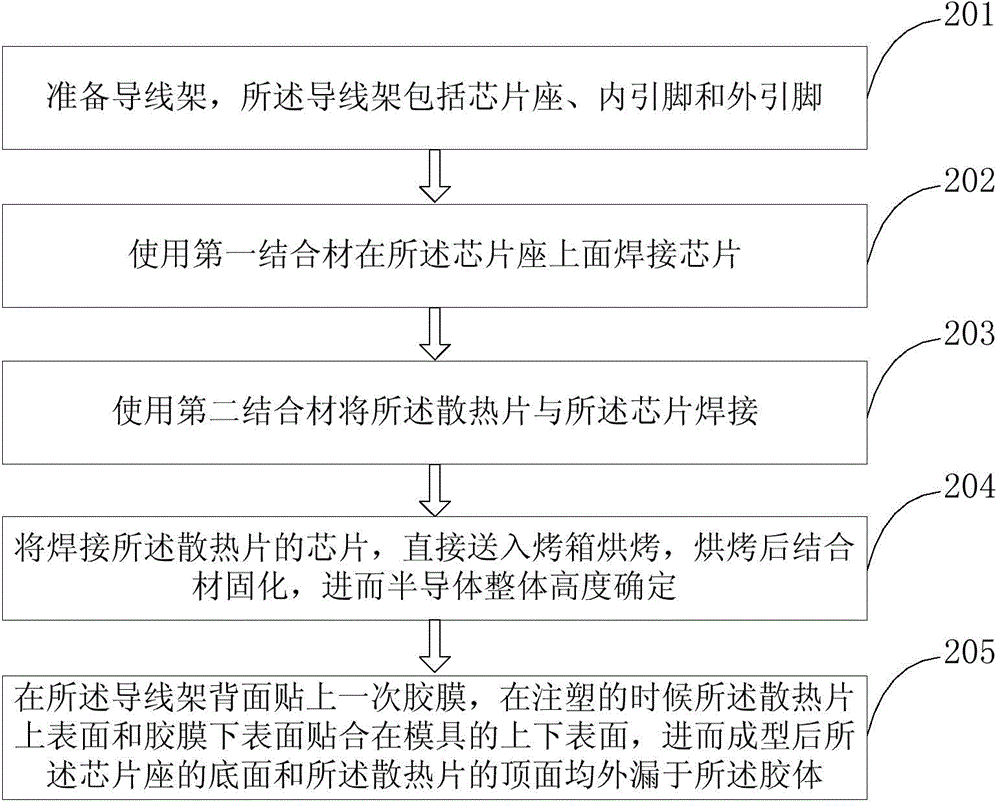

[0044] figure 2 It is a flowchart of a method for packaging a double-sided heat dissipation semiconductor according to the second embodiment of the present invention. Such as figure 2 As shown, the packaging method of the double-sided heat dissipation semiconductor includes:

[0045] Step 201: Prepare a lead frame, which includes a chip holder, inner leads, and outer leads;

[0046] Step 202: Use the first bonding material to solder chips on the chip holder;

[0047] Step 203: Use a second bonding material to weld the heat sink to the chip;

[0048] Step 204: Send the chip welded to the heat sink directly into the oven for baking, and the bonding material is solidified after baking, so that the overall height of the semiconductor is determined;

[0049] Step 205: Paste an adhesive film on the back of the lead frame to perform clamping and injection molding;

[0050] Wherein, the first binding material and the second binding material in step 202 and step 203 contain high-temperature ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More