Crystal back defect representation method

A technology for crystal back defects and characterization, applied in electrical components, electrical solid-state devices, circuits, etc., can solve the problems of increasing production cost, high price, waste, etc., and achieve the effect of improving production efficiency and simple operation.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] In order to make the above objects, features and advantages of the present invention more comprehensible, specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

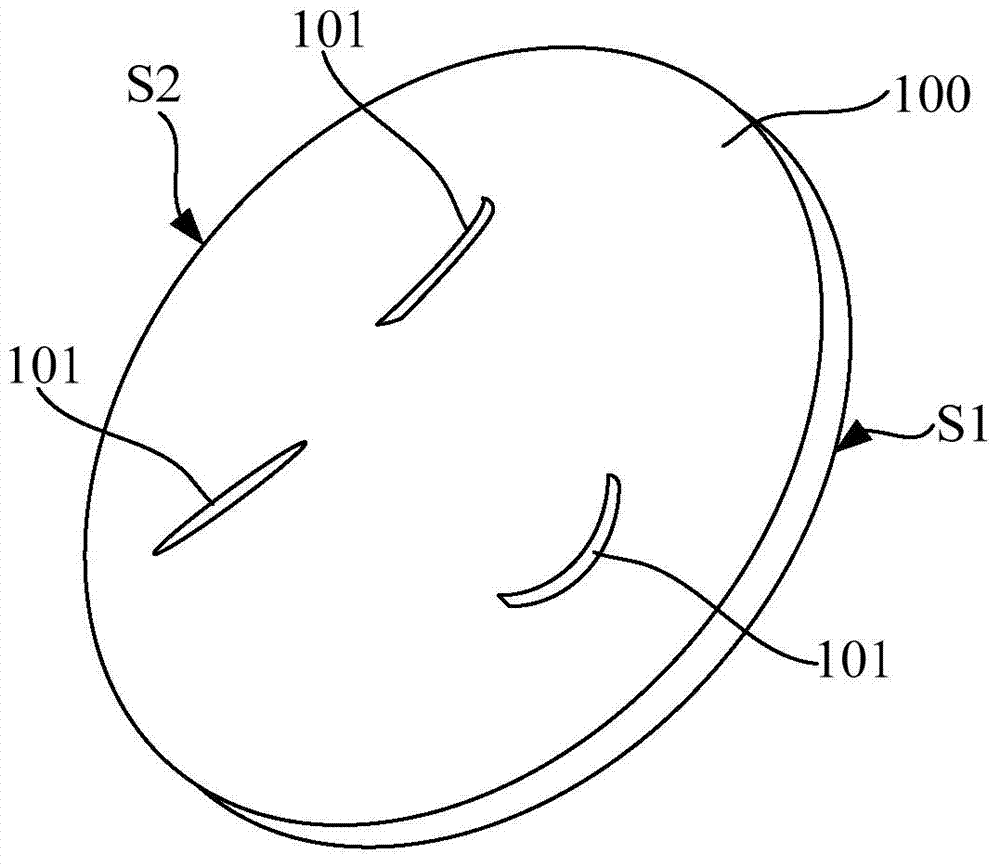

[0037] refer to figure 1 , provide a wafer 100, the wafer 100 includes a wafer front S1 and a wafer back (hereinafter referred to as the crystal back) S2, the crystal back S2 has a crystal back defect 101, and an integrated circuit (not shown in the figure) is formed on the wafer front S1 out).

[0038] It should be pointed out that the crystal back defects 101 refer to macroscopic defects visible to the naked eye such as scratches and chromatic aberrations.

[0039] Wherein, the chromatic aberration refers to that impurities remain on the crystal back S2, and the impurities partially bulge the crystal back S2, making the chromatographic colors of the crystal back S2 inconsistent. Impurities remaining on the crystal back S2 will become ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com