Patents

Literature

86 results about "Cost burden" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The burden rate consists of indirect costs associated with employees, over and above gross compensation or payroll costs. Typical costs associated with the burden rate include payroll taxes, workers' compensation and health insurance, paid time off, training and travel expenses, vacation and sick leave,...

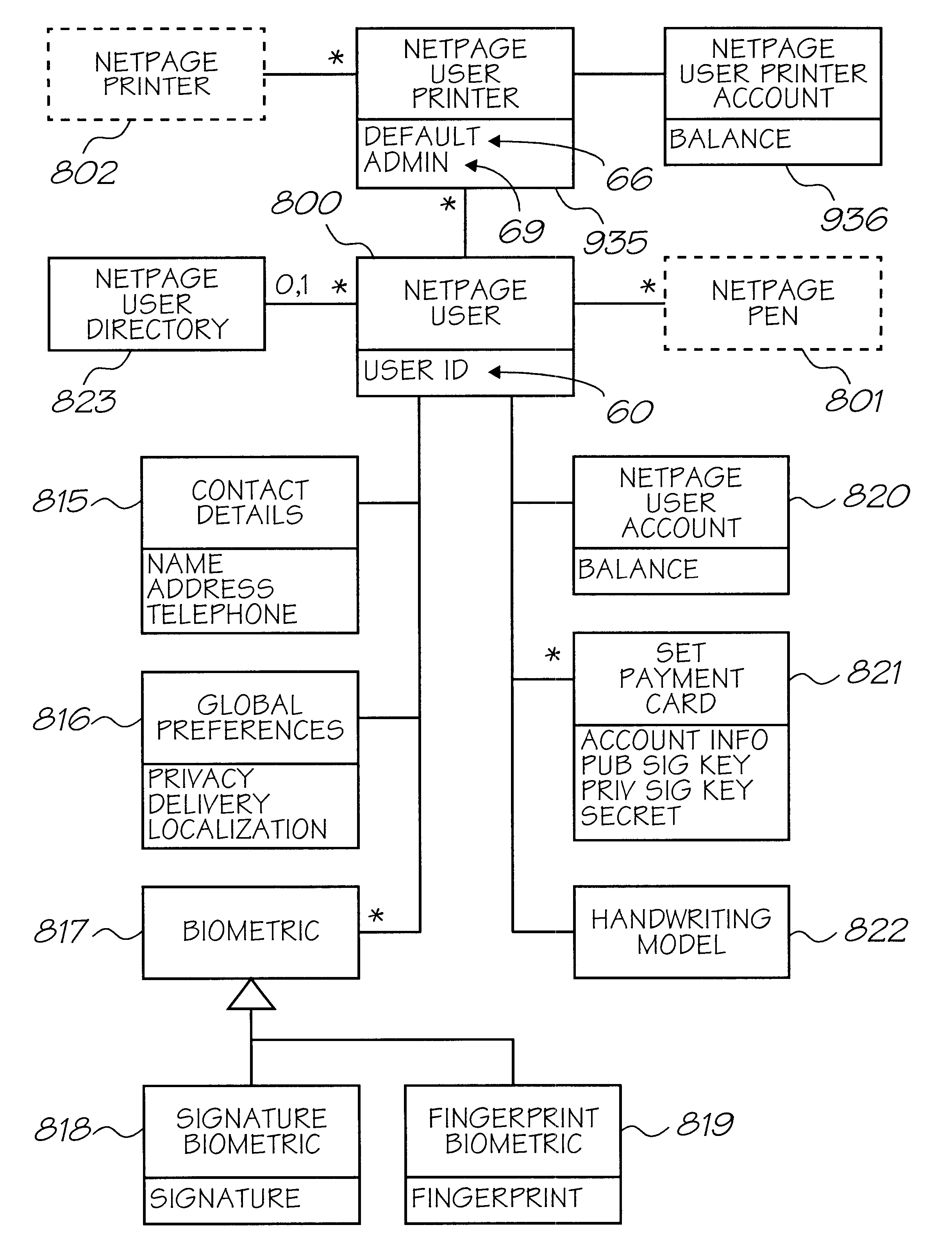

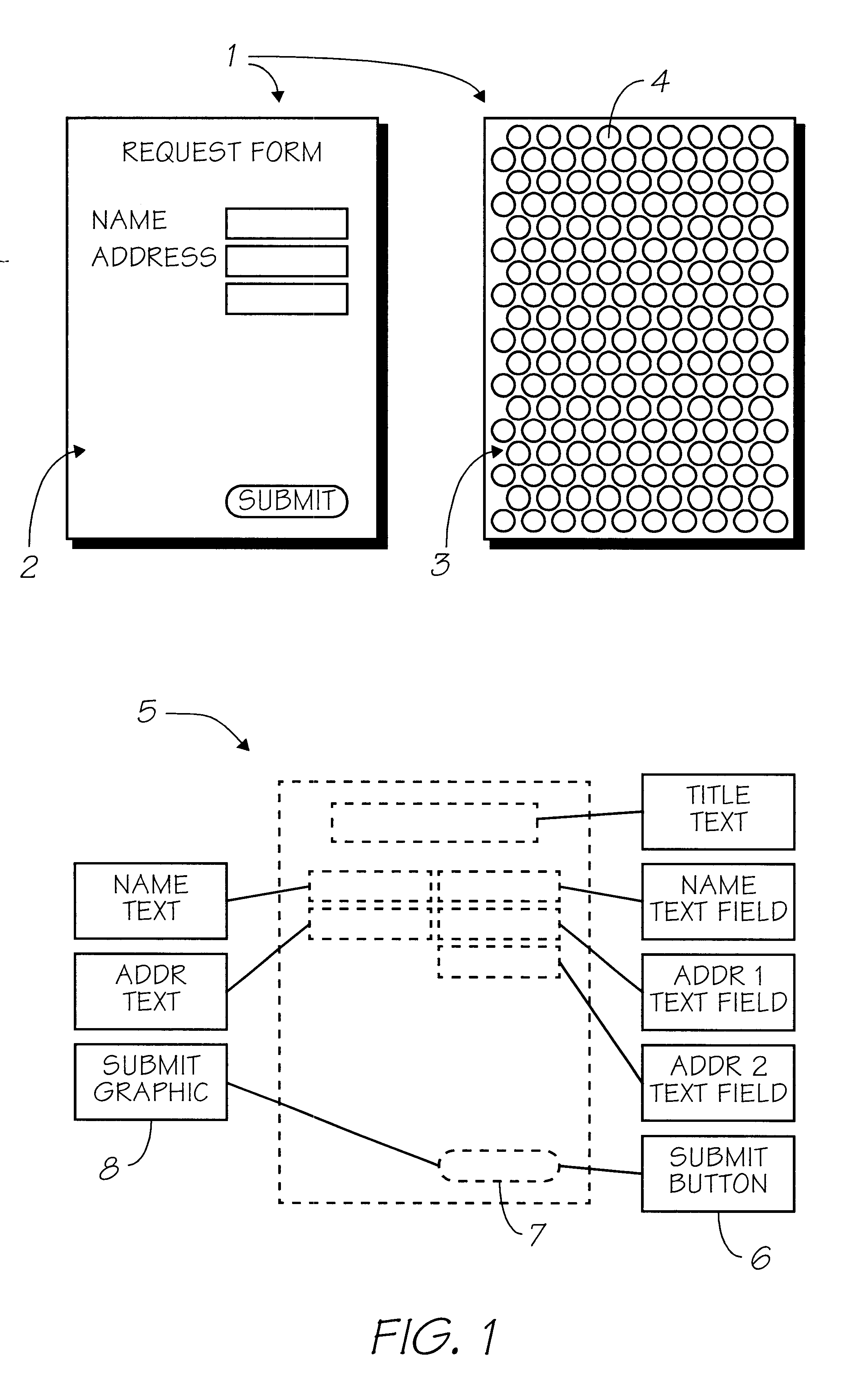

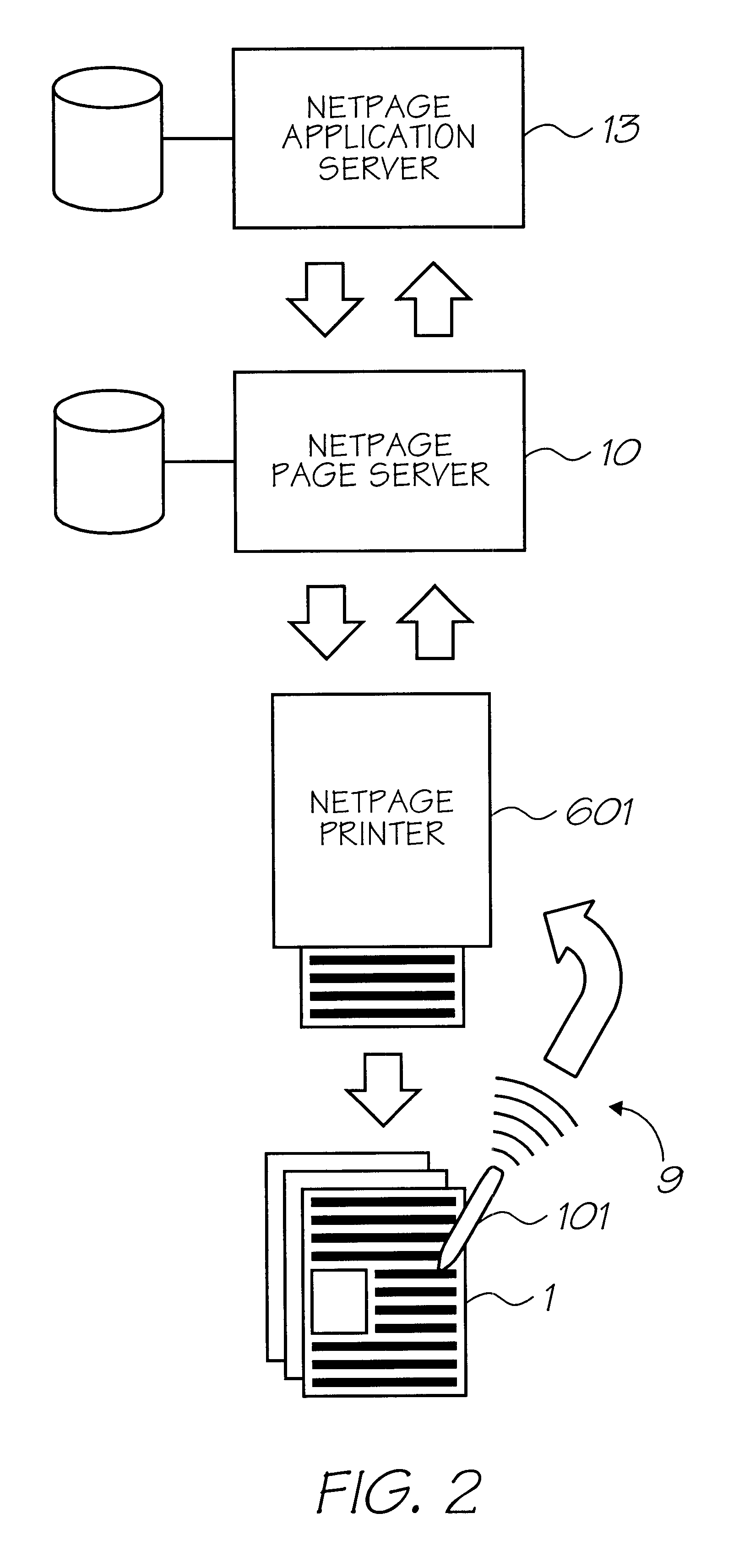

Interactive printer reward scheme

InactiveUS6457883B1Provide usageCharacter printing data arrangement from carrierError detection/correctionCost burdenPurchasing

A preferred embodiment of the invention is specifically configured to allow a printer's or a user's account to accumulate a credit balance and for all or a portion of this balance to be presented to the corresponding user or users as a collection of "points". If the printer account has a credit balance, then the corresponding points may be redeemed by the user or users for particular products or services. Users thereby learn to associate fee-earning activities in relation to the printer, such as the printing of advertising and online purchasing, with the accumulation of points, thus maximising the likelihood that a particular printer will not become a cost burden to its provider.

Owner:SILVERBROOK RES PTY LTD

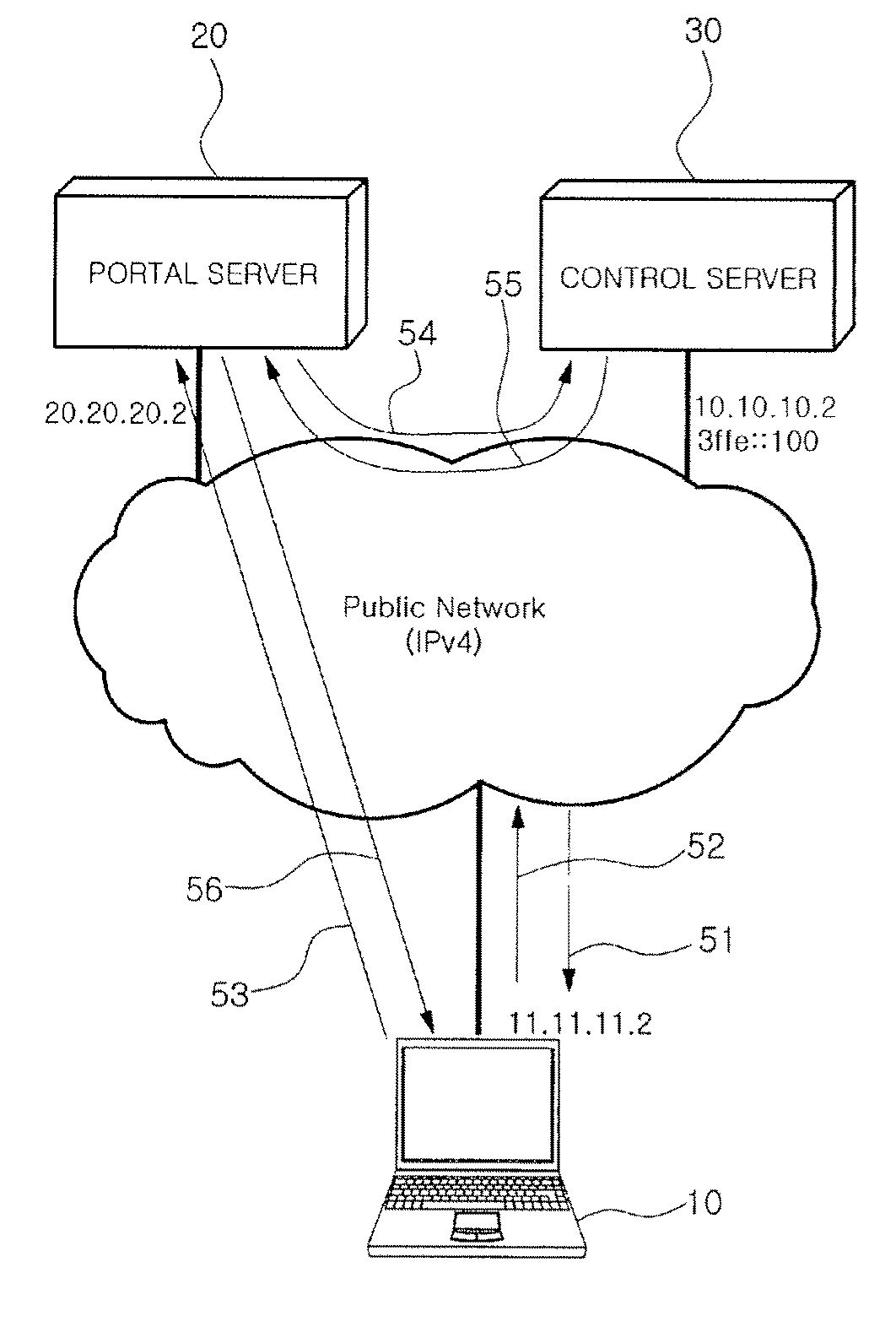

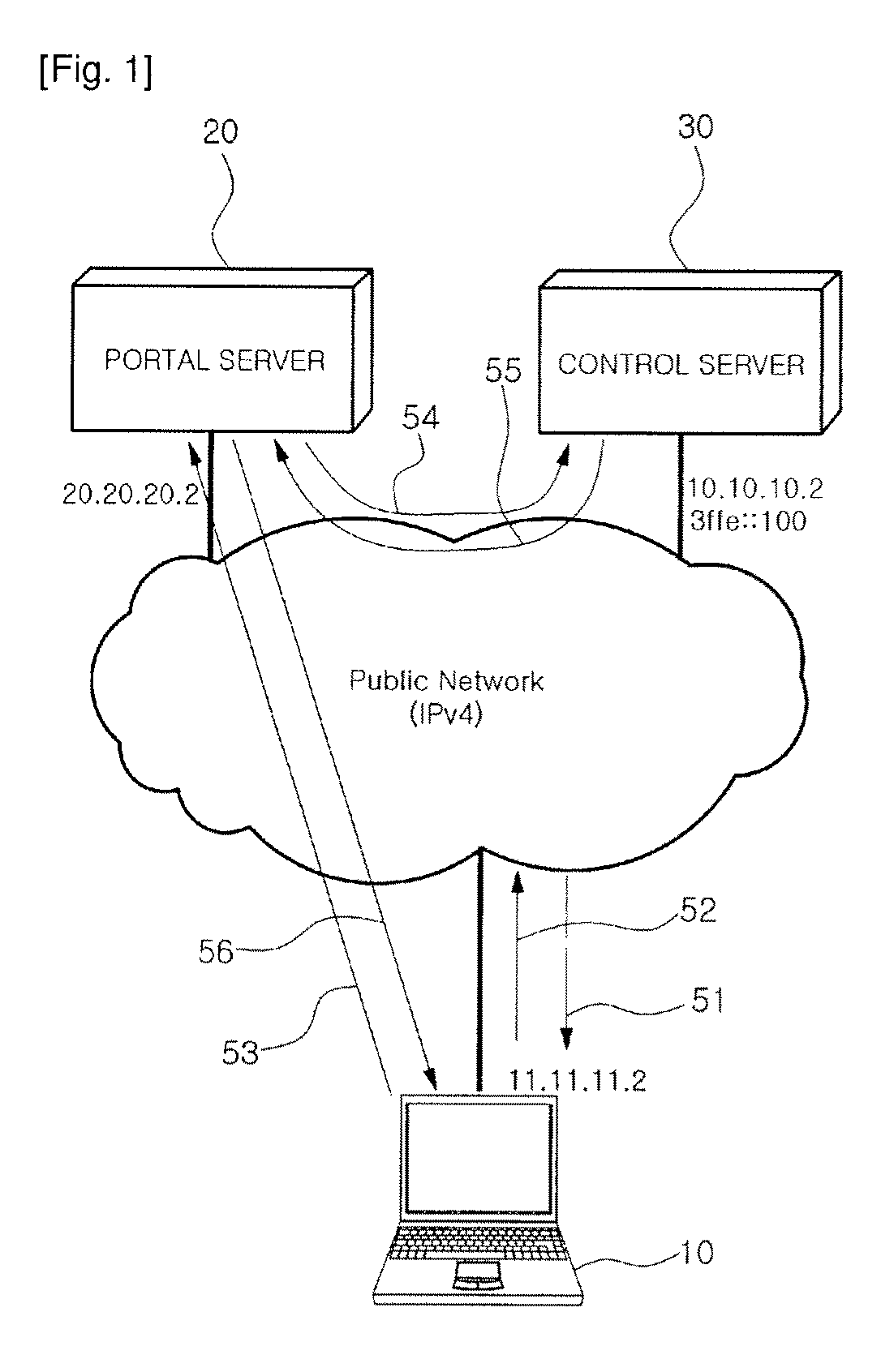

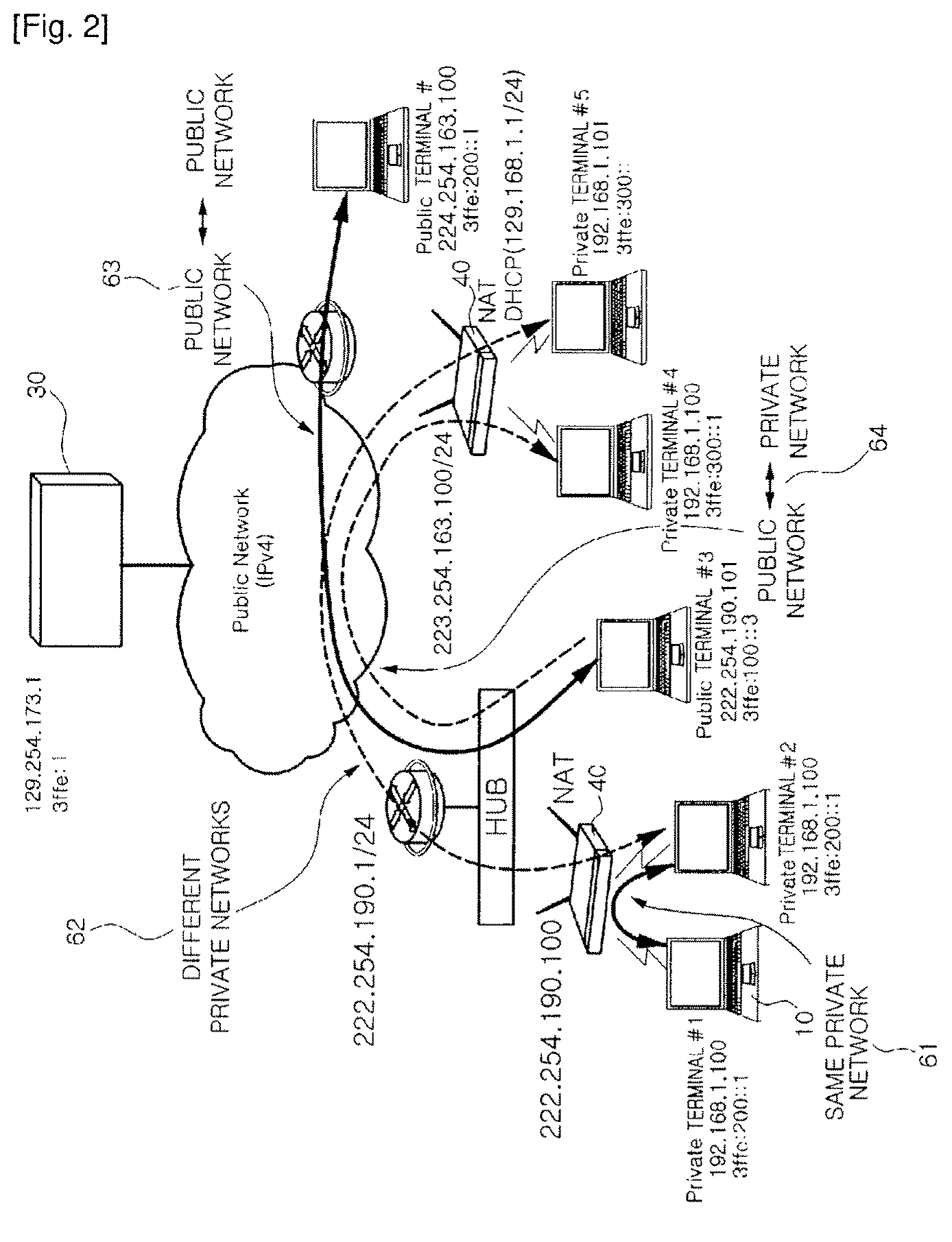

Method for configuring control tunnel and direct tunnel in ipv4 network-based ipv6 service providing system

ActiveUS20100008260A1Low costMinimizing cost burdenNetworks interconnectionNetwork connectionsCost burdenService information

Provided is a method for configuring a control tunnel and a direct tunnel in an IPv4 network-based IPv6 service providing system. To provide IPv6 service, when a random request terminal receives a tunnel response message from a control server by using service information downloaded from a portal server at the time of initialization, the request terminal configures a control tunnel with the control server, and is registered to the control server. The request terminal transmits and receives a direct tunnel request message and a direct tunnel response message with a counterpart terminal by using its terminal information learned during the control tunnel configuration, i.e., network position information and status information, thereby configuring a direct tunnel. Thus, IPv6 communication is made through IPv4 based IPv6 tunneling, so that IPv6 application services that are not yet widely used can easily come into wide use. Also, only software change of each terminal and a control server is required without changing existing network equipment, so that a cost burden of a service provider can be minimized.

Owner:ELECTRONICS & TELECOMM RES INST +1

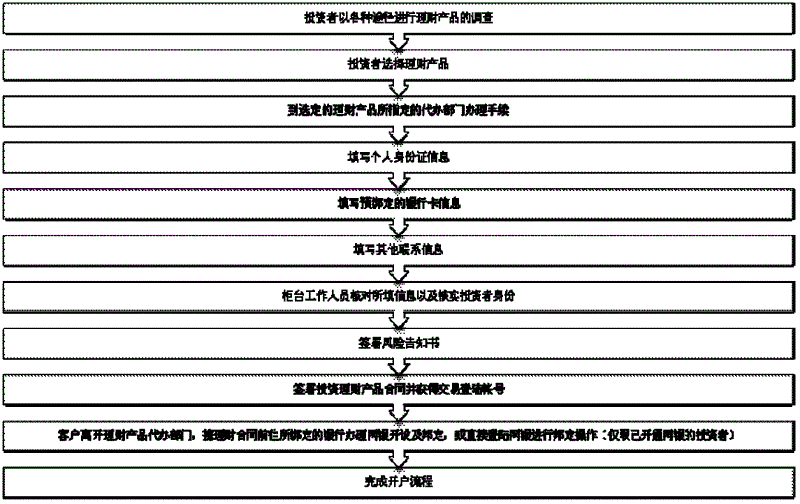

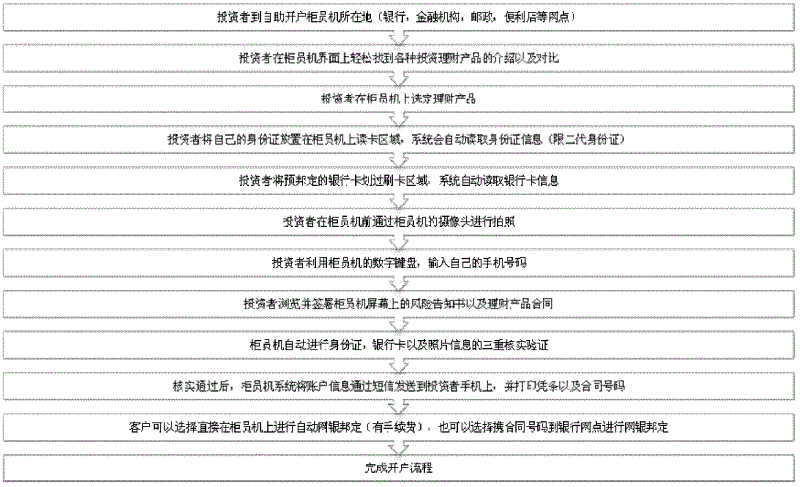

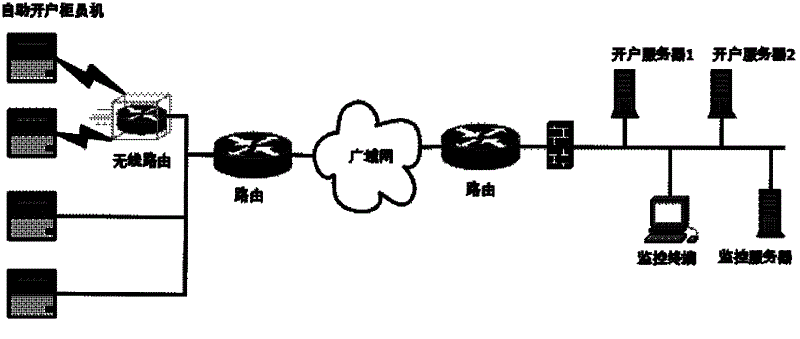

Self-service account opening system and self-service account opening method thereof

InactiveCN102622707ASimplified account opening processEasy to open an accountFinanceCost burdenTerminal equipment

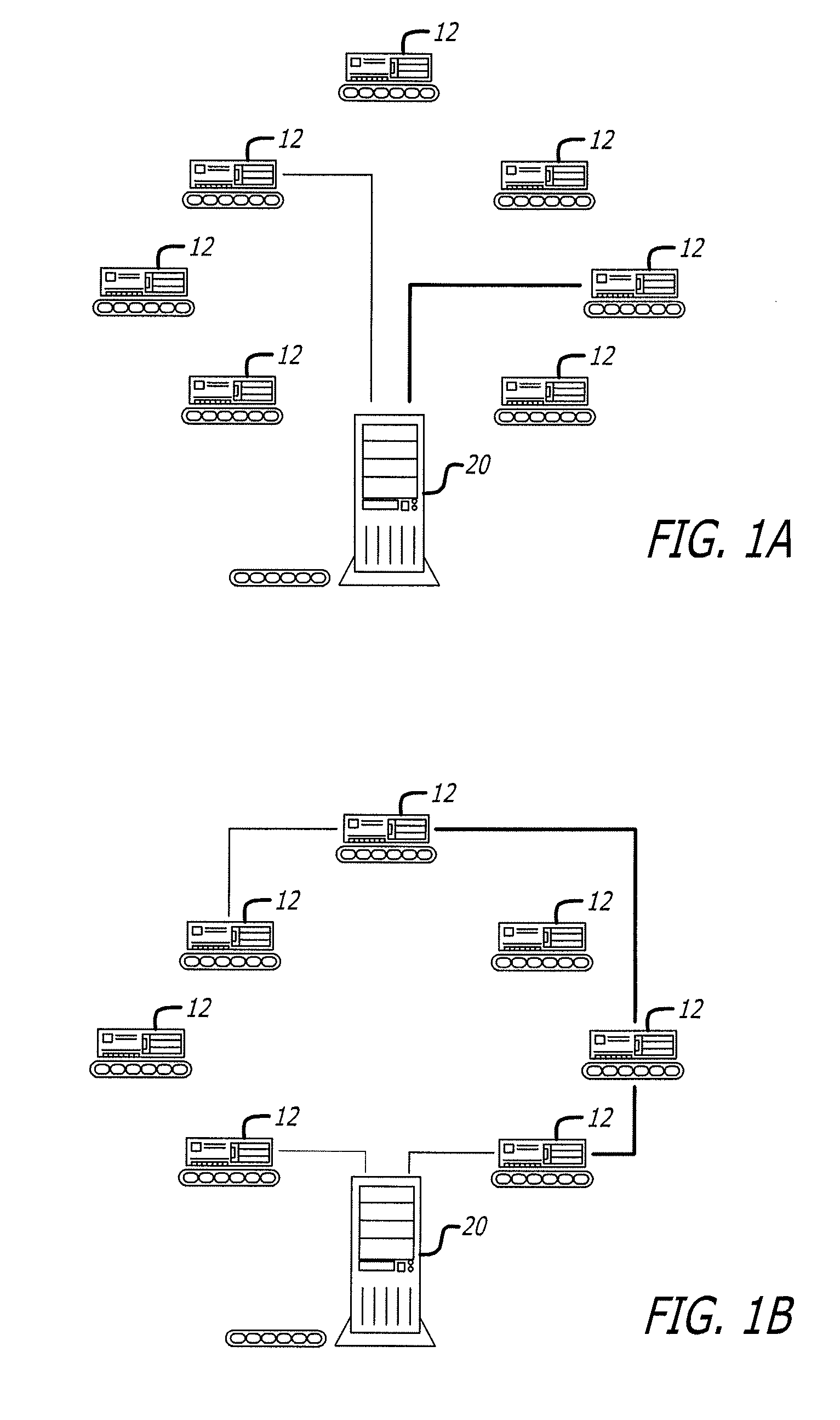

The invention relates to a self-service account opening system and a self-service account opening method thereof, in particular to a system for clients to open accounts in a self-service manner and a self-service account opening method for the system. Self-service account opening automatic teller machines arranged in different regions in a scattered manner are connected with a server system in a wide area network via wired or wireless route equipment; and the self-service account opening automatic teller machines are terminal equipment of the self-service account opening system and are used for being interacted with the clients. The invention further discloses the self-service account opening method realized by the aid of the self-service account opening automatic teller machines. Problems in a present financial product account opening flow are resolved, investment account opening flow is simplified, investors can conveniently open accounts of financial products, cost burden and repeated construction risks of branches of financial product business enterprises are relieved, and accordingly the investors and the financial product business enterprises are benefited.

Owner:孙大利

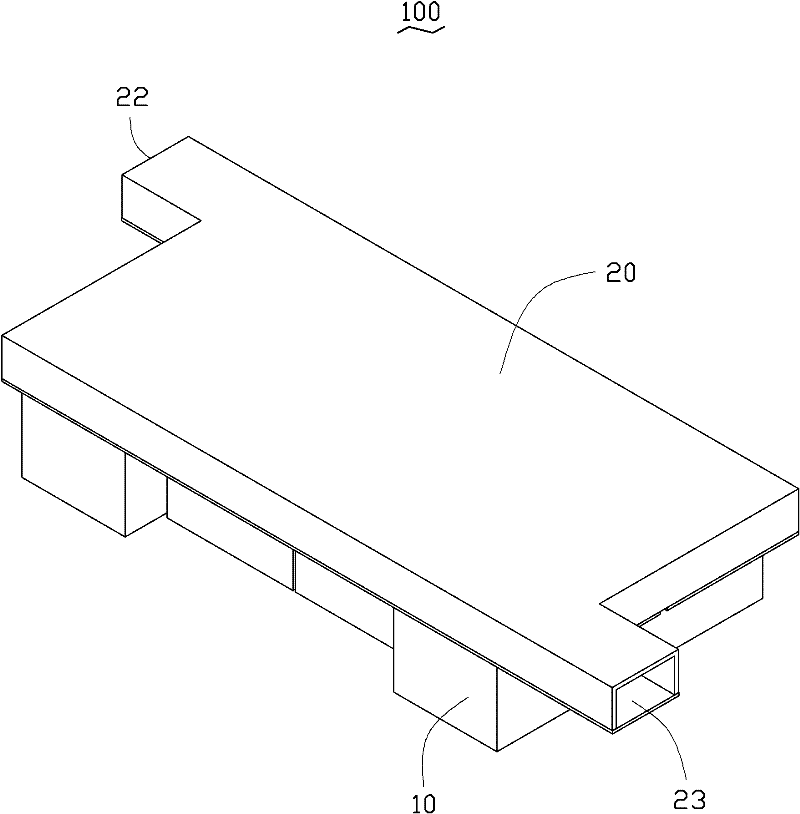

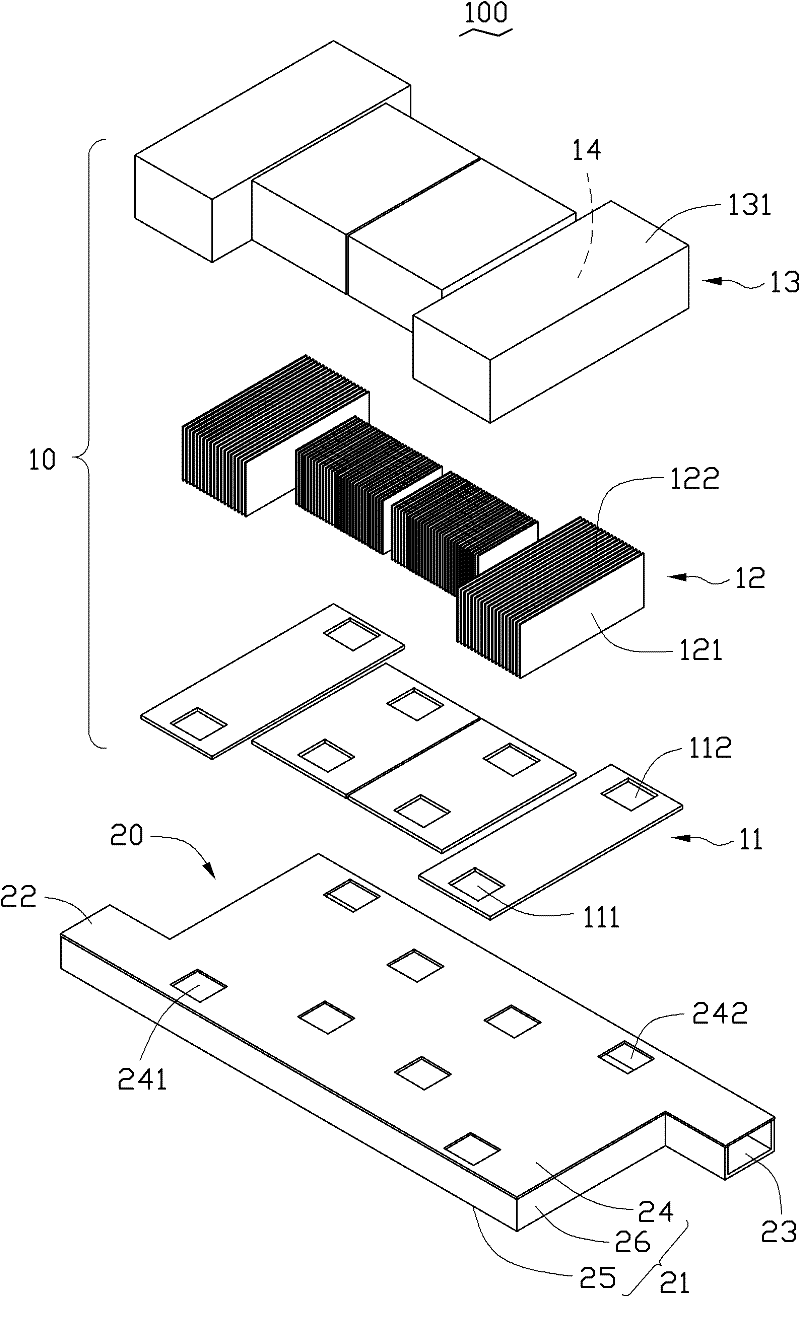

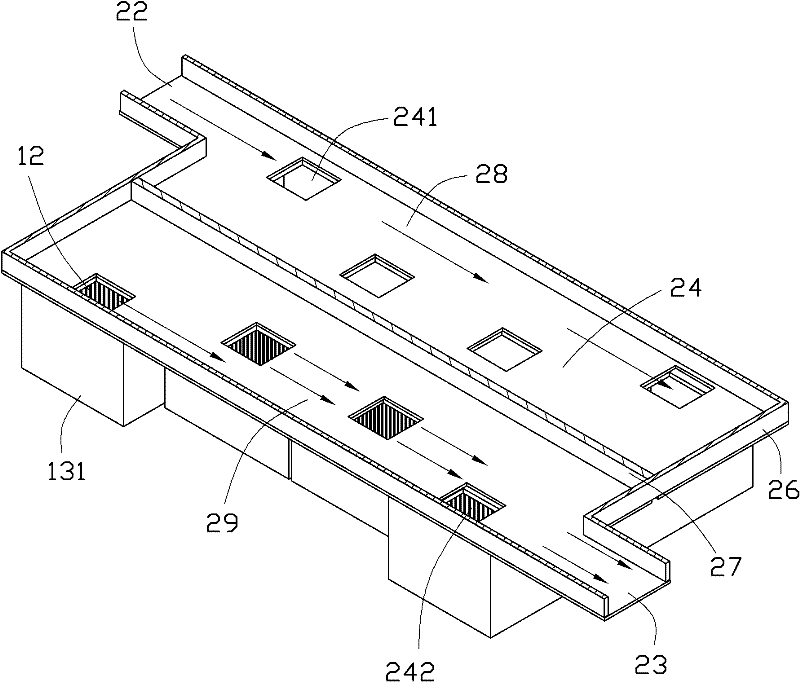

Liquid-cooled radiating device

InactiveCN102543916ASimple structureReduce volumeDigital data processing detailsSemiconductor/solid-state device detailsCost burdenEngineering

A liquid-cooled radiating device is used for radiation of at least one heating electronic component, and comprises at least one liquid-cooled head and a container connected with the liquid-cooled heads. A closed containing space is formed in each liquid-cooled head which is provided with a first liquid inlet and a first liquid outlet, the container comprises a liquid inlet passage and a liquid outlet passage which are isolated from each other, a liquid inlet pipe for cooling media to inflow is arranged on the side of the container as same as that of the liquid inlet passage and is communicated with the first liquid inlets, and a liquid outlet pipe for cooling media to flow out is arranged on the side of the container as same as that of the liquid outlet passage and is communicated with the first liquid outlets. The liquid-cooled radiating device is small in size, simpler than an air-cooled radiating device in structure, low in development cost and capable of relieving cost burden for redesign and redevelopment under different platforms and effectively saving design cost.

Owner:中山市云创知识产权服务有限公司

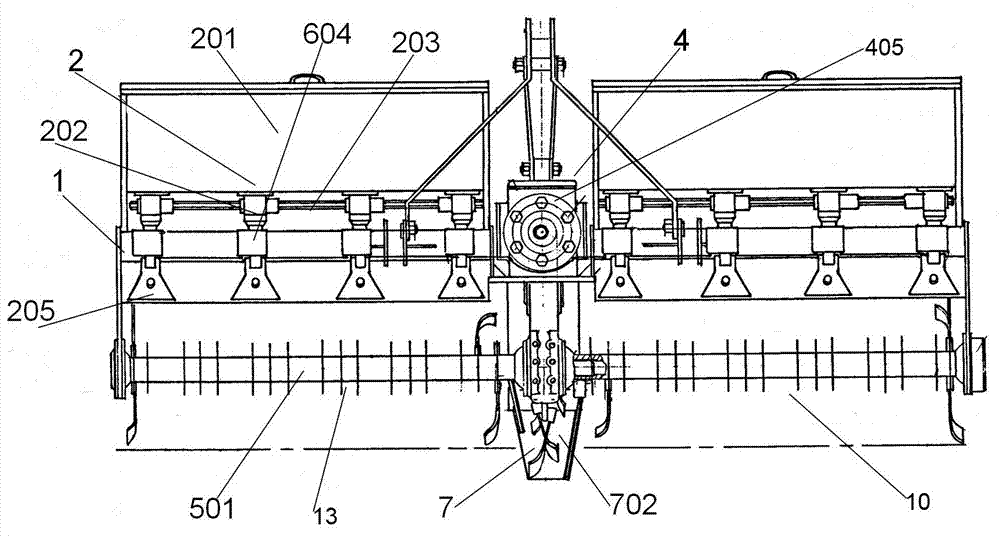

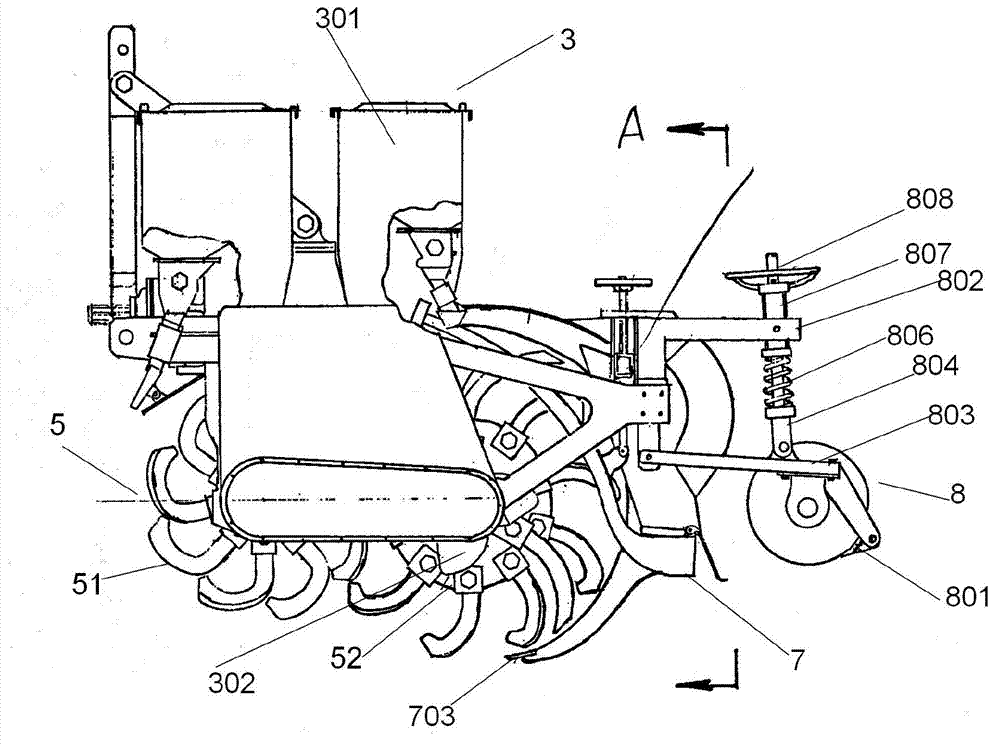

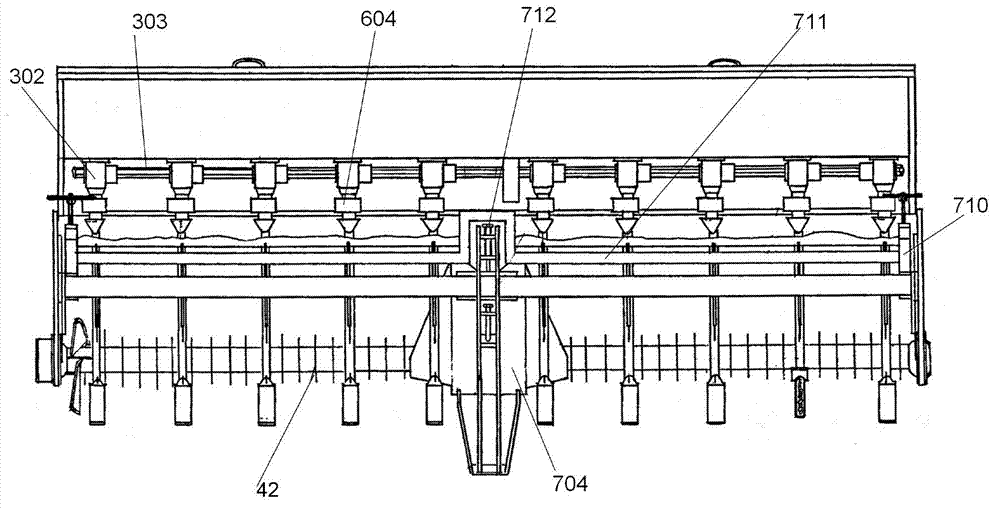

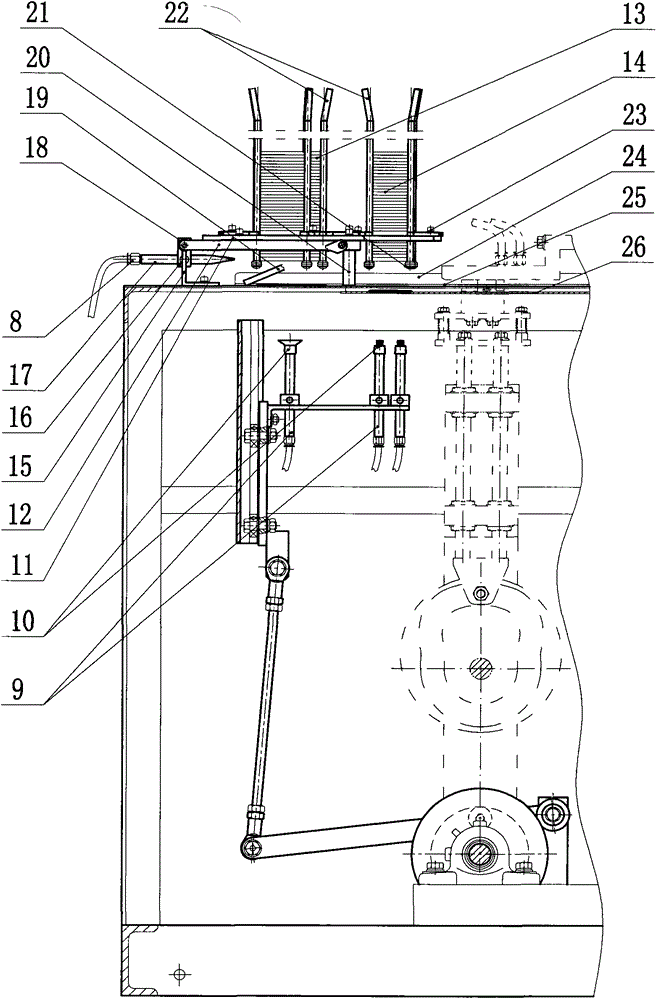

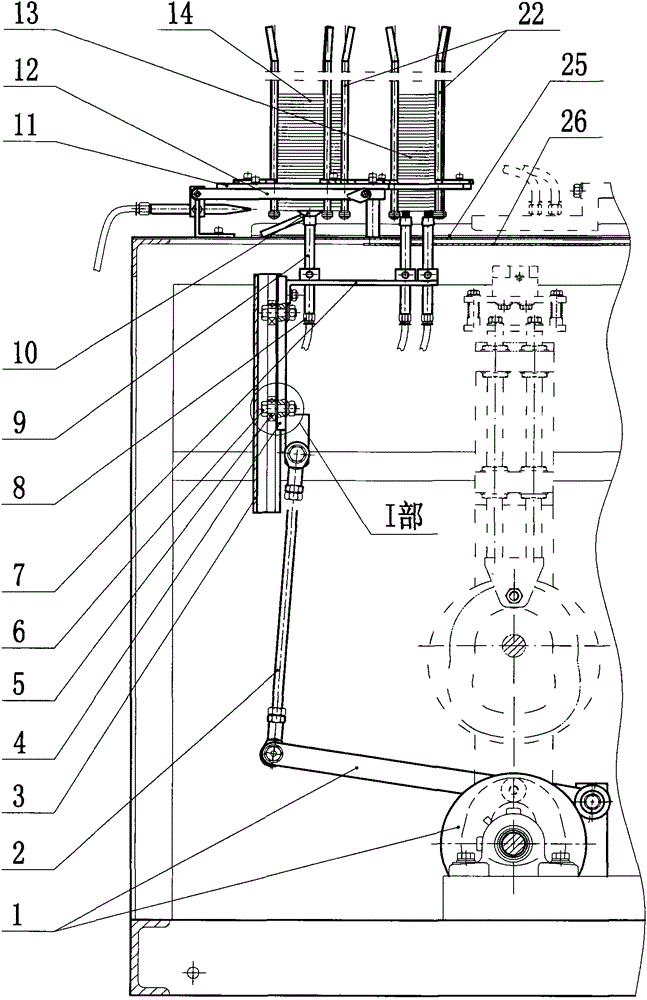

Intelligent rotary tillage and fertilization seeder

ActiveCN103314669ASowing performance is stableGood stubble removal performance when returning to the field in full amountSpadesSaving energy measuresCost burdenControl system

The invention discloses an intelligent rotary tillage and fertilization seeder which comprises a rack as well as a fertilizer metering mechanism, a seed feeding mechanism, a transmission mechanism, a stubble cleaning mechanism and a control system, wherein the stubble cleaning mechanism comprises a stubble cleaning unit and a two-step soil tilling stubble cleaning unit; the control system comprises a controller as well as a display panel, a monitor, a driver and a speed sensor which are connected with the controller; and monitors and drivers are installed on both the fertilizer metering mechanism and the seed feeding mechanism. The intelligent rotary tillage and fertilization seeder has the advantages that the intelligent degree is high, the stubble cleaning performance is good, the usage is flexible and convenient, and the like; and the stubble cleaning rate can reach up to 92% and is increased by more than 20% compared in comparison with a single stubble cleaning rotary cultivator, and the soil tilling rate is increased by more than 5%. The intelligent rotary tillage and fertilization seeder can reduce labor intensity greatly, the investment of labor force and the tillage cost burden effectively.

Owner:TAICANG XIANGSHI AGRI MACHINE

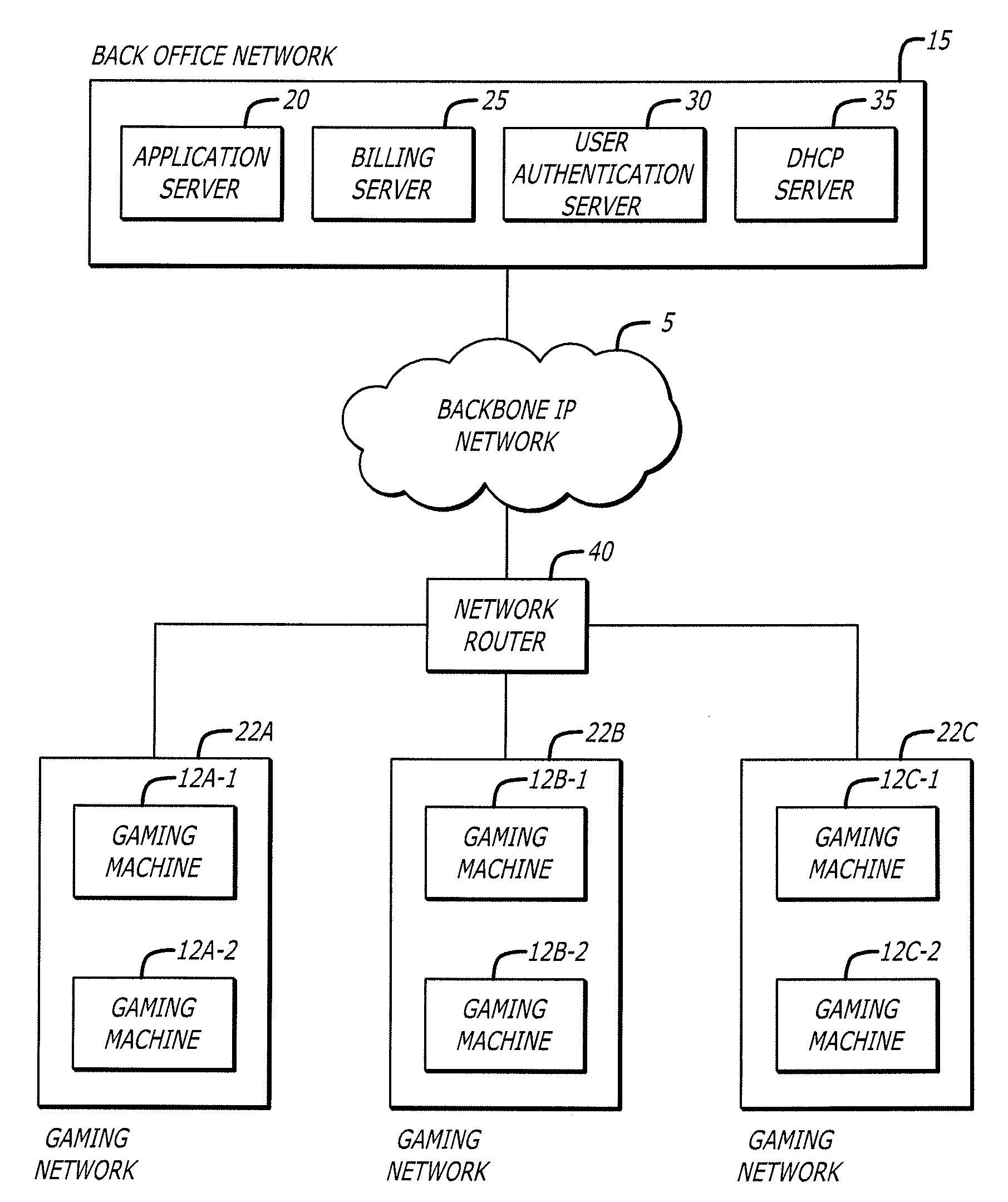

Download and data transfer gaming system

InactiveUS7743163B2Easy to downloadRedistributing burdenMultiple digital computer combinationsApparatus for meter-controlled dispensingComputer hardwareData integrity

A download and data transfer gaming system utilizes a hybrid peer-to-peer, segmented file distribution protocol to vastly improve the download capabilities of a gaming system by improving the upload cost burdened by the download host. The system redistributes this cost to the download clients by allowing clients on the gaming system to upload pieces of a file to each other. This system is much more redundant by eliminating the possibility of a client missing a download broadcast. The system alleviates this possibility of missing packets and bad data integrity by using SHA-1 verification of the file pieces. The benefits of the improved bandwidth capabilities enable the download of much larger files, thus enhancing the game play experience.

Owner:BALLY GAMING INC

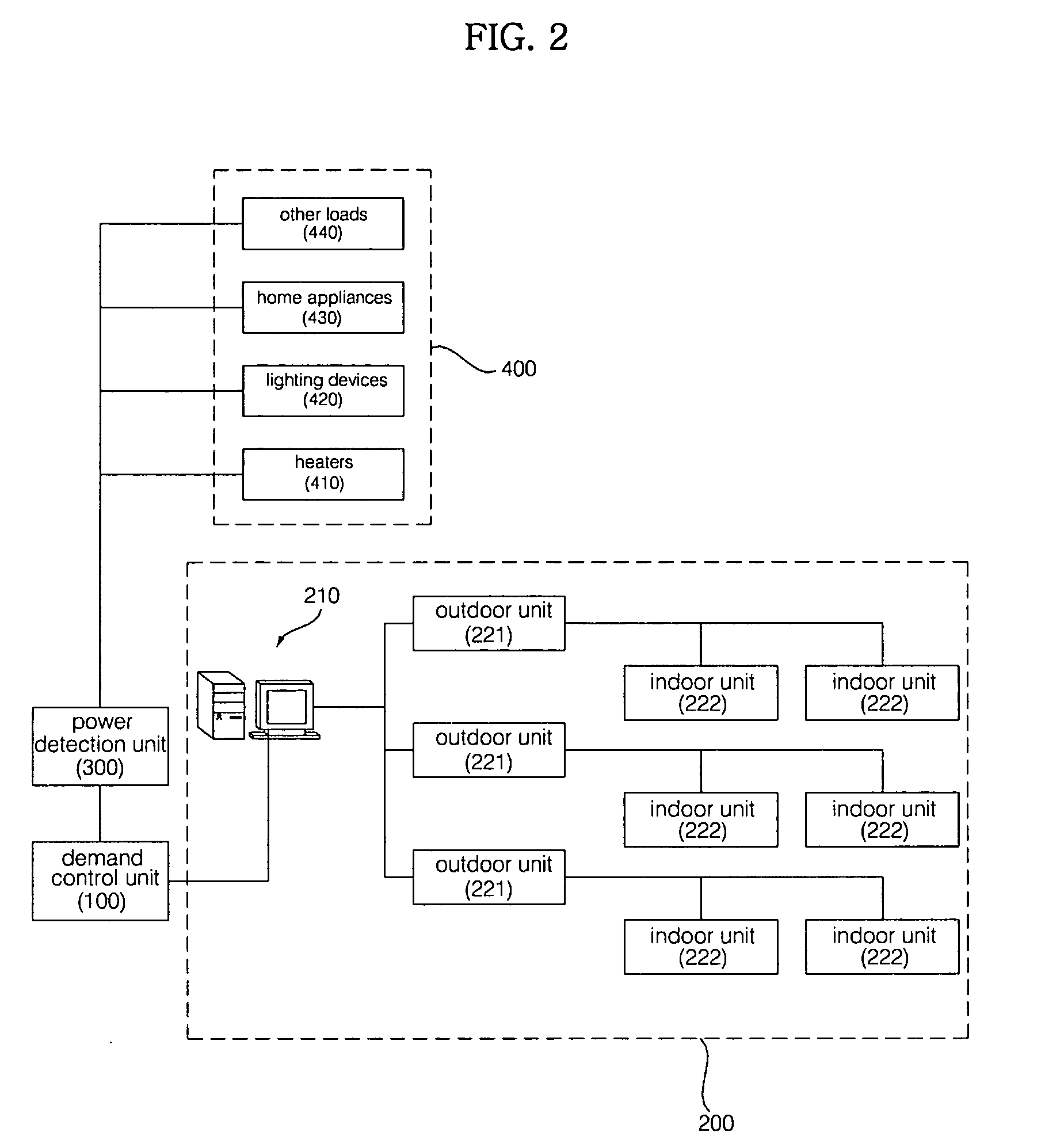

Multi-air conditioner peak power control system and control method thereof

InactiveUS20060207269A1Addressing slow performancePerformed rapidly and efficientlyMechanical apparatusSpace heating and ventilation safety systemsCost burdenControl system

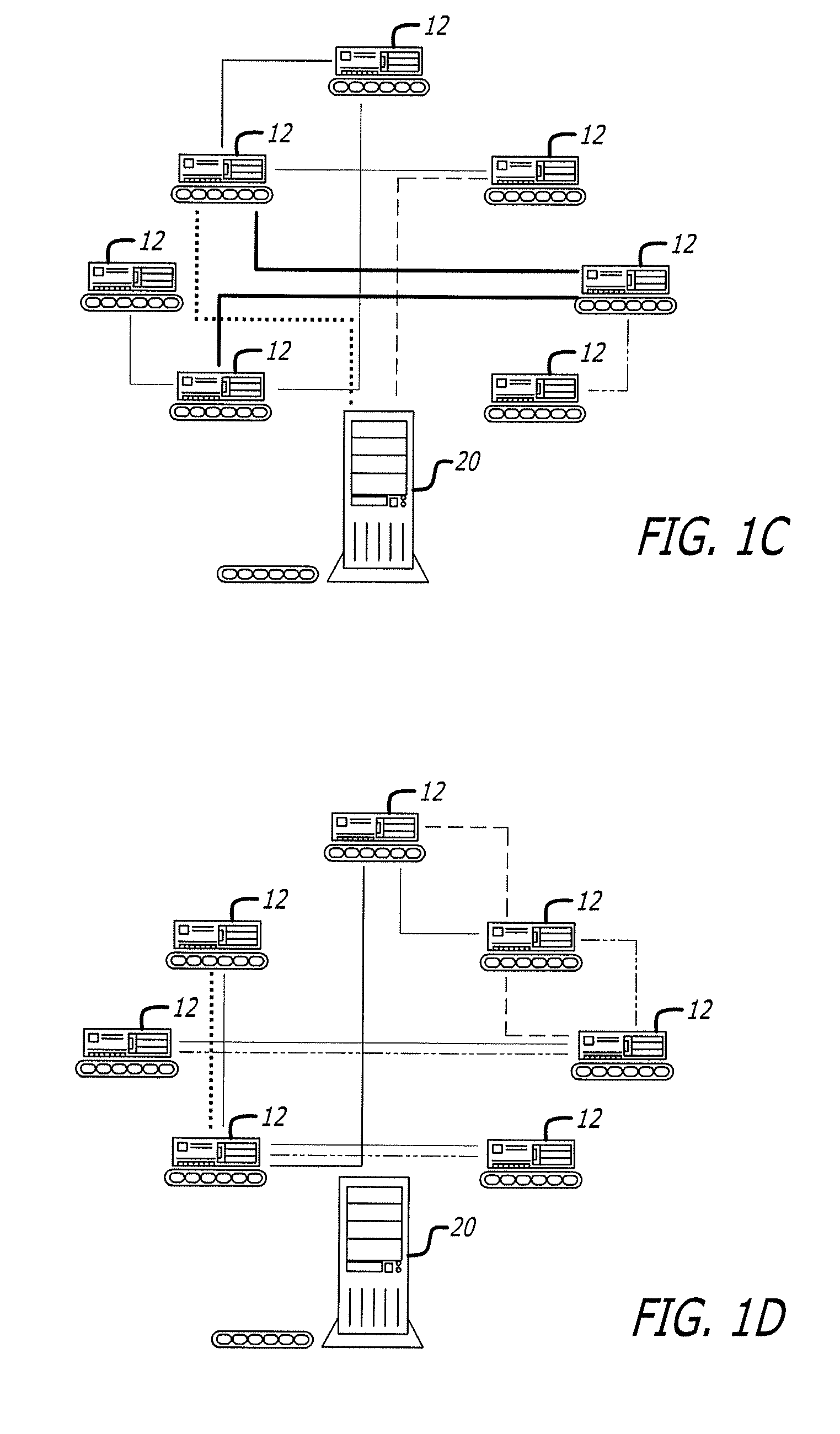

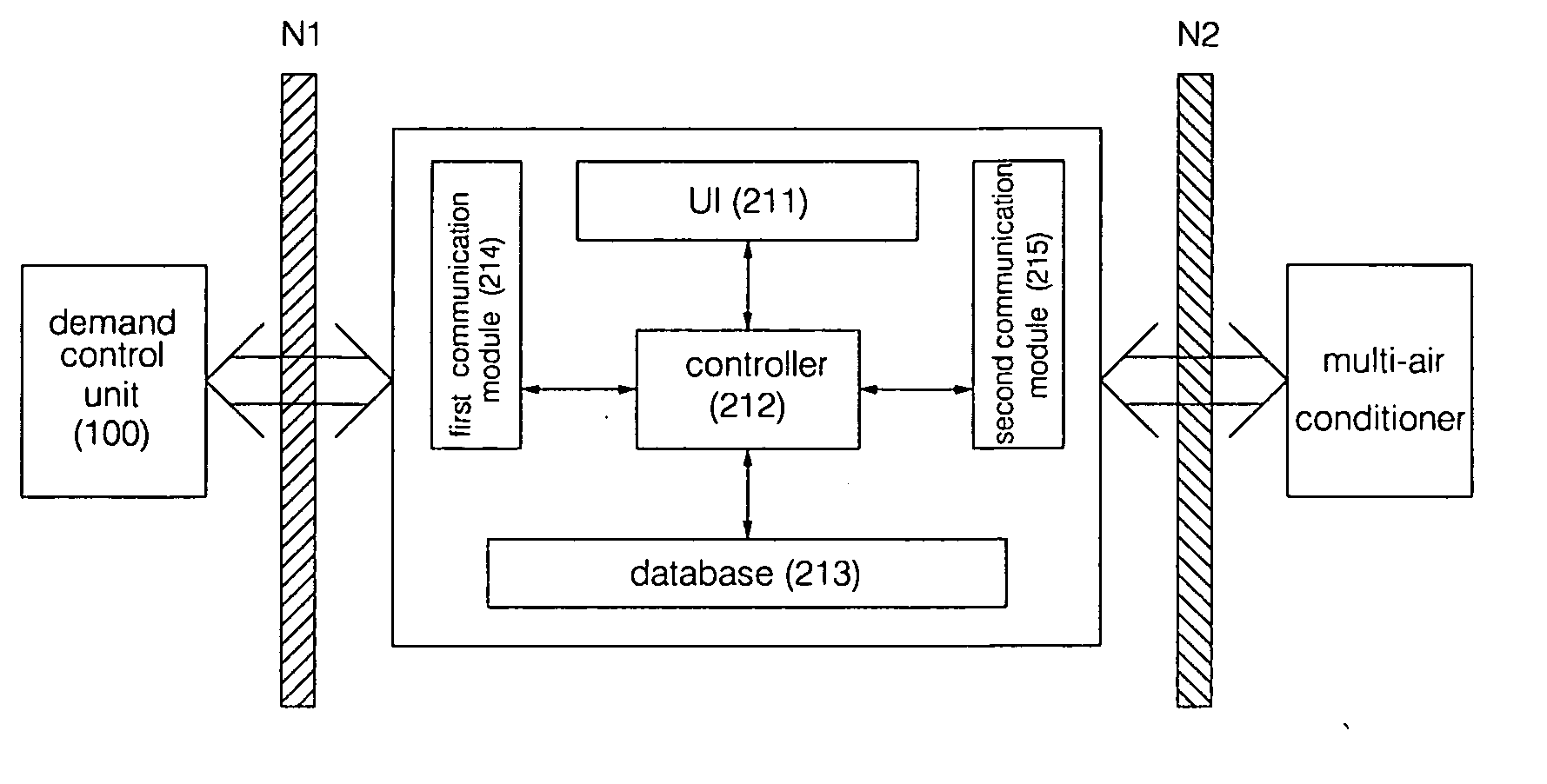

Disclosed herein are a multi-air conditioner peak power control system and a control method thereof. The peak power control system comprises a central control unit for controlling a multi-air conditioner system including a plurality of multi-air conditioners each having an outdoor unit and a plurality of indoor units in an integrated manner, and operating the multi-air conditioner system at a reference operation rate, and a demand control unit for sending / receiving data to / from the central control unit to control power consumption of the multi-air conditioner system such that the power consumption is less than total reference power consumption allocated to a building. The control method of the peak power control system adjusts the total power consumption in the building such that the total power consumption does not exceed the total reference power consumption in a more efficient and convenient way, thereby reducing excessive cost burden due to power over-consumption and significantly enhancing user convenience.

Owner:LG ELECTRONICS INC

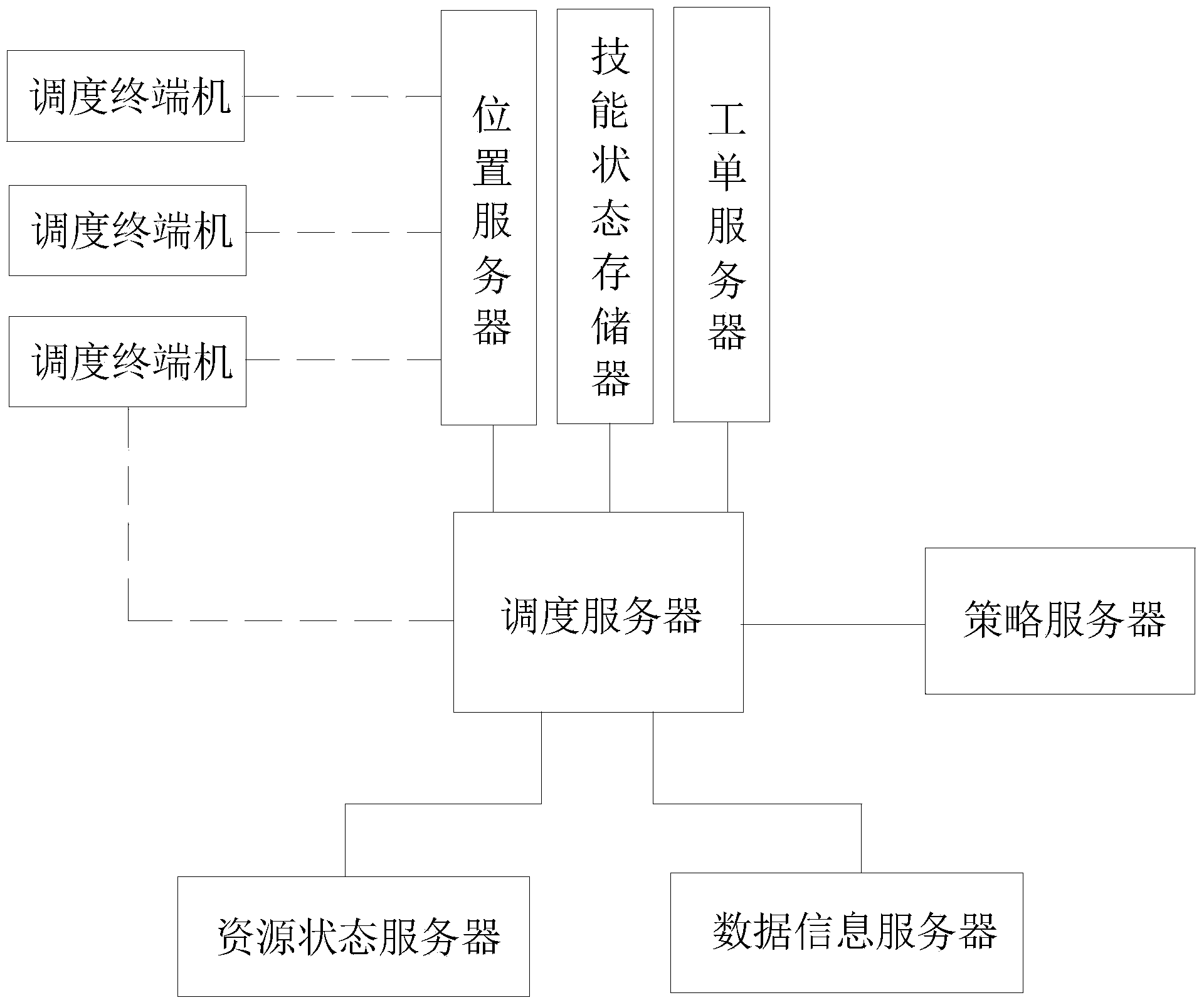

Dispatching command system

InactiveCN103955770ADistribution balanceImprove work efficiencyForecastingResourcesStrategy executionCost burden

The invention provides a dispatching command system which comprises a dispatching server, a position server, a skill state storage, a work order server, a strategy server and a plurality of dispatching terminals; the work order server is used for storing basic task order types; the skill state storage is used for storing personnel files of all project personnel; the strategy server is used for storing and calculating dispatching decisions; the position server is used for obtaining map information; the dispatching server is used for receiving task orders, calling the position server, the skill state storage, the work order server and the strategy server, and matching resources and allocating task orders to the dispatching terminals; the dispatching terminals are used for sending position information to the position server, and receiving task orders from the dispatching server. By means of the dispatching command system, overall optical distribution is conducted, the dispatching strategy is separated from the strategy execution, nonlinear condition constraints, and balanced distribution of labor and work resources are achieved, work efficiency is improved, and the cost burden is reduced.

Owner:GUANGDONG HAIGE ICREATE TECHNOLOGY CO LTD

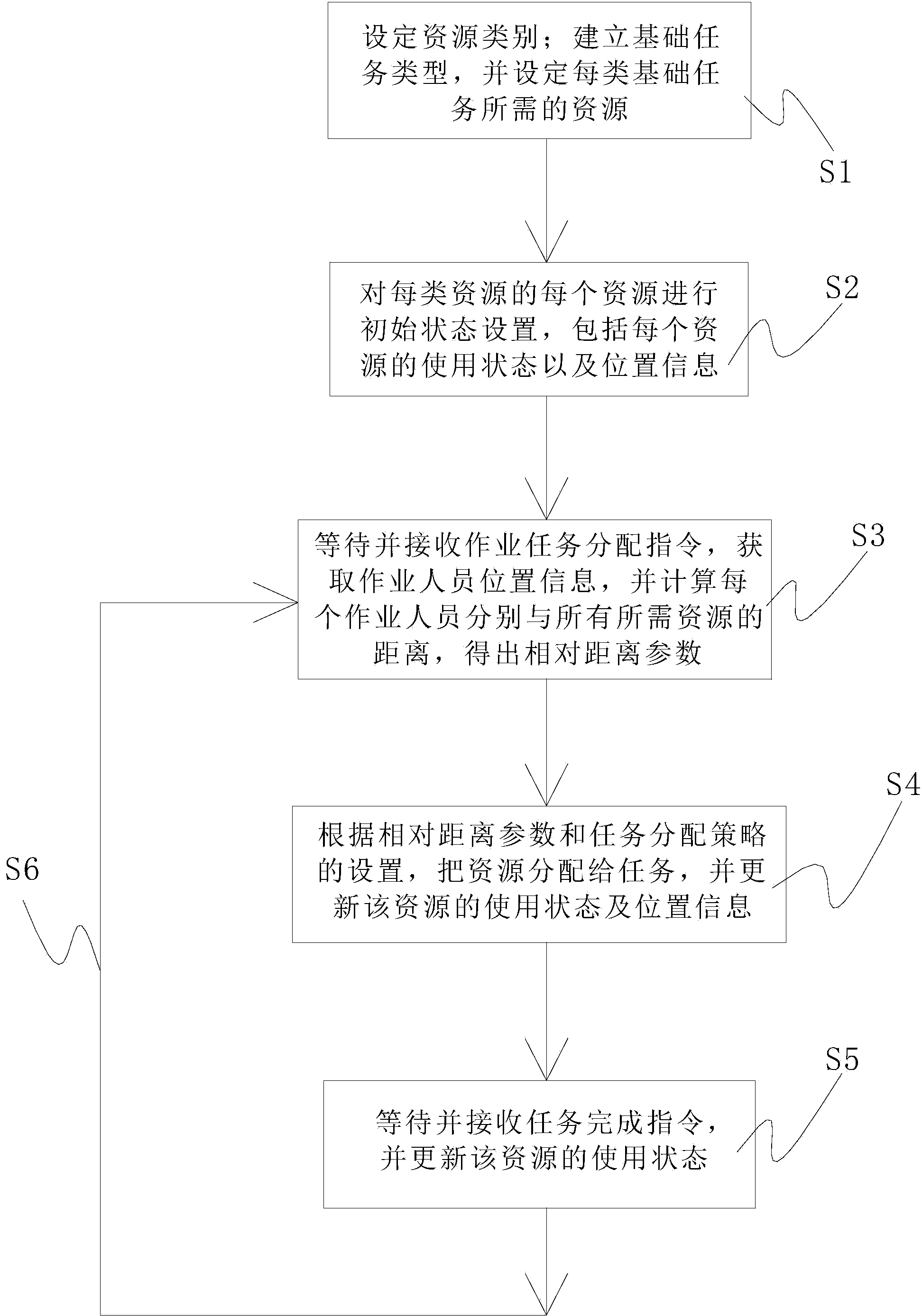

Job resource dispatching method

The invention provides a job resource dispatching method. The method comprises the following steps of 1, setting resource classes, setting up basic task types, and setting the types of resources needed by all the types of basic tasks; 2, carrying out initial state setting on each resource of all the types of the resources, wherein the initial state comprises the use state and position information of each resource; 3, waiting for and receiving a job task distribution instruction, obtaining the position information of operators, and calculating the distance between all operators and all the needed resources to obtain relative distance parameters; 4, according to setting of the relative distance parameters and a task distribution strategy, distributing the resources to the tasks, upgrading the position information of the resources, and upgrading the use state to be in use; 5, waiting for and receiving a task complementation instruction, and upgrading the use state of the resources to be idle; 6, returning to and executing the step 3. According to the job resource dispatching method, the job resources and the job tasks are matched as a whole, the resources are reasonably distributed to the operators, and the cost burden is lowered.

Owner:GUANGDONG HAIGE ICREATE TECHNOLOGY CO LTD

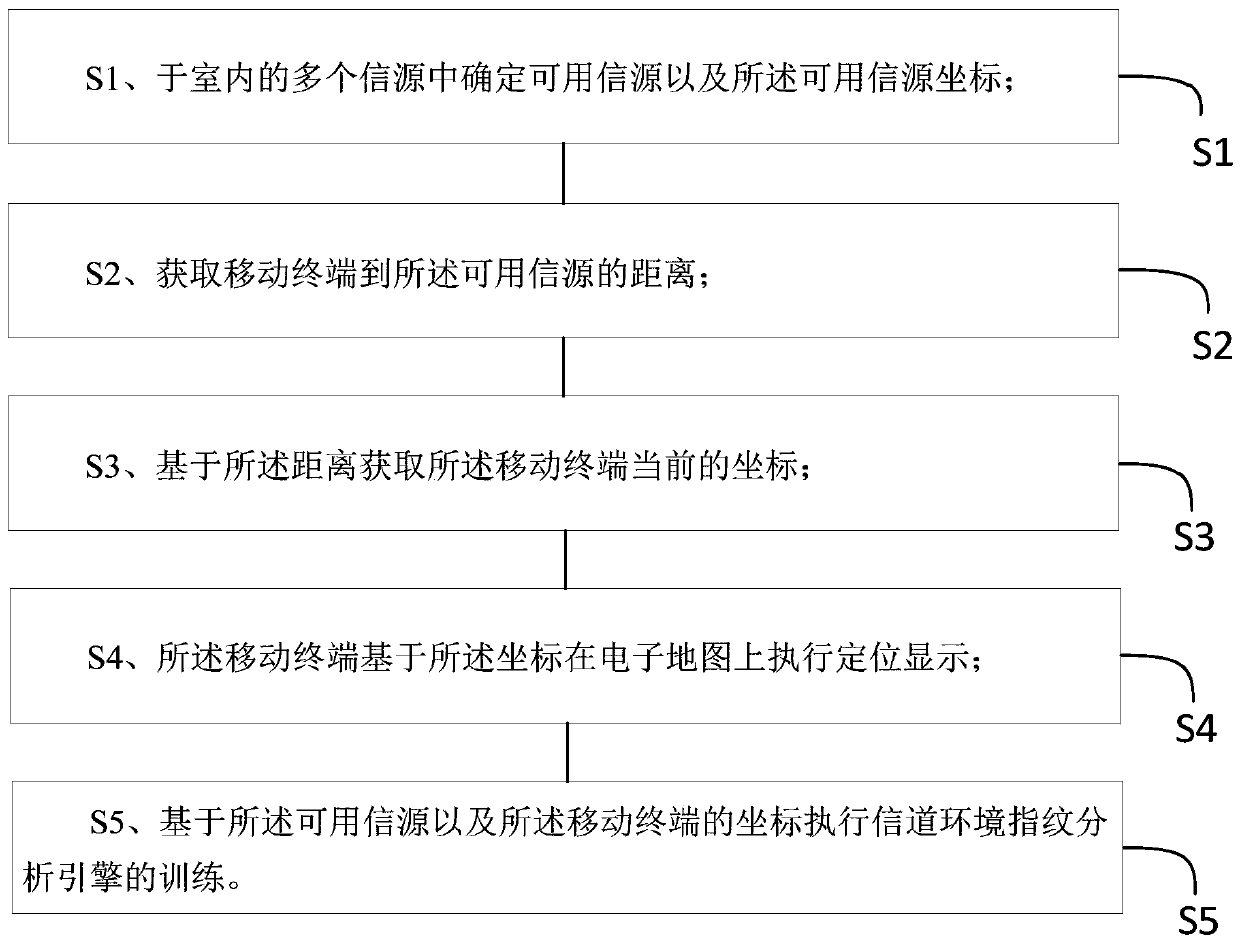

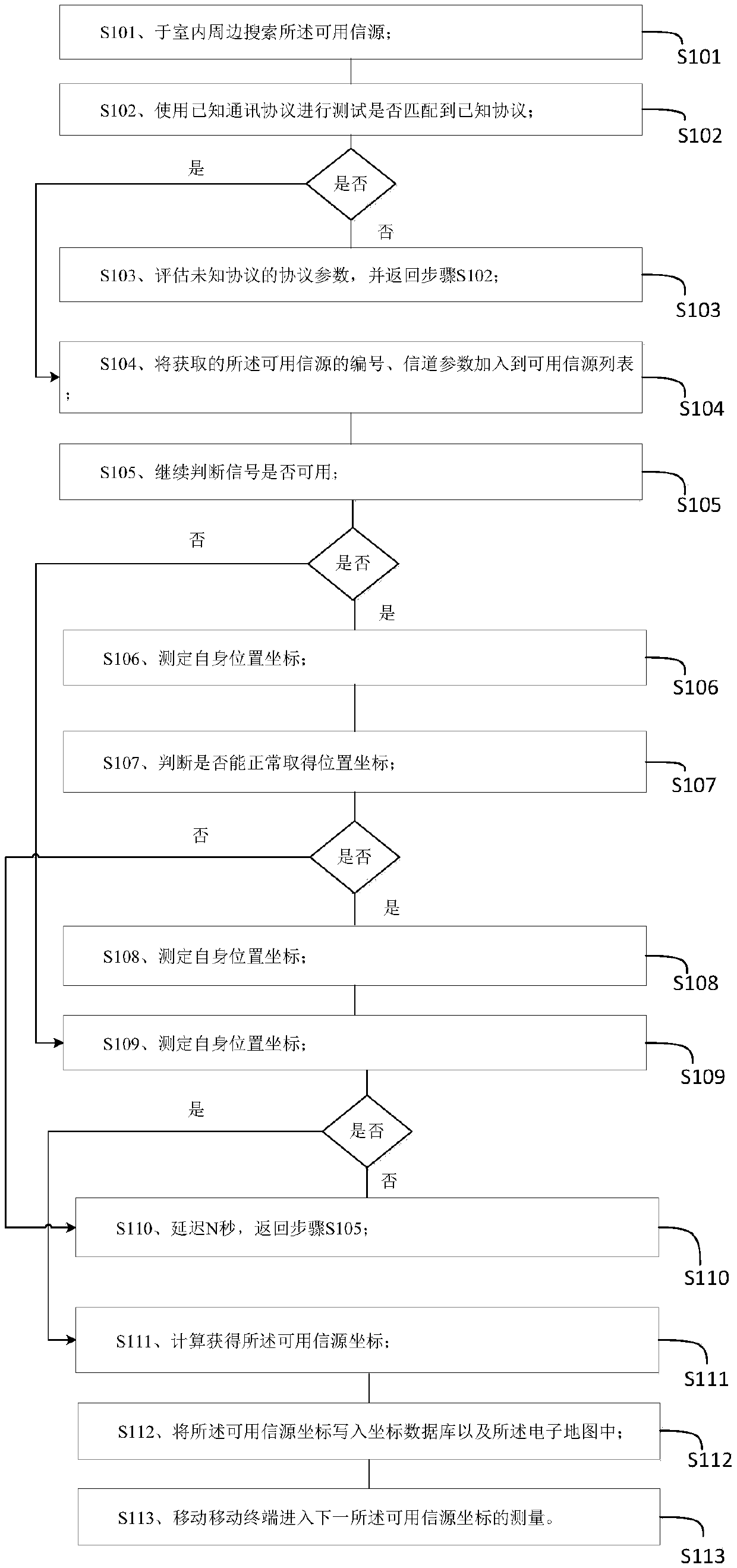

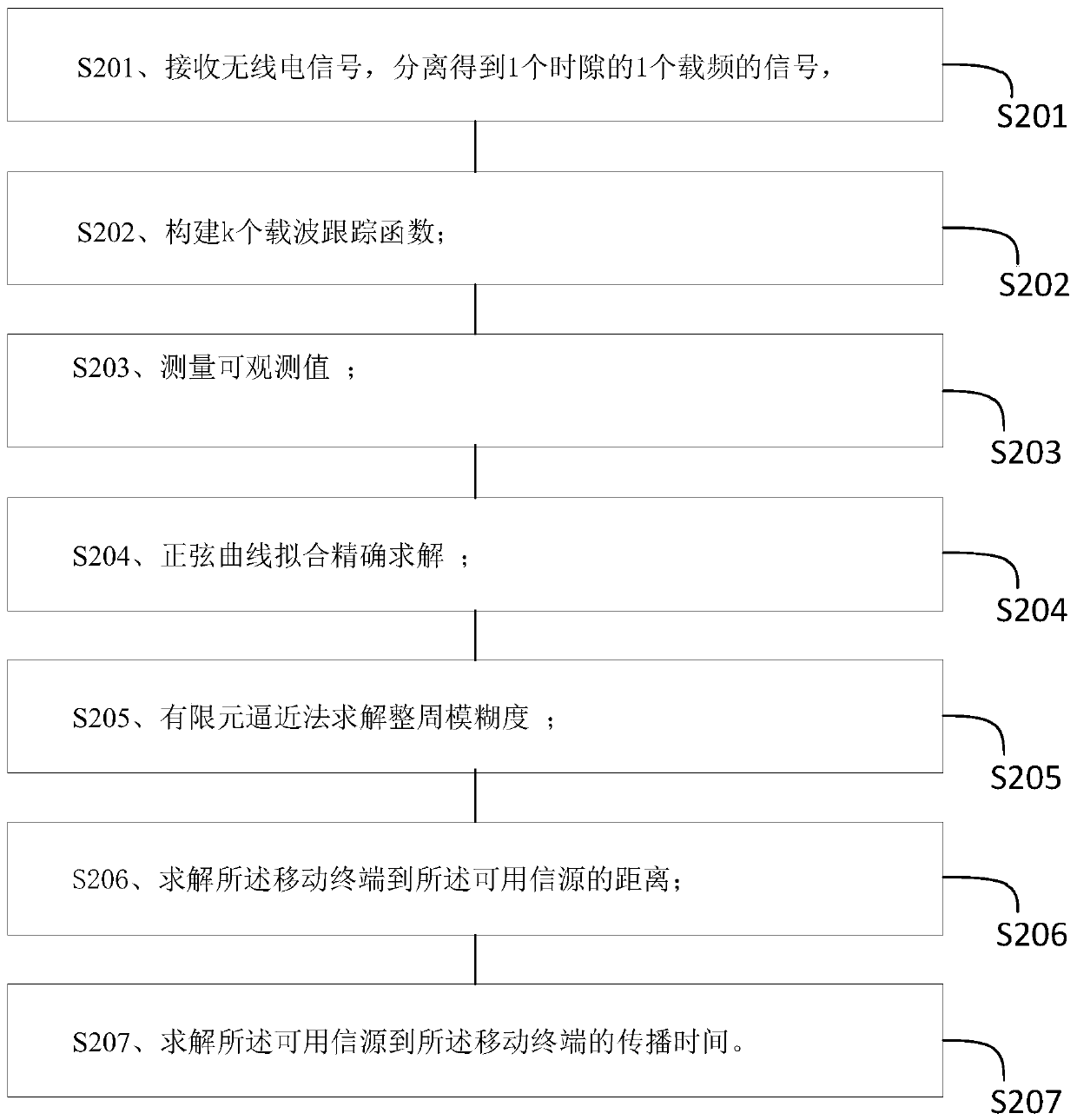

Indoor positioning method and system based on signal multipath propagation measurement

ActiveCN110351655AHigh accuracy of pseudo-range measurementExcellent theoretical distance measurement accuracyParticular environment based servicesPosition fixationCost burdenOperational costs

The invention discloses an indoor positioning method and system based on signal multipath propagation measurement, and the method comprises the following steps: S1, determining an available signal source and the coordinates of the available signal source from a plurality of indoor signal sources; S2, obtaining the distance from the mobile terminal to the available information source; S3, acquiringa current coordinate of the mobile terminal based on the distance; S4, enabling the mobile terminal to execute positioning display on an electronic map based on the coordinates; and S5, executing training of a channel environment fingerprint analysis engine based on the available information source and the coordinates of the mobile terminal. The technical scheme has the beneficial effects that the precision of measuring the pseudo distance between the mobile terminal and the available information source is high; positioning is realized by adopting public visible base stations and public visible radio signals, such as LBS, WiFi, WiMAX, FM, ZigBee and other fixed base station signals, access authorization of a base station owner is not needed, infrastructure construction investment and energy consumption are not increased, and operation cost burden is not increased.

Owner:BORUITAIKE SCI & TECH NINGBO CO LTD

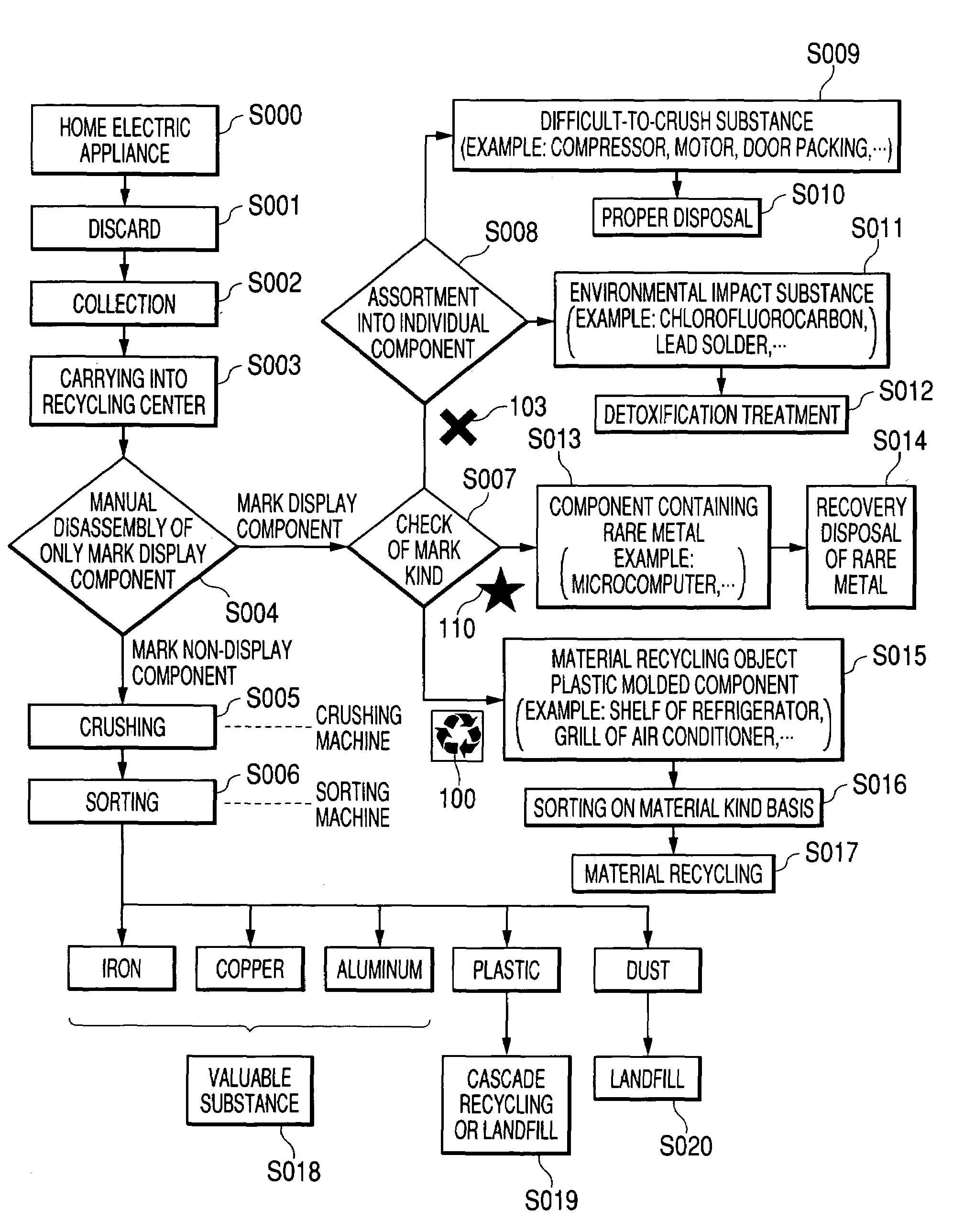

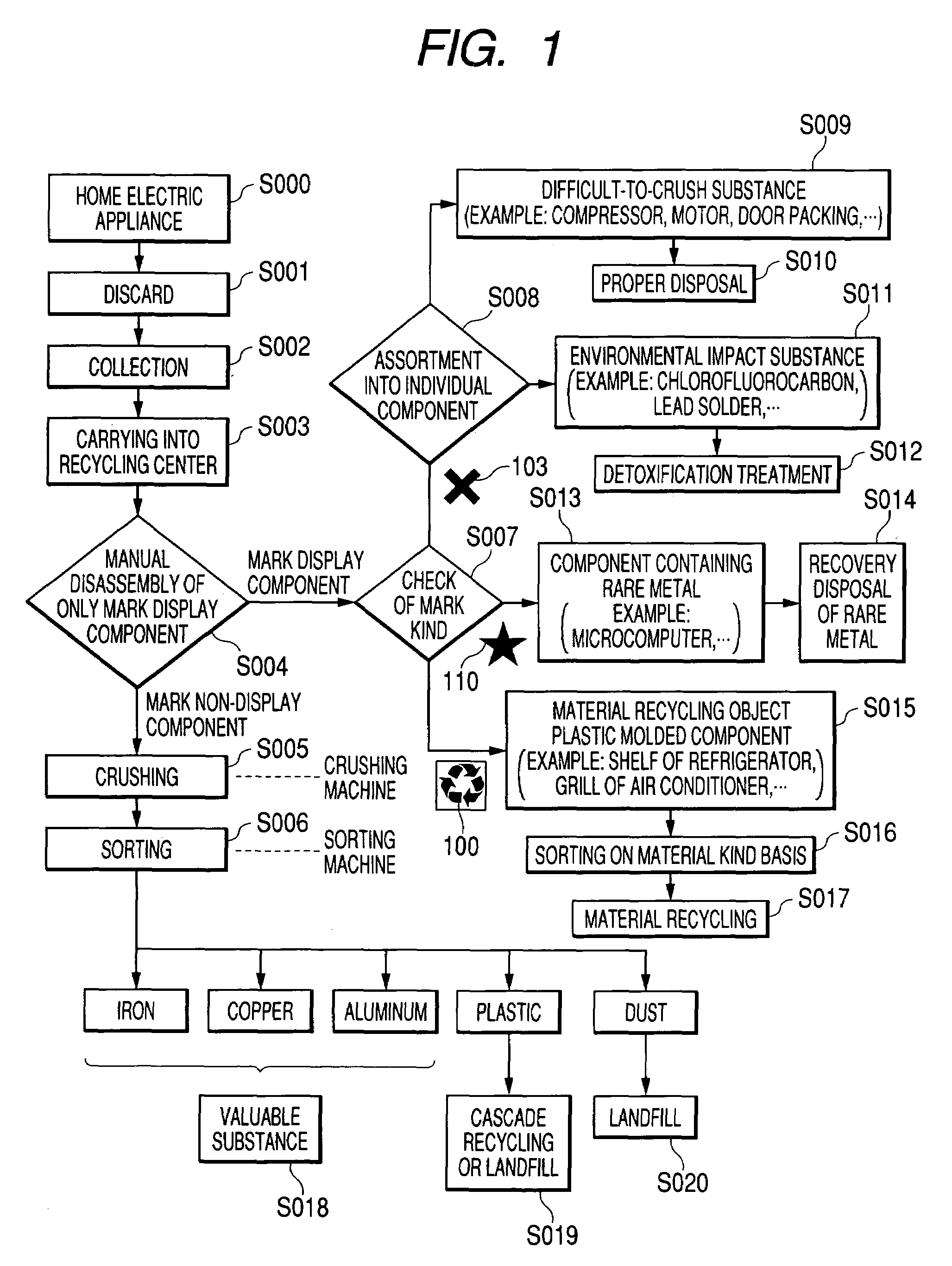

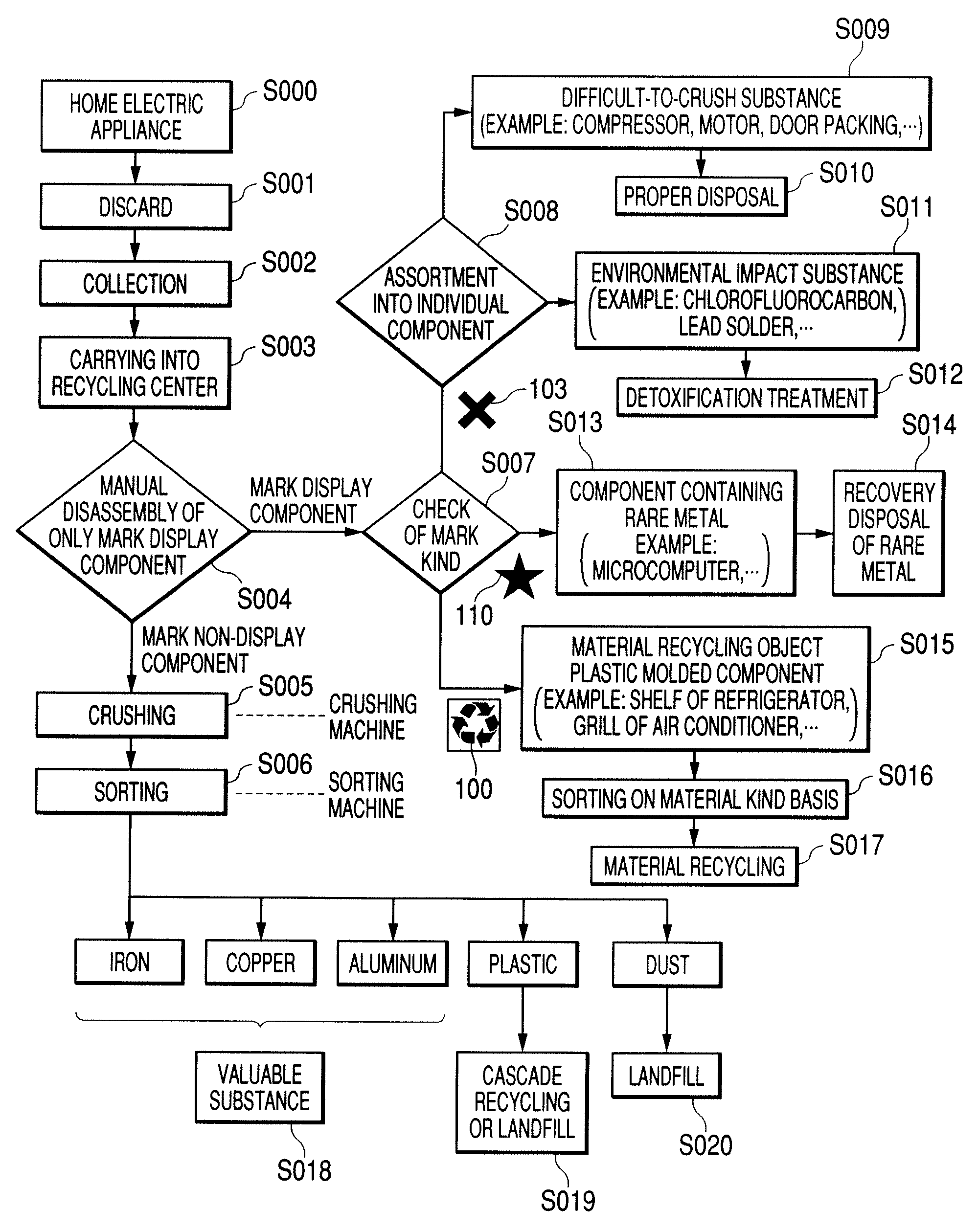

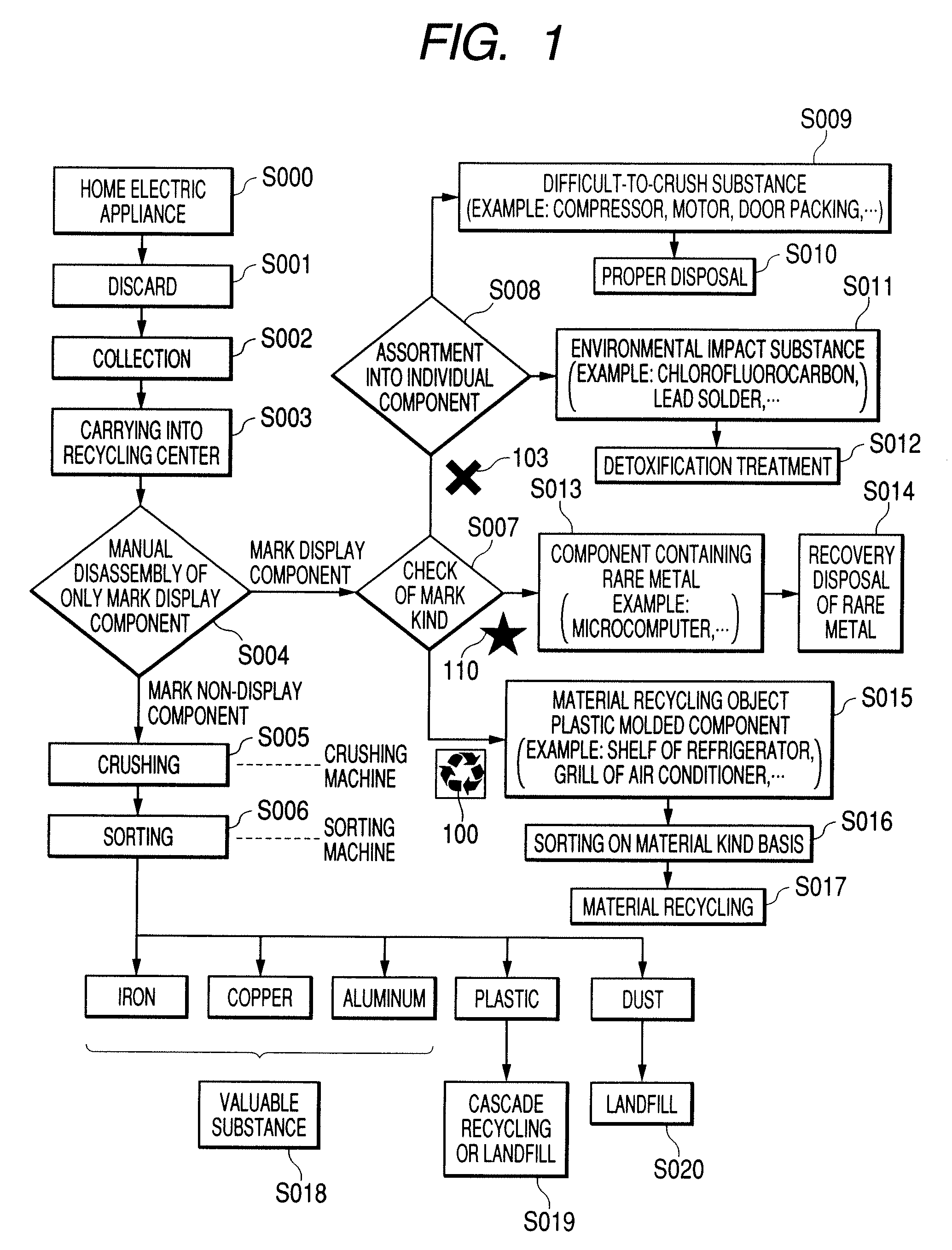

Recovery method for an electric appliance

InactiveUS7318265B2Avoid failureLow costSolid waste disposalPlastic recyclingRecovery methodCost burden

A mark is displayed to a manually scrapped component capable of being disassembled manually without disassembling or crushing by machine at the time of discard or recovery of an electric appliance after use, and the manually scrapped component is manually scrapped from a product, and in the case of crushing by machine thereafter, the mark display is a mark capable of separation into plural kinds of substance on which a cost burden is imposed and valuable substance after recovery, and scrapping can be performed easily at low cost.

Owner:MITSUBISHI ELECTRIC CORP

Long shelf-life and refrigerated live bacterium yogurt and preparation method thereof

InactiveCN106376644AExtended shelf lifeLong refrigerated shelf lifeMilk preparationCost burdenWhey protein powder

The present invention discloses a long shelf-life and refrigerated live bacterium yogurt and a preparation method thereof. Each 1L of the above long shelf-life and refrigerated live bacterium yogurt comprises the following raw material components: 20-100 grams of white sugar, 500-900 grams of fresh milk or 50-130 grams of milk powder, 2-20 grams of concentrated whey protein powder, 2-40 grams of concentrated milk protein, 0.1-11 grams of thickening agent, 0.1-1.0 gram of sweetener, 0.05-1.0 gram of sodium citrate, 0.5-1.5 grams of edible essence, 0.05-0.15 gram of lactic acid bacteria, and water as the balance. According to the technical scheme of the invention, the shelf life of the refrigerated live bacterium yogurt is as long as 90 days, while the mouth feel of the refrigerated live bacterium yogurt can be kept stable. Meanwhile, the selling radius of the refrigerated yogurt can be extended, and the production and marketing cost burden of a production manager is relieved. Moreover, the refrigerated live bacterium yogurt provides authentic yogurt nutrition and good taste for consumers in remote areas.

Owner:HANGZHOU WAHAHA TECH

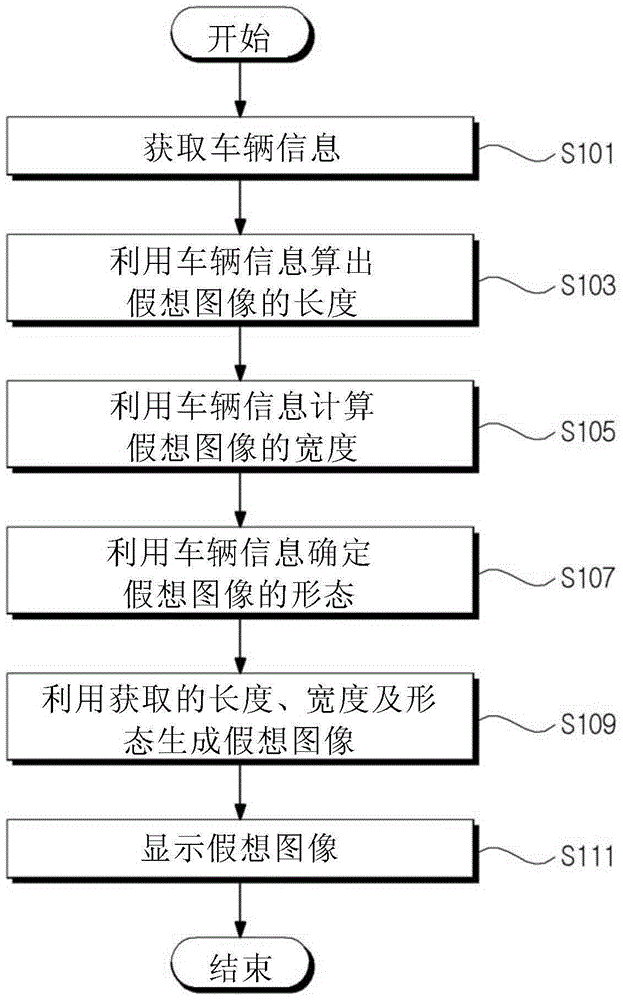

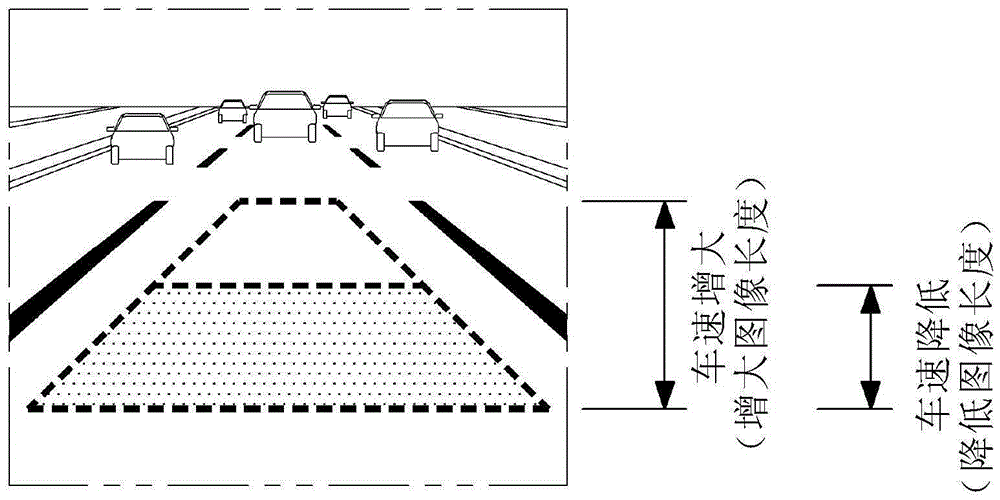

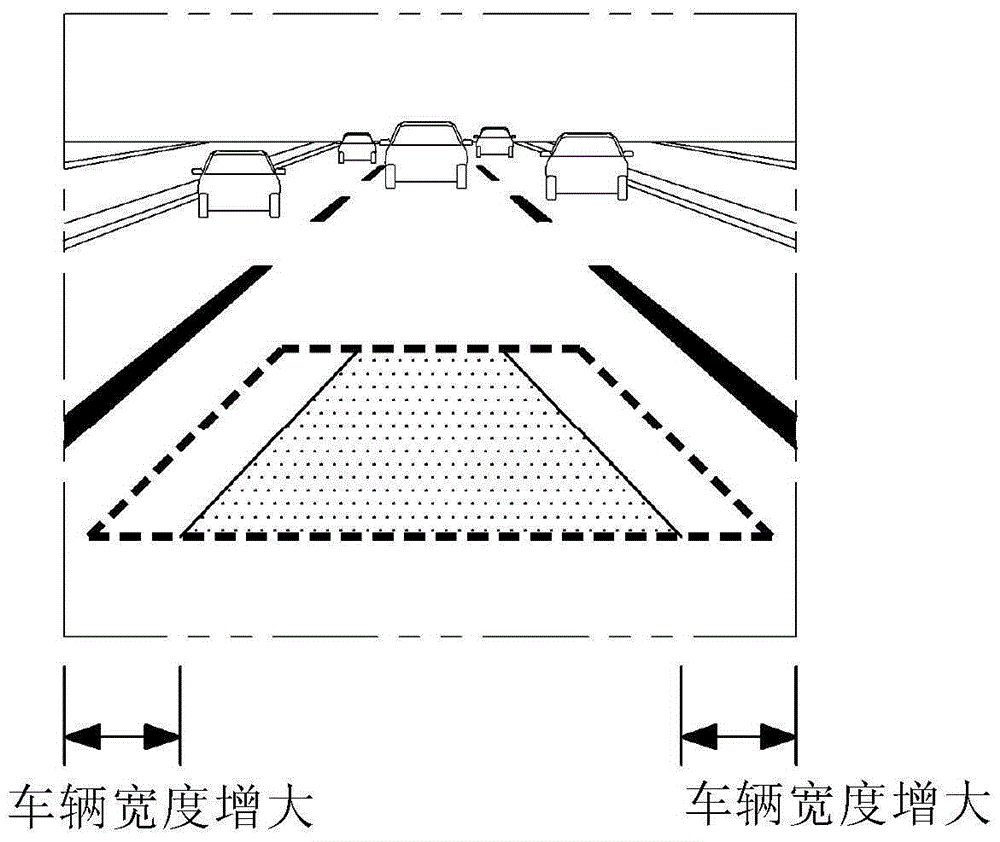

Driving support image display method

ActiveCN105398379AAccurate identification of widthEasy to judge narrow roadOptical viewingHypothesisCost burden

The invention discloses a driving support image display method including a step of obtaining vehicle information of a vehicle; a step of calculating the length of a hypothesis image for driving support by using the vehicle information; a step of calculating the width of the hypothesis image by using the vehicle information; a step of determining the form of the hypothesis image by using the vehicle information; and a step of displaying the hypothesis image so as to be apt to recognize by a driver. According to the driving support image display method of the embodiment, the vehicle width on a road can be accurately recognized, thus it is easy to judge a narrow rod or whether to enter the road. Rear-collision accidents between opposite vehicles can be effectively prevented, and the vehicle weight or cost burden cannot increase.

Owner:HYUNDAI MOBIS CO LTD

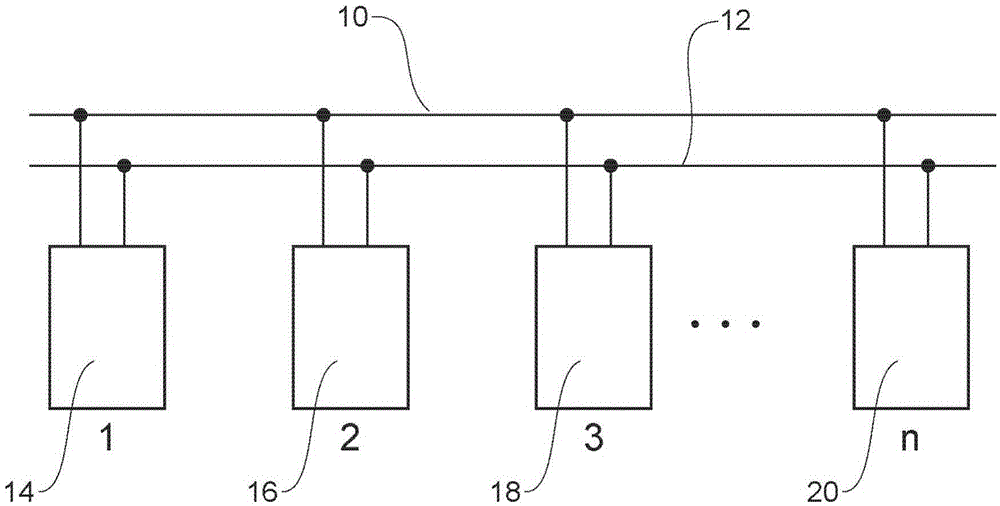

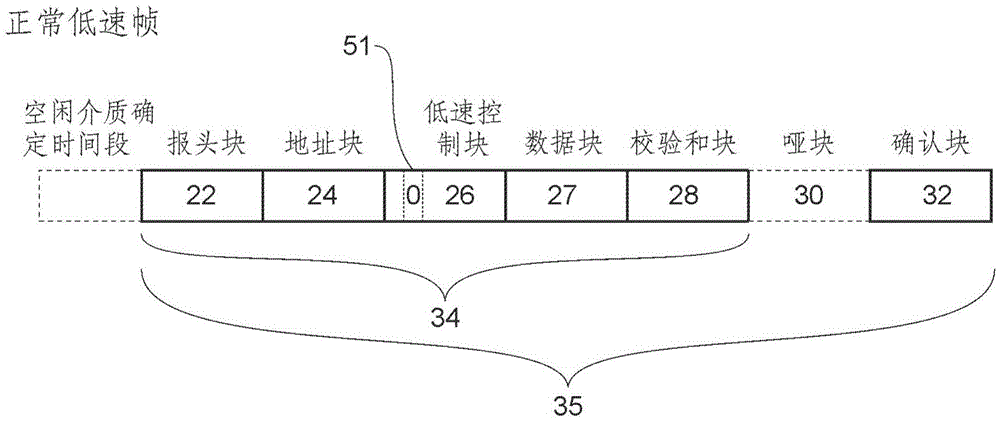

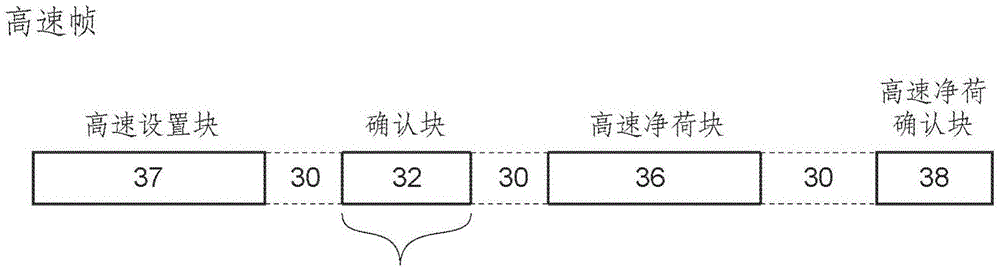

Variable data rate control protocol

There is disclosed a protocol which can use the existing network bandwidth limitations for transmission during at least the bus contention period after which the remaining portion of the data should be collision-free but allow for a choice of signalling rate within the frame after that bus contention period for the payload data to be transmitted, thus allowing the use of a different data rate in parts of a frame. Additionally there is disclosed advantages to be gained by making best use of available but otherwise not used network bandwidth capability at different parts of the transmission of a frame, such that the protocol enhancement should be compatible with existing installed devices and associated controllable arrangements, so that a system existing in a network can be upgraded, by adding one or more of the devices and associated controllable arrangements which can transmit and receive both the original standard (typically lower) data rate as well as the newer (typically higher) data rate transmissions, at the convenience of the owner of the network without a cost burden associated with replacement or the upgrading of all existing devices or associated controllable arrangements.

Owner:SCHNEIDER ELECTRIC (AUSTRALIA) PTY LTD

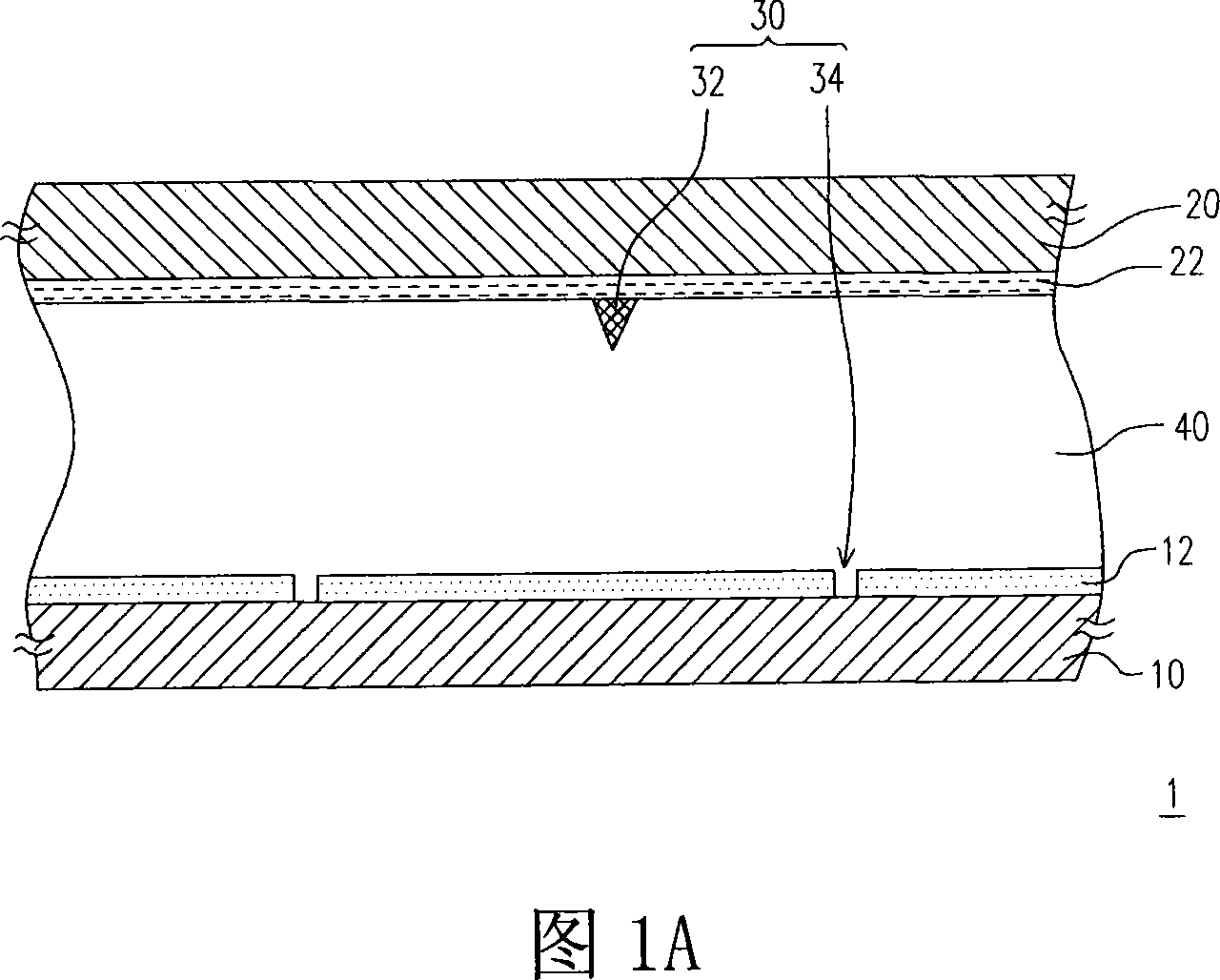

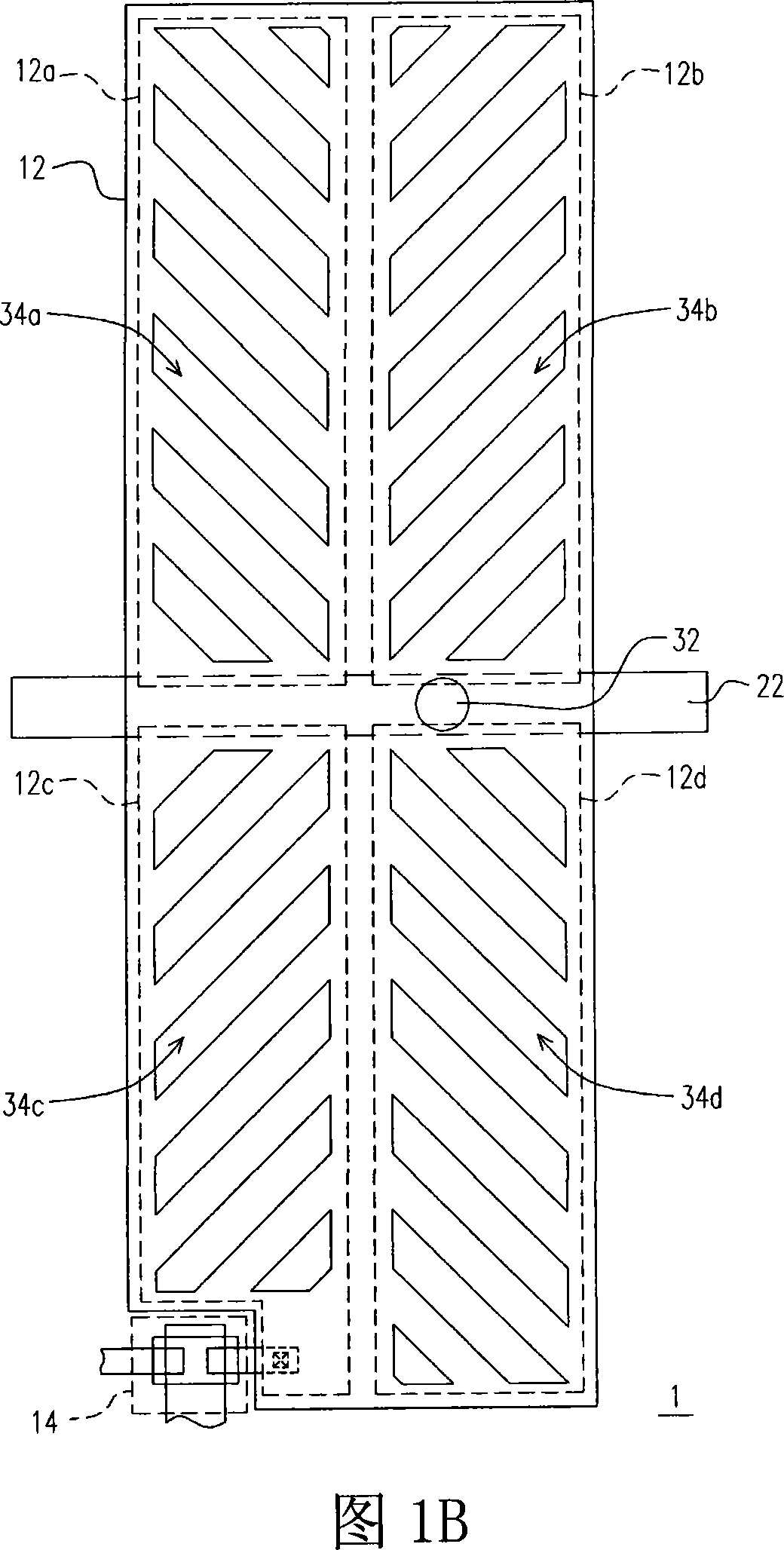

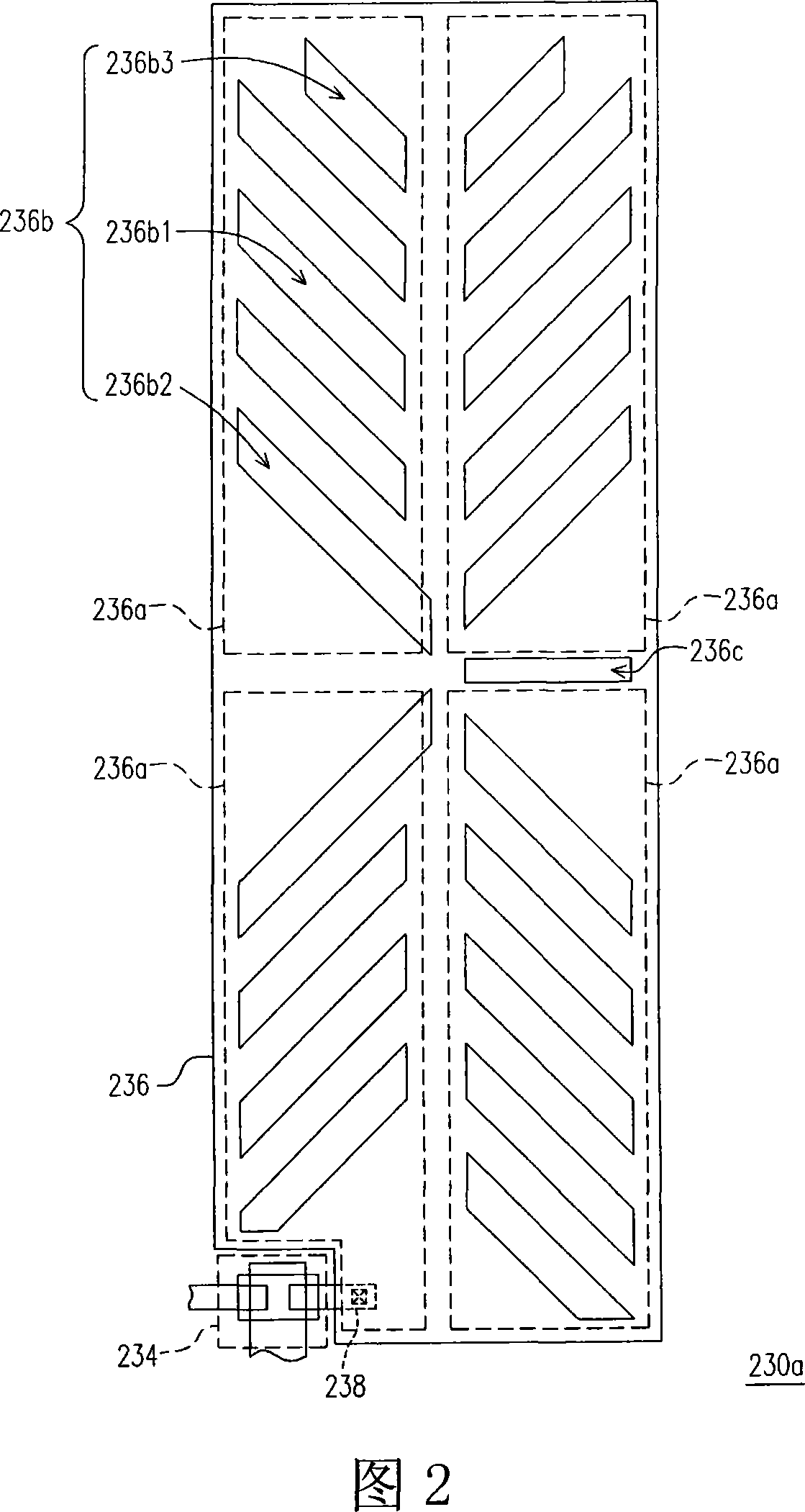

Image element structure and LCD with the same

ActiveCN101221332AStable arrangementImprove display qualityNon-linear opticsCost burdenElectrical connection

The invention discloses a pixel structure and a liquid crystal display having the same, wherein the pixel structure comprises an active element and a pixel electrode. The pixel electrode is in electrical connection with the active element, and a pixel electric area is provided with a plurality of alignment regions. Each alignment region of the pixel electrode is provided with a group of alignment slits which are opposite in alignment direction; the groups of alignment slits include a plurality of first alignment slits which are the same in length and account for the largest number. At least one group of alignment slits also comprises at least one second alignment slit of a length larger than that of each first alignment slit. The designed slits in the pixel structure of the invention can effectively control the arrangement of liquid crystal molecules and improve the condition of inconsistent brightness of pixels displaying the same gray scale image. In addition, the slits in the pixel structure of the invention can be driven by the prior drive circuit and have a process which is the same as the prior process in manufacture, thereby not resulting in cost burden.

Owner:AU OPTRONICS CORP

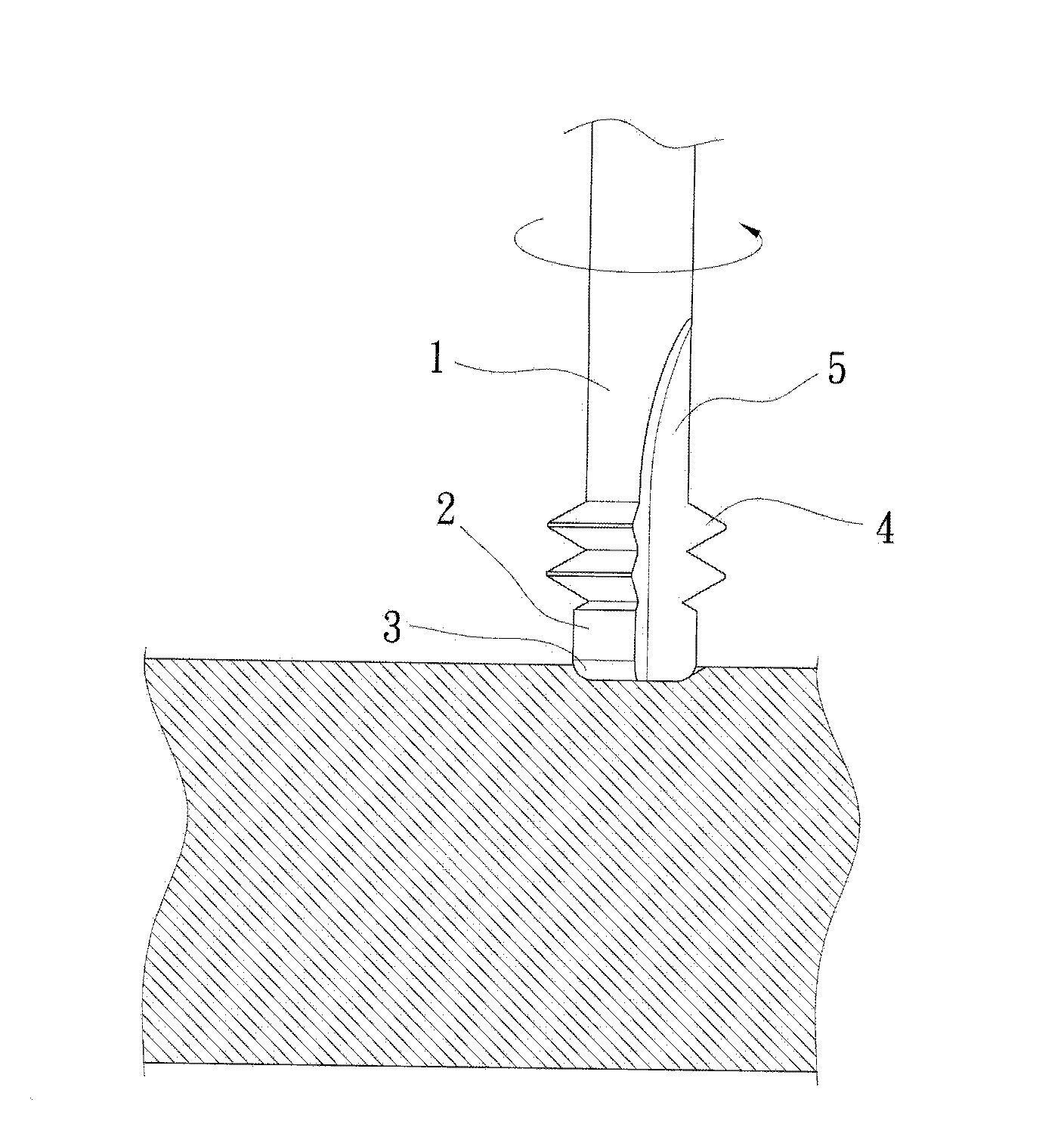

Cutter structure

InactiveCN103157845AReduce man-hour lossAvoid cost burdenThread cutting toolsMilling cuttersNumerical controlCost burden

The invention relates to a cutter structure which comprises a cutter main body. A milling cutter portion is arranged on the cutter main body, a chamfering portion is formed on the peripheral edge at the front end of the milling cutter portion, and a thread cutter portion is formed on the cutter main body and located behind the milling cutter portion in a connected mode. Therefore, the chamfering portion in the front of the cutter main body is utilized for achieving an equidistant chamfering function through numerical control, then a numerically-controlled spiral curve equation is utilized for driving a cutter edge of the milling cutter portion to mill a bottom hole, and lastly, the thread cutting portion is used for carrying out a thread milling process continuously, so that forming operation of a threaded hole can be finished once. During implementation, working hours consumed for changing cutters cumbersomely in a machining process can be effectively reduced, errors generated due to recalibration when the cutters are changed for multiple times can be prevented, the cost burden for purchasing the multiple cutters and machine tools can be further avoided, and more specifically, the competitiveness of the present manufacturing industry can be improved, and other substantive benefits can be increased.

Owner:泳捷科技有限公司

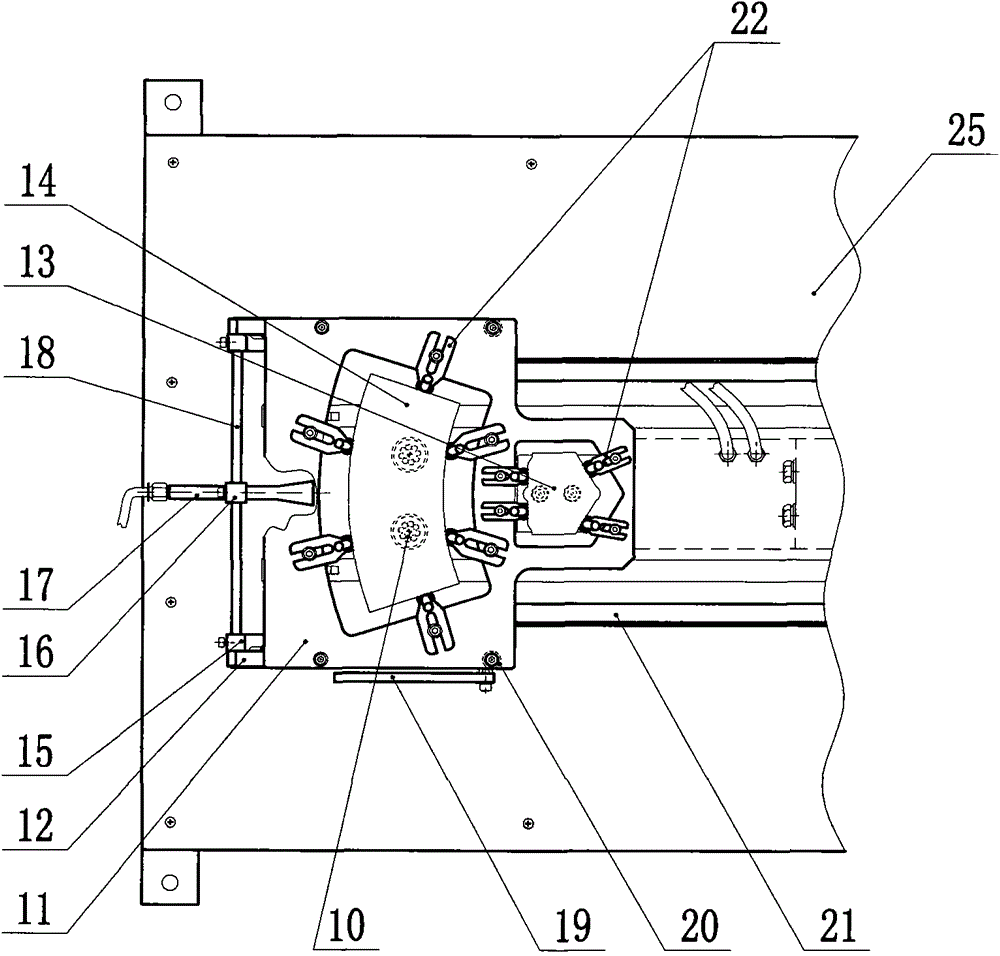

Suction and release double paper mechanism of sticky handle paper cup forming machine

ActiveCN103317776BSolve the problem of hot handsReduce cost burdenPaper/cardboard articlesCost burdenPulp and paper industry

A double paper piece absorbing and releasing mechanism for a pasted handle type paper cup forming machine comprises an absorbing and releasing structure and a stacking structure. A cam rocker drive mechanism is connected with a connecting rod to form the absorbing and releasing structure, the connecting rod is movably connected upwards with a sliding plate, rollers and pins, the sliding plate is sequentially connected upwards with a pipe seat, suction pipes and suction nozzles, and a paper frame plate is arranged above the suction nozzles. The stacking structure mainly comprises the paper frame plate, a paper frame strip, a support leg, a blowing seat, a blowing pipe, a horizontal shaft, a support rod, a frame leg, paper stoppers, paper blocking rods and the like. The paper blocking rods are arranged on the peripheries of a front opening and a rear opening of the paper frame plate, and each paper blocking rod is used for blocking double paper pieces. The double paper piece absorbing and releasing mechanism has the advantages that the double paper pieces are stacked by the aid of a single paper frame, a single cam rocker drives two groups of suction nozzles to move, a paper cup with a handle can be produced once, the problem that the paper cup is too hot to handle is solved, and the cost burden of secondary manufacture is relieved.

Owner:瑞安市胜利机械有限公司

Porcine parvnvirus living vaccine and preparation method thereof

InactiveCN101745106AImproving immunogenicityExtended shelf lifeAntiviralsAntibody medical ingredientsRetention periodCost burden

The invention relates to a porcine parvnvirus living vaccine and a preparation method thereof. The living vaccine is prepared by adopting a PPVS-1A strain (the HA valence is not less than 29, and the TCID50 is not less than 107.0 / ml) to obtain a cell culture through being inoculated with a swine testis (ST) subculture cell growing well, adding a suitable stabilizing agent and carrying out freezing vacuum drying. The virus content of each first part of the living vaccine is not less than 105.0TCID50. Compared with the prior art, the porcine parvnvirus living vaccine has good immunogenicity, rapid antibody generation after immunization, high titer and long maintenance time of the generated antibody, long retention period and small immunizing dose. When the porcine parvnvirus living vaccine is used to carry out vaccine injection a plurality of weeks before hybridization, the pregnant sow can maintain strong immunizing power in the easy infection period. The porcine parvnvirus living vaccine is the excellent choice for preventing the porcine parvnvirus. The adopted preparation method has reasonable process and lower cost and greatly reduces the cost burden of the livestock breeding.

Owner:上海佳牧生物制品有限公司 +1

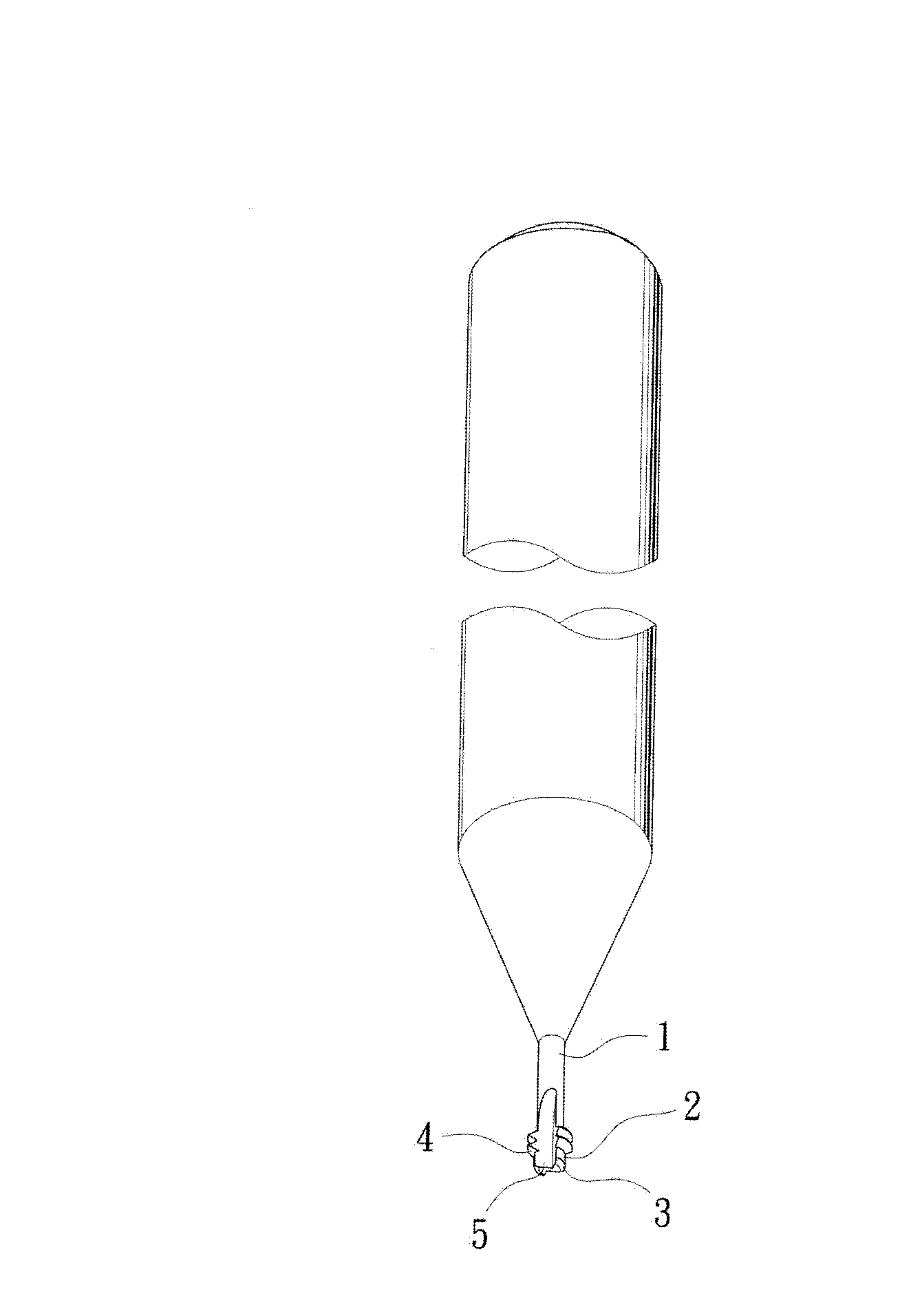

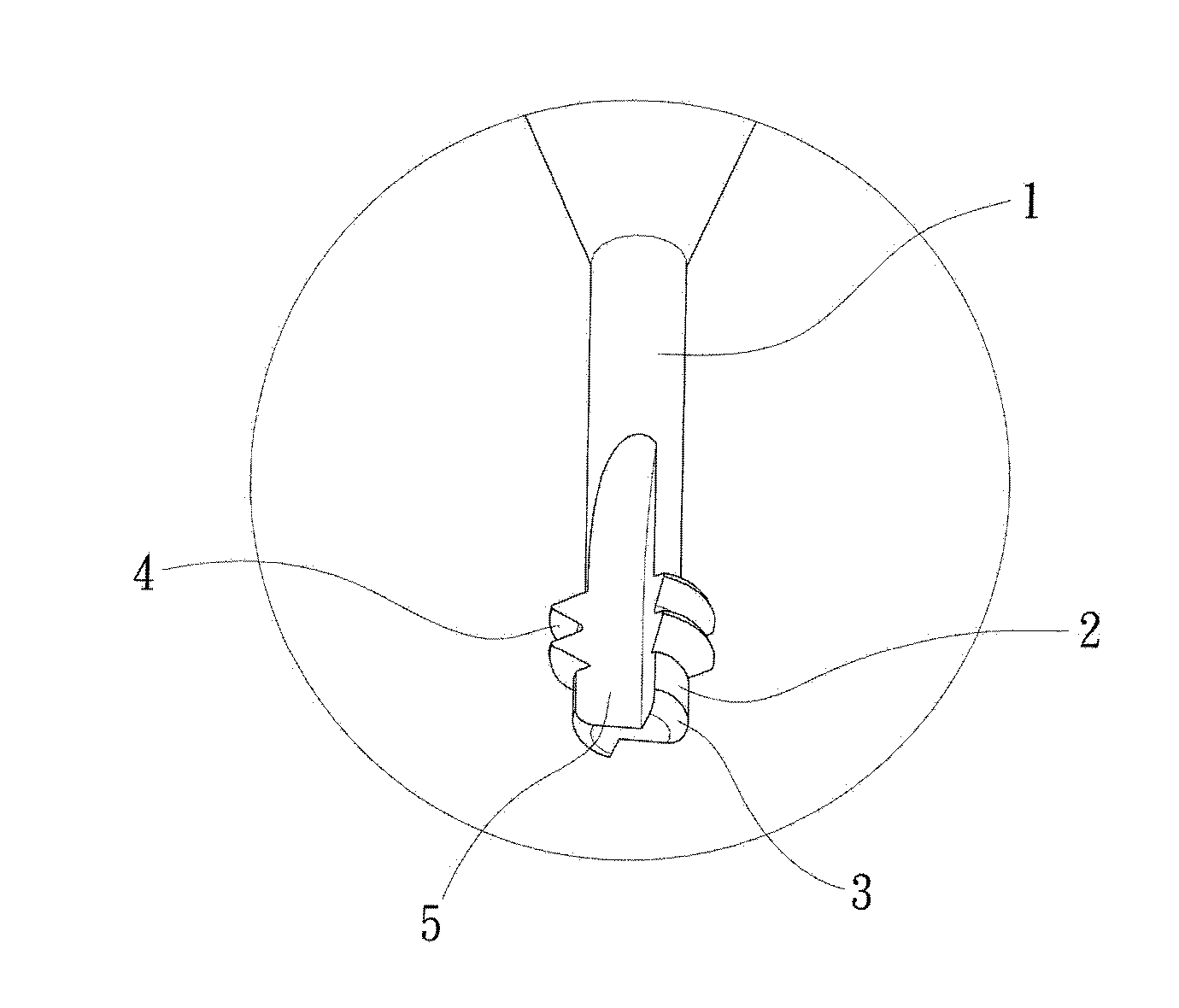

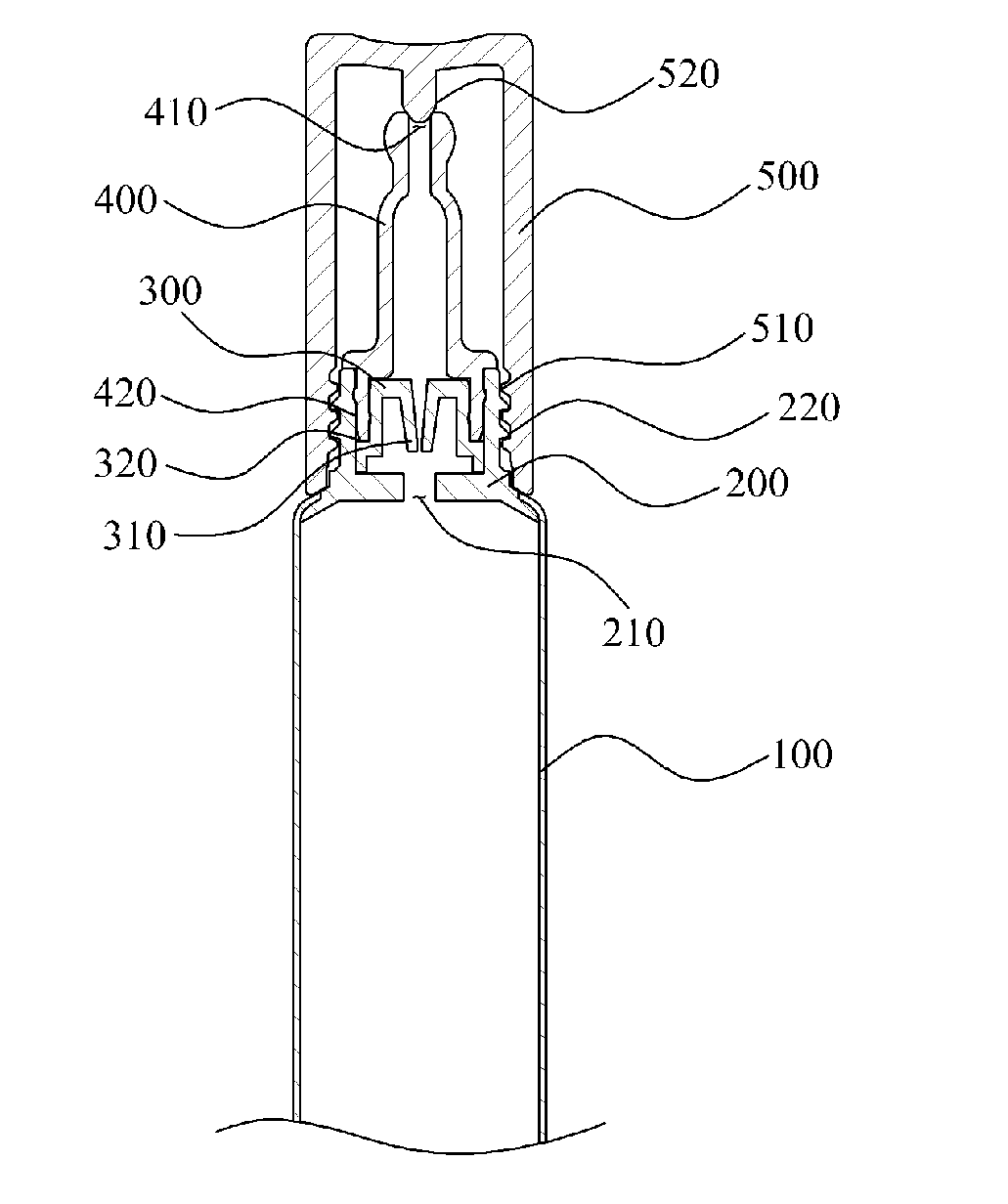

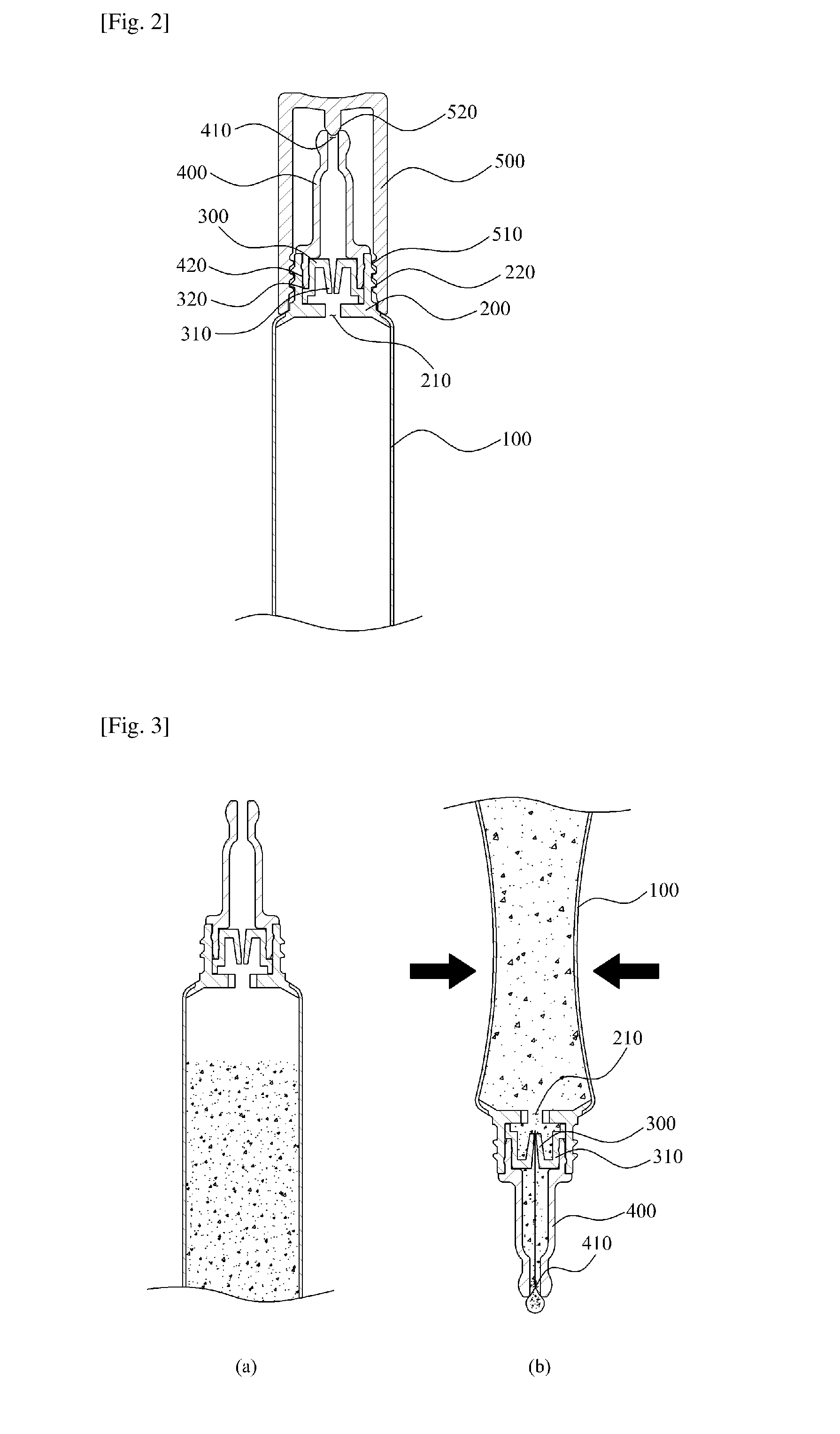

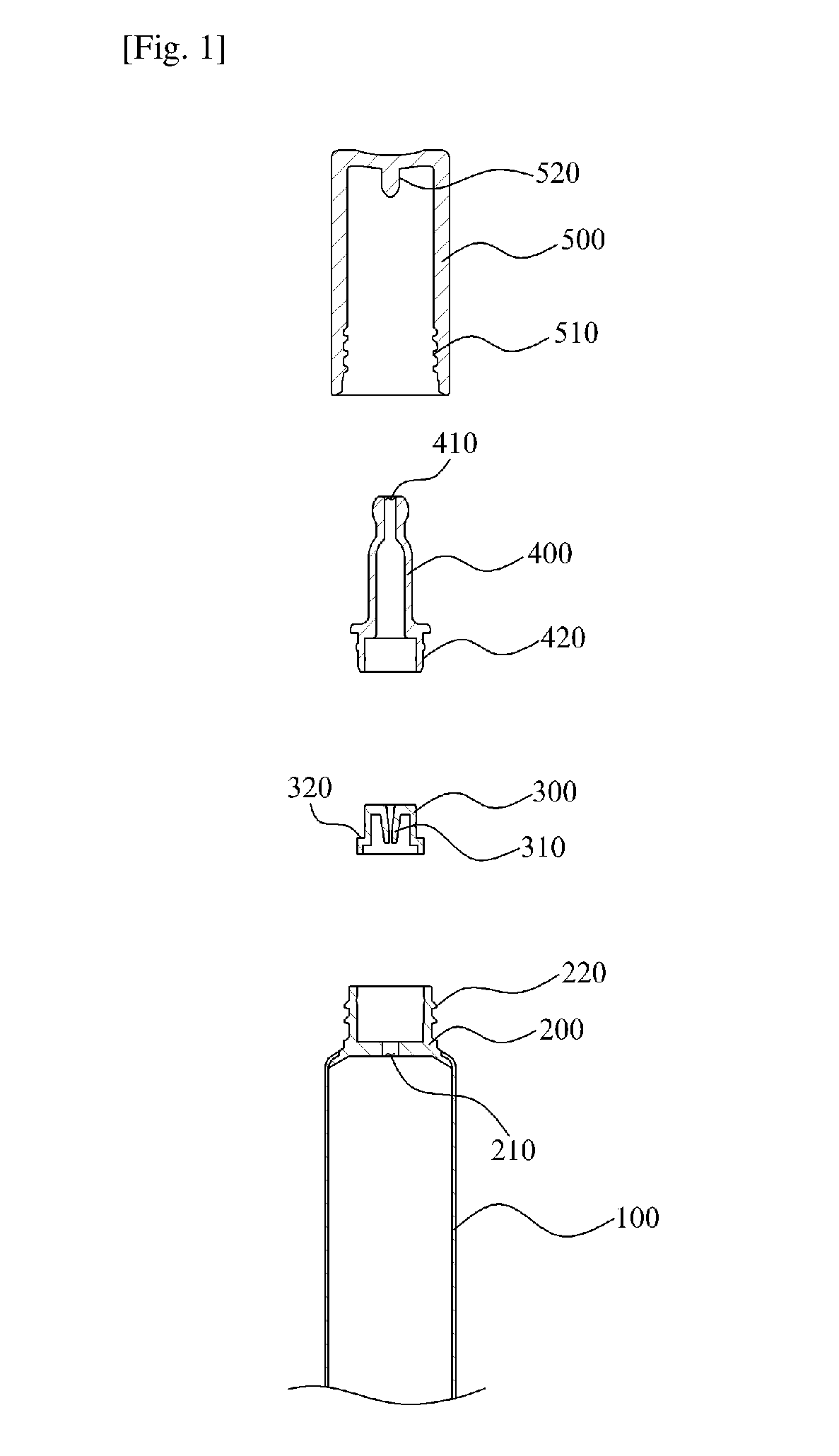

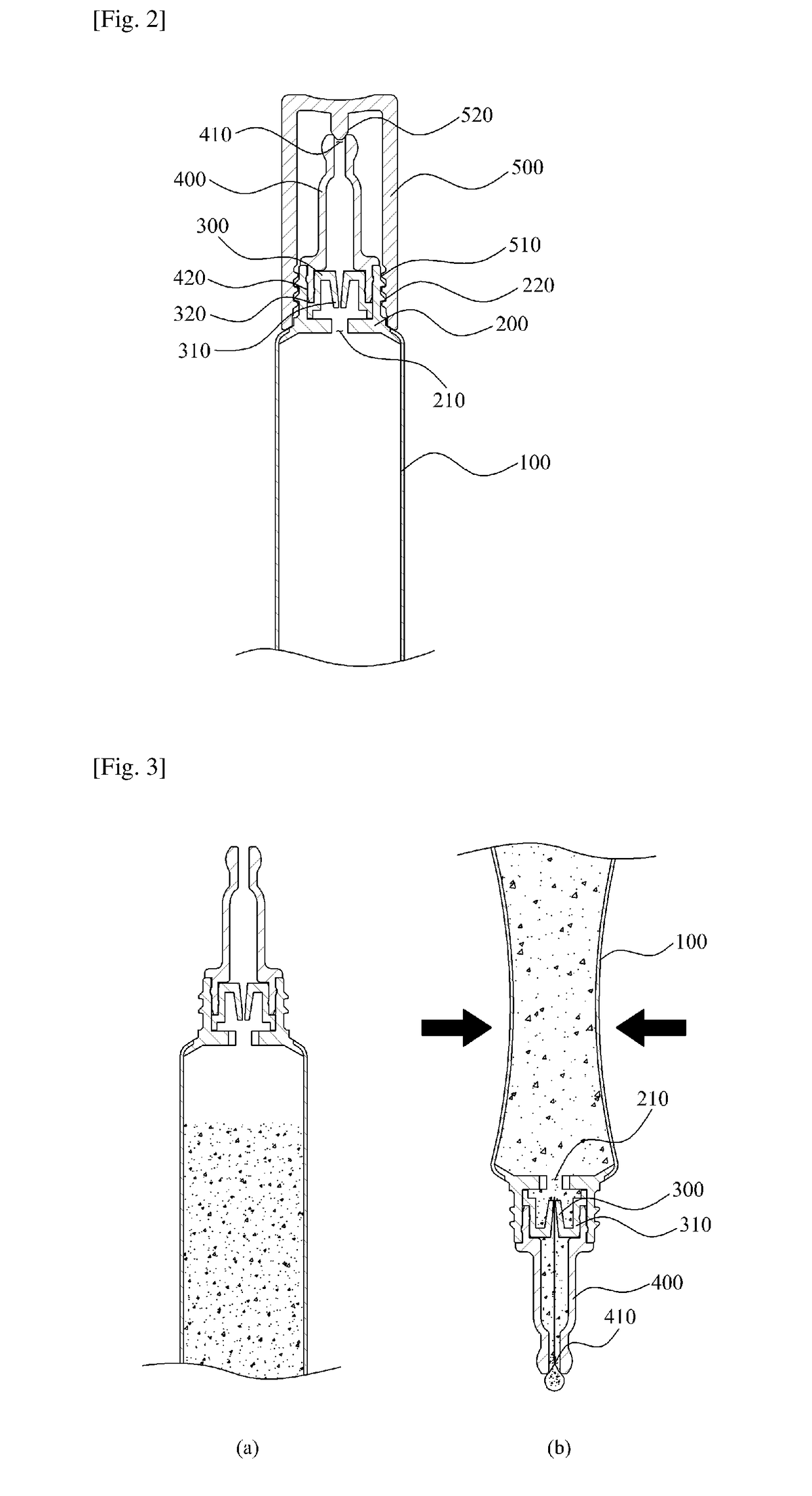

Tube-Type Cosmetics Container for Discharging Liquid Contents in Form of Droplet

ActiveUS20160272381A1Reduce cost burdenShorten production timeClosures with discharging devicePackaging toiletriesCost burdenTubing types

Provided is a tube-type cosmetic container which discharges a liquid content in a form of droplet. The tube-type cosmetic container reduces the cost burden in accordance with shortening of the manufacturing time and reducing cost, by allowing a liquid content to be discharged in a form of droplet through a simple content discharging structure that becomes gradually wider from a lower portion to an upper portion thereof.

Owner:YONWOO CO LTD

Washing method of dish-washing machine

InactiveCN101708119AEasy to useReduce usageTableware washing/rinsing machinesCost burdenProcess engineering

The invention discloses a washing method of a dish-washing machine, which not only can save energy consumption, but also improve the washing efficiency; the washing method of the dish-washing machine can wash the dinnerware in the dish-washing machine as follows: (1) washing liquid is sprayed on the surface of the dinnerware; (2) the washing liquid attached on the dinnerware is heated; (3) the dinnerware is washed. In the invention, as the washing liquid attached on the dinnerware is directly heated, the energy consumption and time consumption can be greatly reduced, the using effect of the washing liquid can be ensured, and the using amount of the washing liquid can be reduced, thereby reducing the cost burden of users and being beneficial to environment protection.

Owner:刘庆

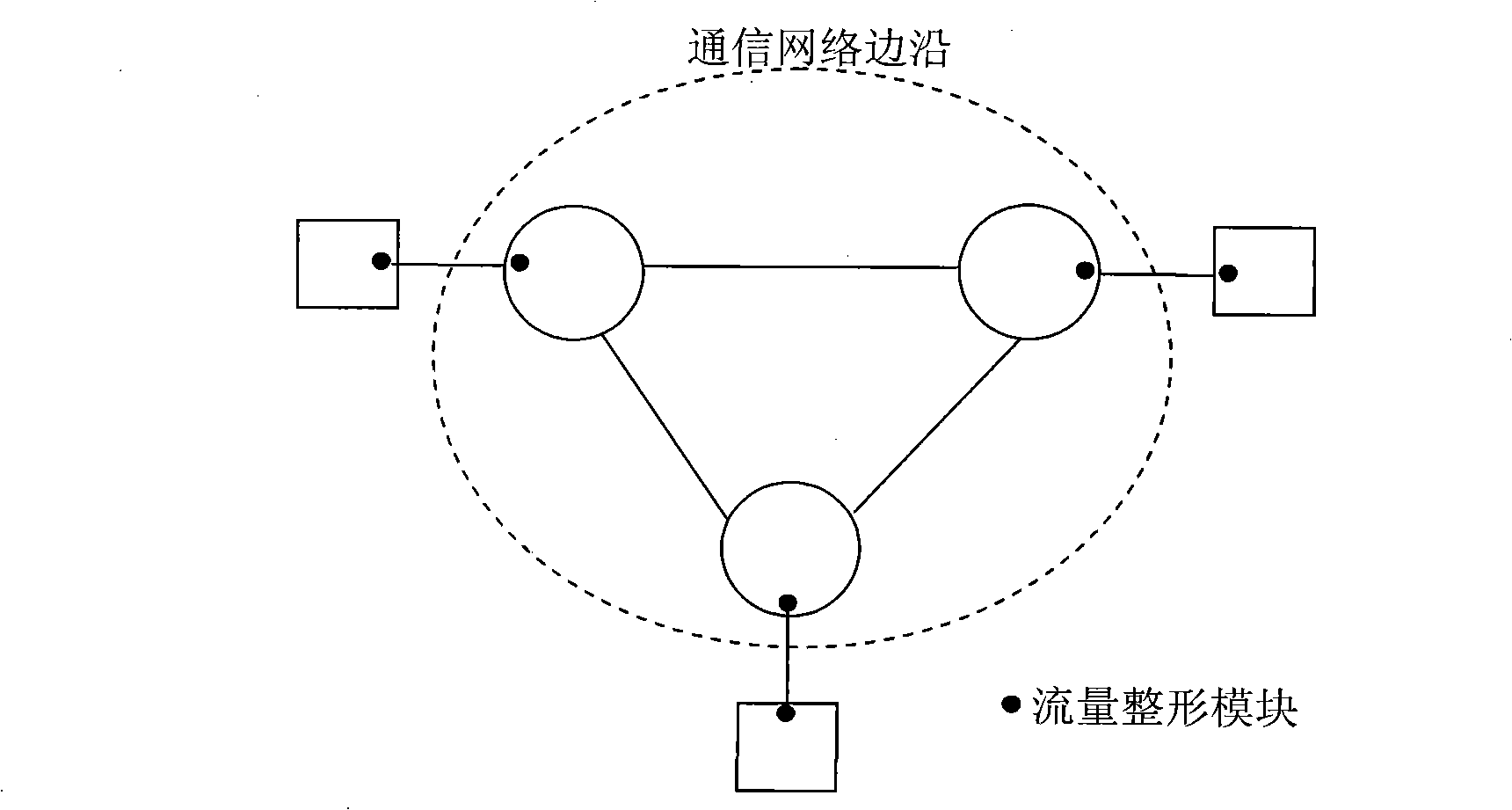

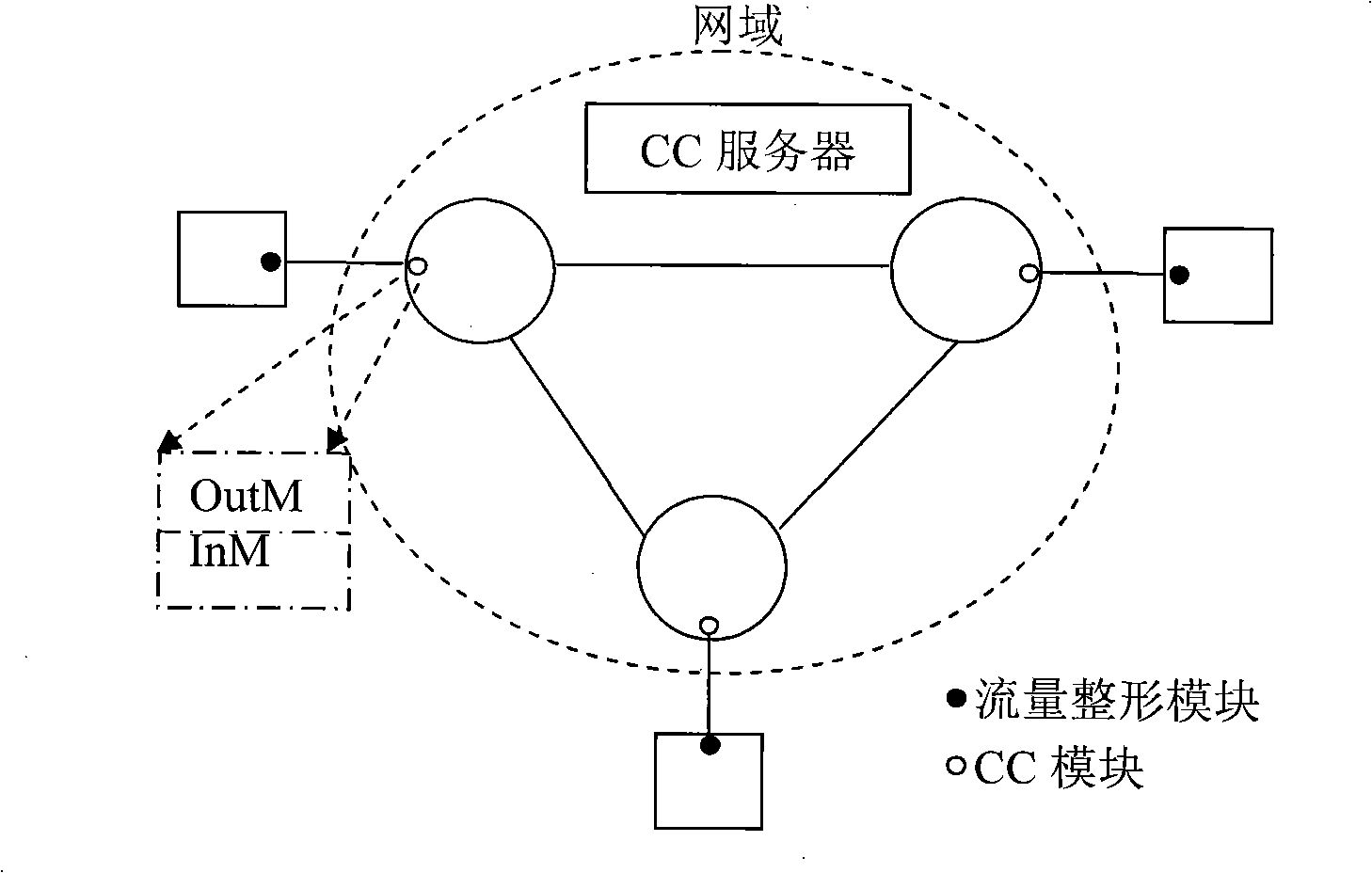

Communication network congestion control method

InactiveCN101296187AOmit the traffic shaping moduleReduce cost burdenData switching networksTraffic capacityCost burden

The invention discloses a congestion control method for a communication network, which pertains to the field of network communication. The method comprises the following steps: when a certain information source point excessively sends data and one or more congestion points are caused in the communication network; each congestion point can generate a series of congestion events which drive a preset responsibility point calculating process. A responsibility point R of the information source point is obtained when the calculation of the time span of a T tempo is accumulated; during a preset appraisal period, the responsibility point R of every T tempo is accumulated, and a total responsibility point U of the information source point is obtained; according to the total responsibility point U and a preset punishing strategy, punishment with sufficient strength is carried out to the information source point so as to force the information source point to limit flow consciously. By establishing a supervision mechanism, the method causes the information source point to limit flow consciously, thus saving a flow shaping module at the edge port of the communication network, eliminating the main cost burden for the whole network to realize congestion control and remarkably lowering realizing cost for promising the communication network of QoS as a whole.

Owner:BEIJING YICHEN COMM TECH INST

Recovery method of electric appliance, electric appliance, information system of electric appliance and recovery apparatus of electric appliance

InactiveUS20070130742A1Avoid failureLow costSolid waste disposalPlastic recyclingRecovery methodCost burden

A mark is displayed to a manually scrapped component capable of being disassembled manually without disassembling or crushing by machine at the time of discard or recovery of an electric appliance after use, and the manually scrapped component is manually scrapped from a product, and in the case of crushing by machine thereafter, the mark display is a mark capable of separation into plural kinds of substance on which a cost burden is imposed and valuable substance after recovery, and scrapping can be performed easily at low cost.

Owner:MITSUBISHI ELECTRIC CORP

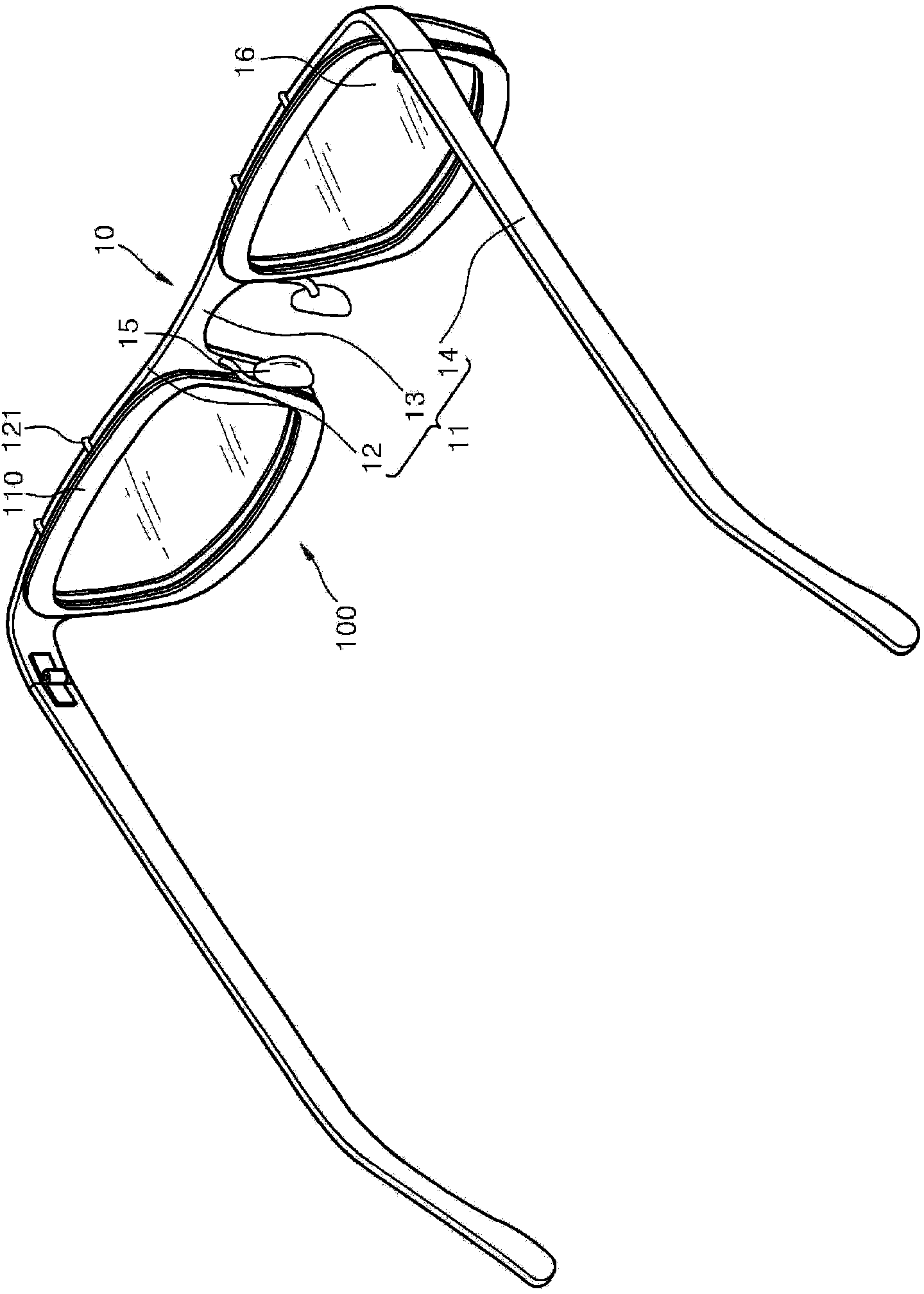

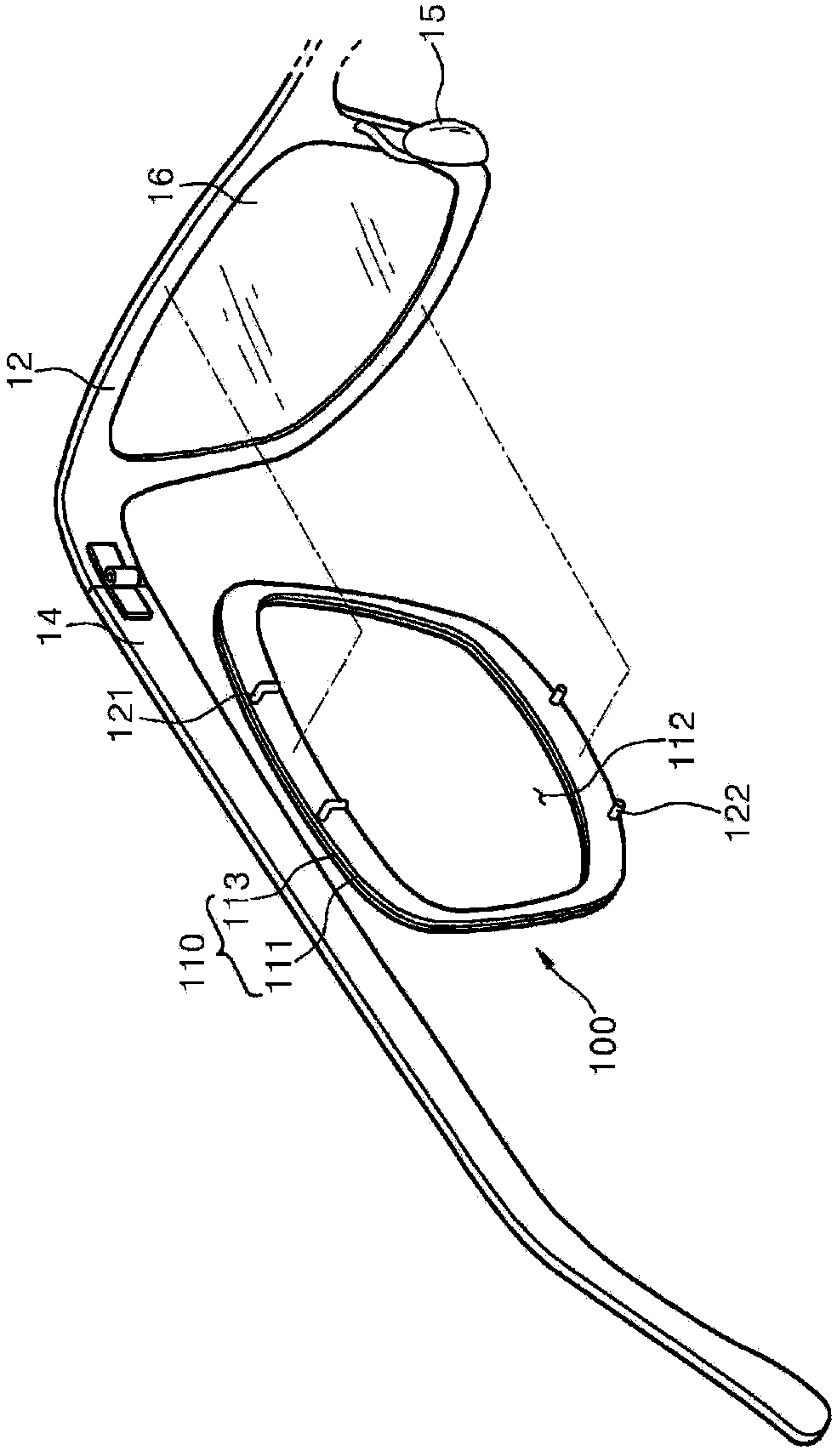

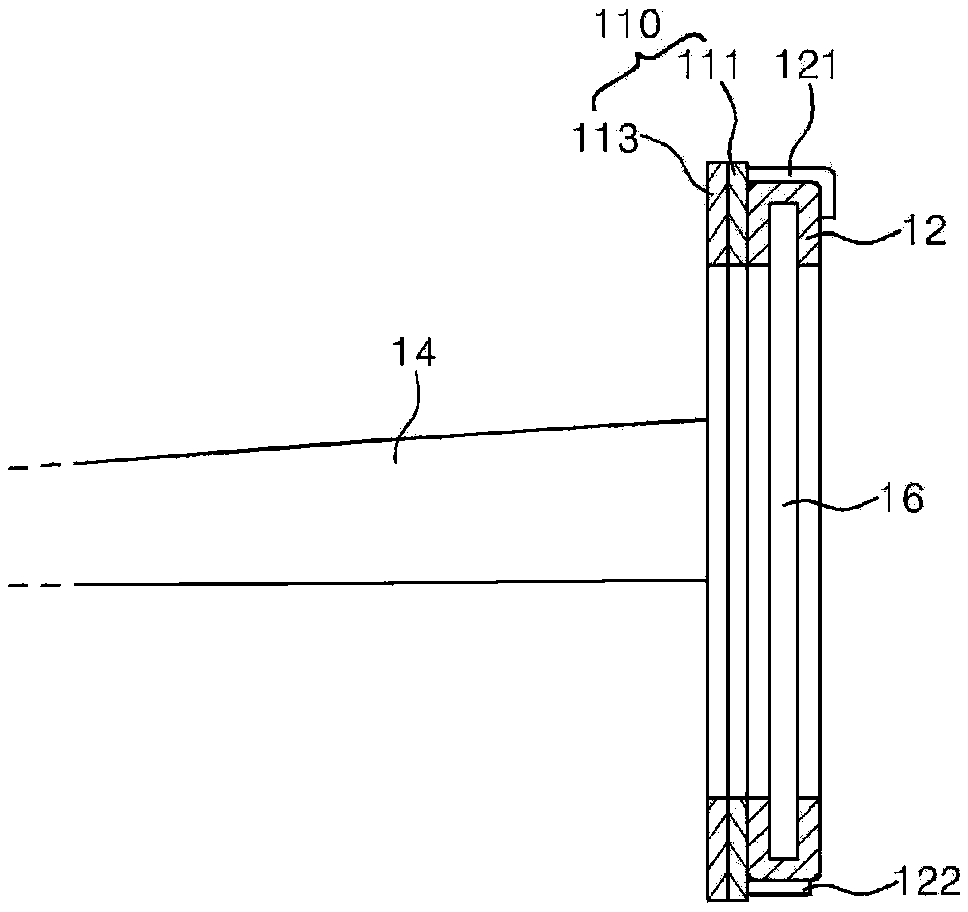

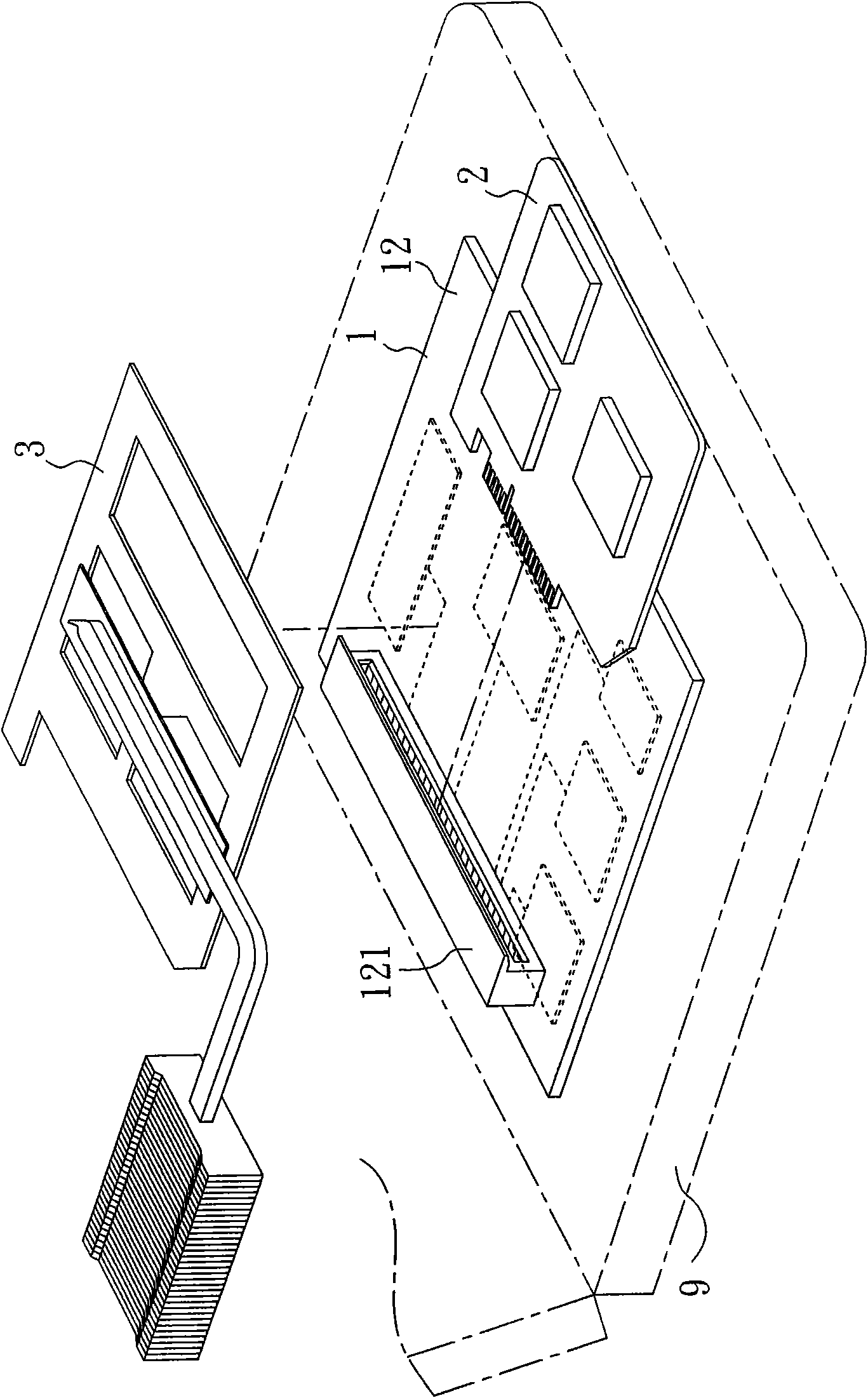

Drug carrier device attachable to glasses

ActiveCN103492017AMinimize the cost burdenMinimize ease of useSpectales/gogglesNon-optical adjunctsCost burdenMetallic materials

Disclosed is a drug carrier device attachable to glasses, which is attached to the glasses and worn with the glasses around the eyes to enable transdermal delivery of drugs for medicinal ingredients for promoting eye fatigue recovery and improving eye diseases. The drug carrier device includes a drug carrier containing medicinal herb ingredients, and a fixing unit for detachably fixing the drug carrier on a frame of glasses. The fixing unit extends from the drug carrier and has a fixing loop whose end portion is bent to be hooked on frame of the glasses. The frame of the glasses is made of a metal to be magnetically coupled to a magnet and the fixing unit includes a permanent magnet magnetically coupled to the frame of glasses. The drug carrier device is attached to the glasses to enable drugs to penetrate into the skin around the eyes of the wearer during everyday life, thereby minimizing the cost burden associated with providing an additional pad fixing member and reducing feeling of irritation. In addition, the drug carrier device of the present invention may be attached to glasses worn at normal times, thus achieving maximized convenience of use.

Owner:BM BIOTECHNOLOGY LAB CO LTD +1

Replaceable CPU module device of desktop computer

InactiveCN101598958AMeet system requirementsExtend the life cycleDigital data processing detailsCost burdenFinger joint

The invention relates to a replaceable CPU module device of a desktop computer, comprising a system control module board, a CPU module board and a radiation device, wherein a second bus connector of the CPU module board is a golden finger joint extending from the CPU module board and is arranged on a socket joint of a first bus connector of the system control module board so that the replaceable CPU module device of the desktop computer can be utilized by a user to decrease the cost burden for replacing a CPU and prolonging the life cycles of peripheral devices of the desktop computer.

Owner:FIRST INTERNATIONAL COMPUTER

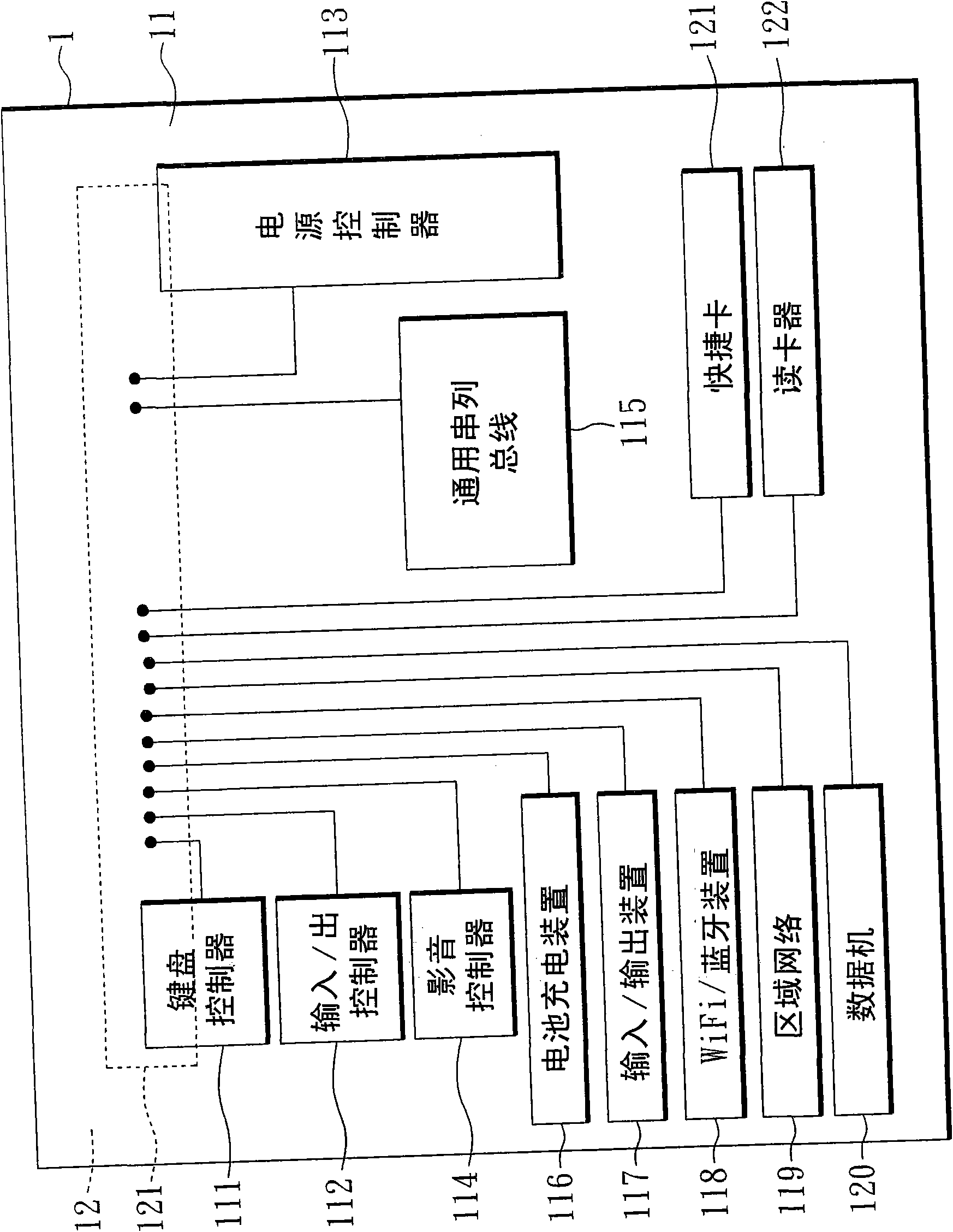

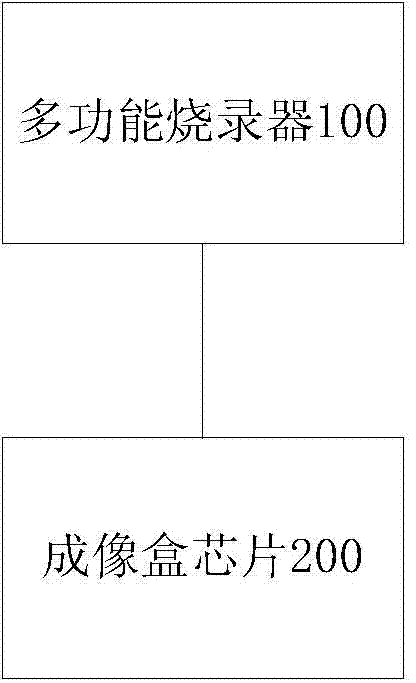

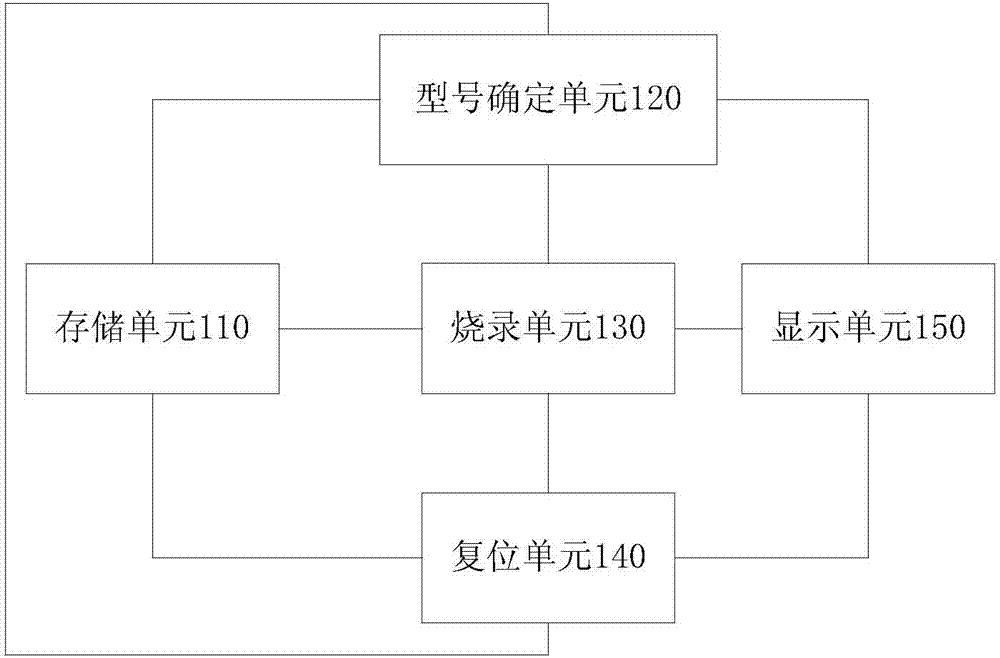

Imaging box chip, multifunctional writer, and imaging box chip processing device and method

ActiveCN104503808AEasy to excludeImprove experienceProgram loading/initiatingCost burdenData information

The invention relates to an imaging box chip processing device. The imaging box chip processing device comprises a multifunctional writer and an imaging box chip; the multifunctional writer is used for storing various groups of program information and various groups of data information, and determining the model number of the imaging box chip, or further used for writing a corresponding group of program information and / or a corresponding group of data information to the imaging box chip according to the determined model number; the various groups of program information include various groups of complete communication protocols corresponding to the communication of the imaging box chip with imaging devices of different types; the various groups of data information include various groups of chip data information corresponding to the imaging box chips of different types; the imaging box chip is used for recording the program information and / or the chip data information written by the multifunctional writer to the imaging box chip. The imaging box chip processing device is suitable for processing schemes such as imaging box chip model number determination, writing and resetting; the processing process is convenient. The imaging box chip processing device is accurate and helpful for enhancing the experience of a user and reducing the extra economic losses and cost burden of the user due to time waste.

Owner:GUANGZHOU ZHONO ELECTRONICS TECH CO LTD

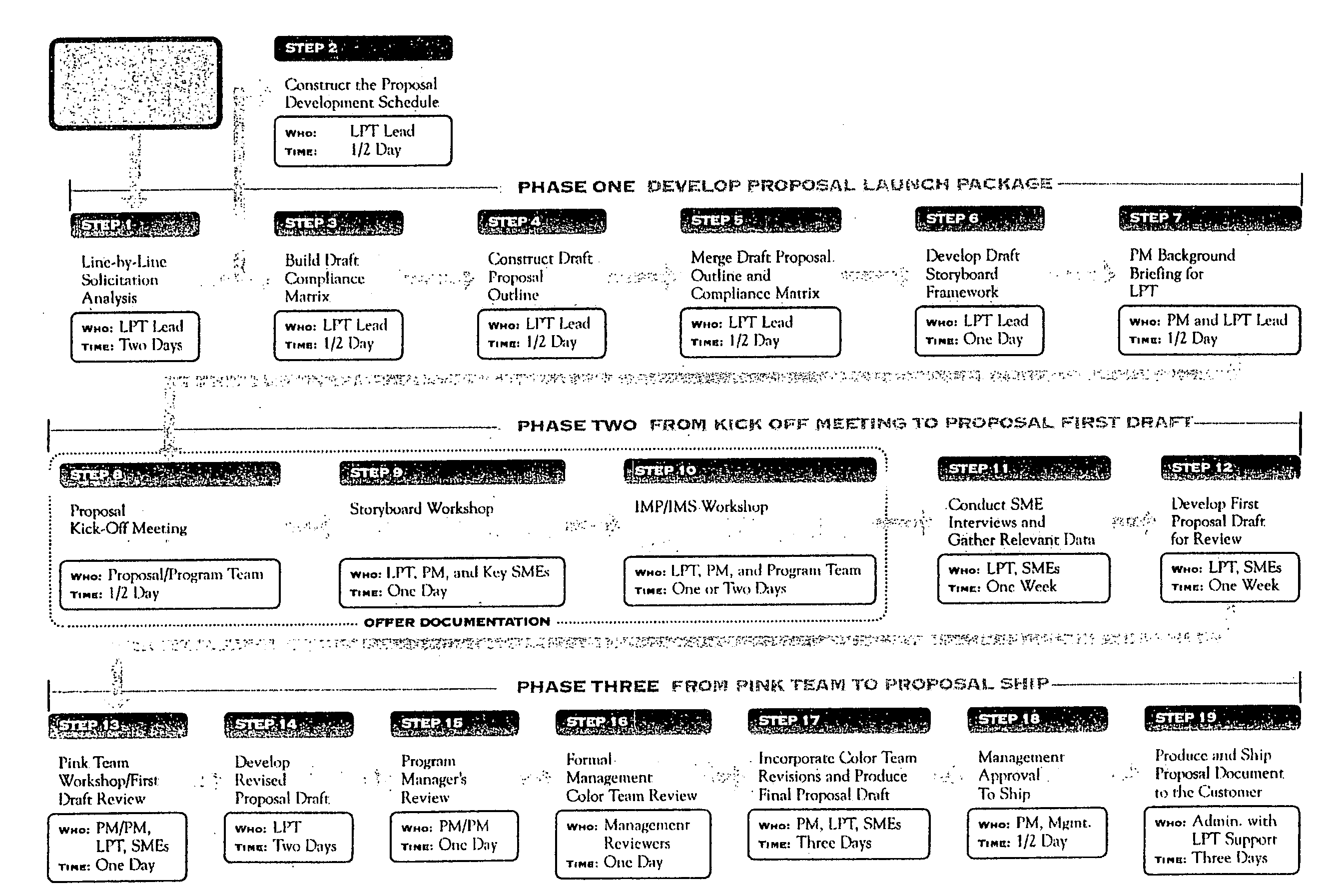

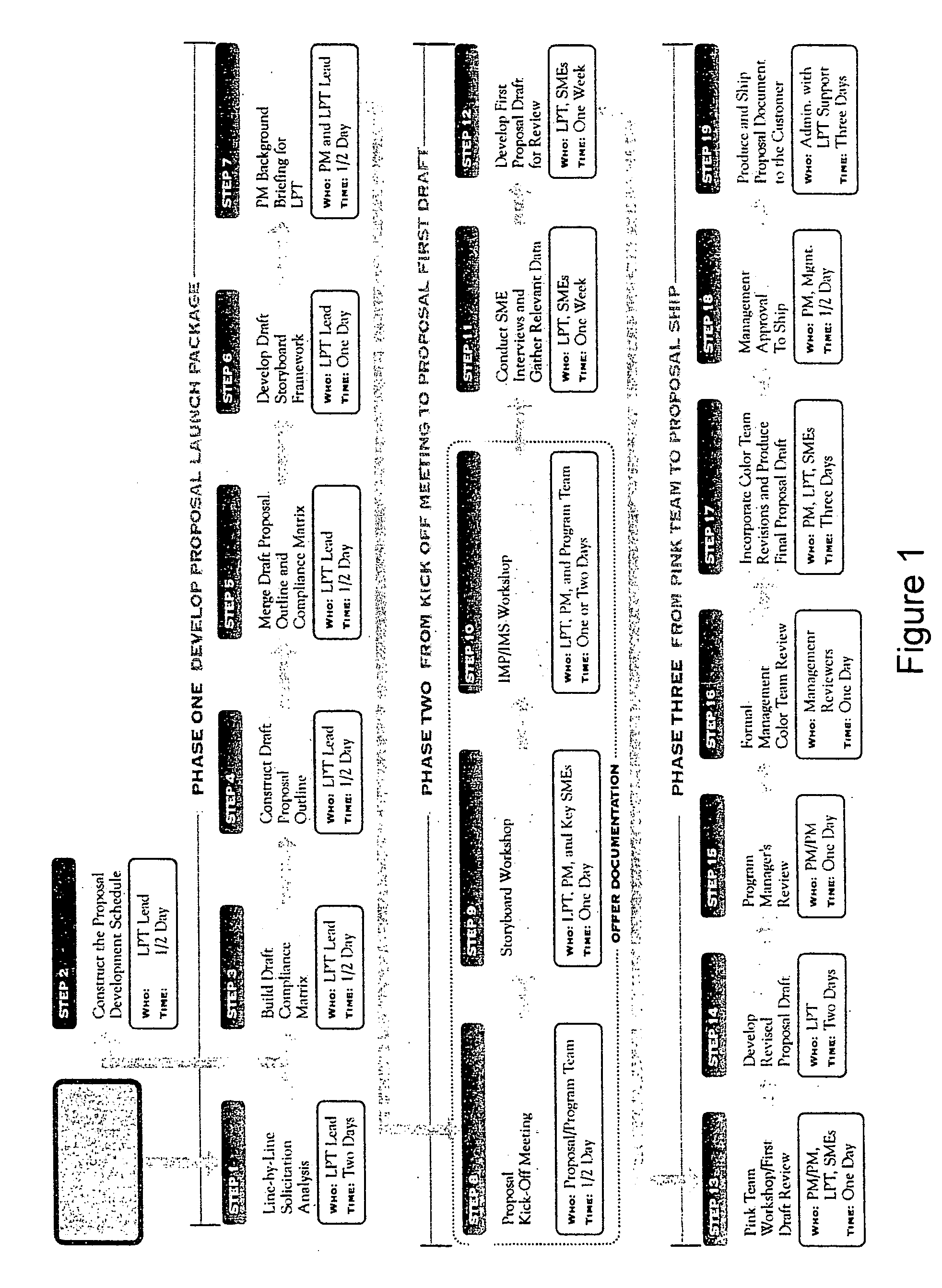

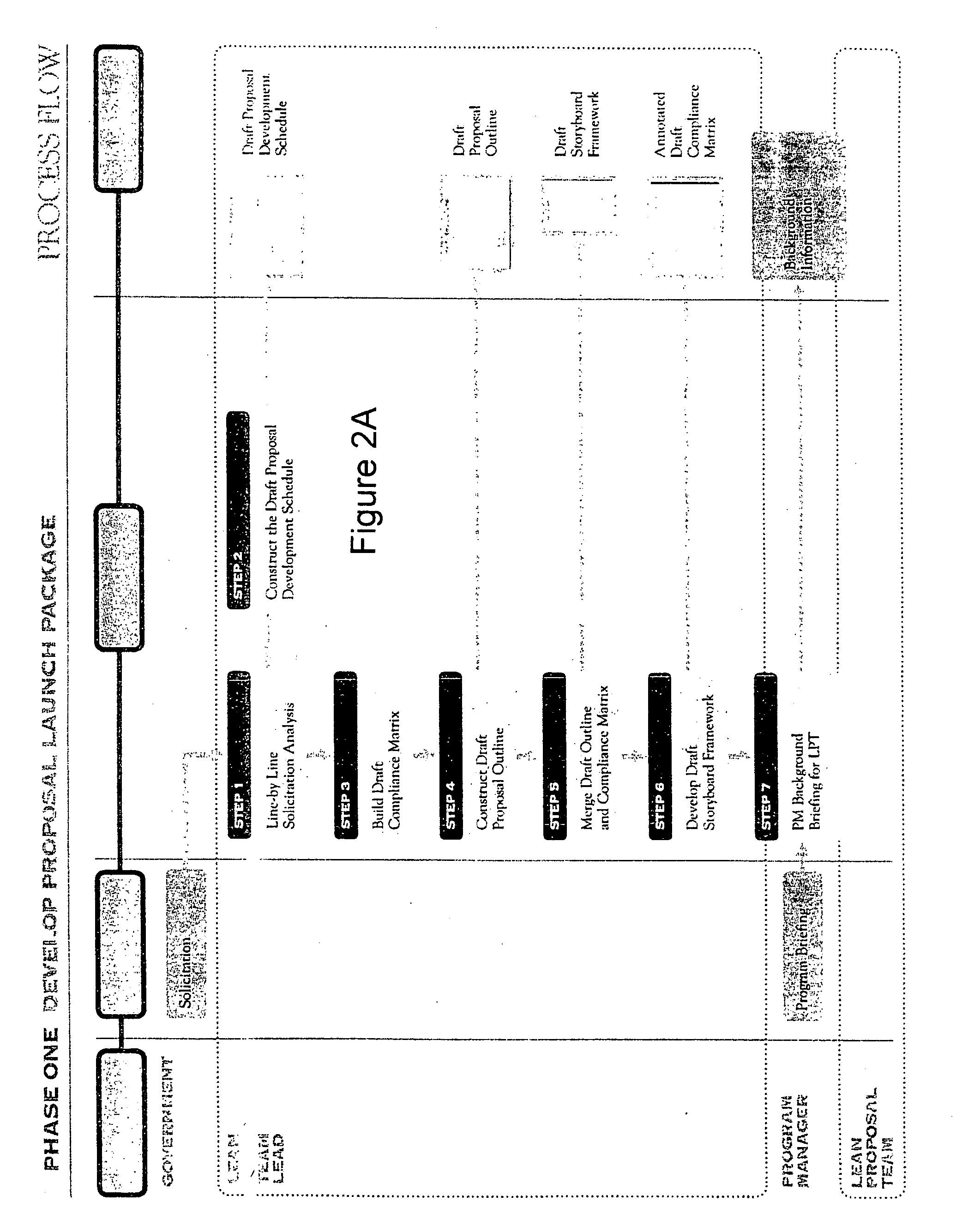

Process for developing business proposals

A method for formulating a business proposal in response to a customer solicitation includes (1) developing a proposal launch package in which is set forth the information needed for the proposal and a framework for obtaining the information; (2) conducting an interactive storyboard review workshop; (3) conducting an interactive offer development workshop and initiating development of an integrated master plan and schedule for the project; (4) conducting interviews with subject matter experts; and (5) drafting proposal content for them to review. Information is collected in accordance with tasks outlined in the framework and this information is used to produce an initial draft of the proposal. This draft is reviewed and revised in response to critiques of the draft; subsequent drafts include additional information identified as being needed in a completed proposal. This approach enables the proposal team to reach a consensus, early in the proposal process, on a detailed response to the solicitation and significantly reduces the time and cost burdens involved in preparing the proposal.

Owner:WAVERLY GRP

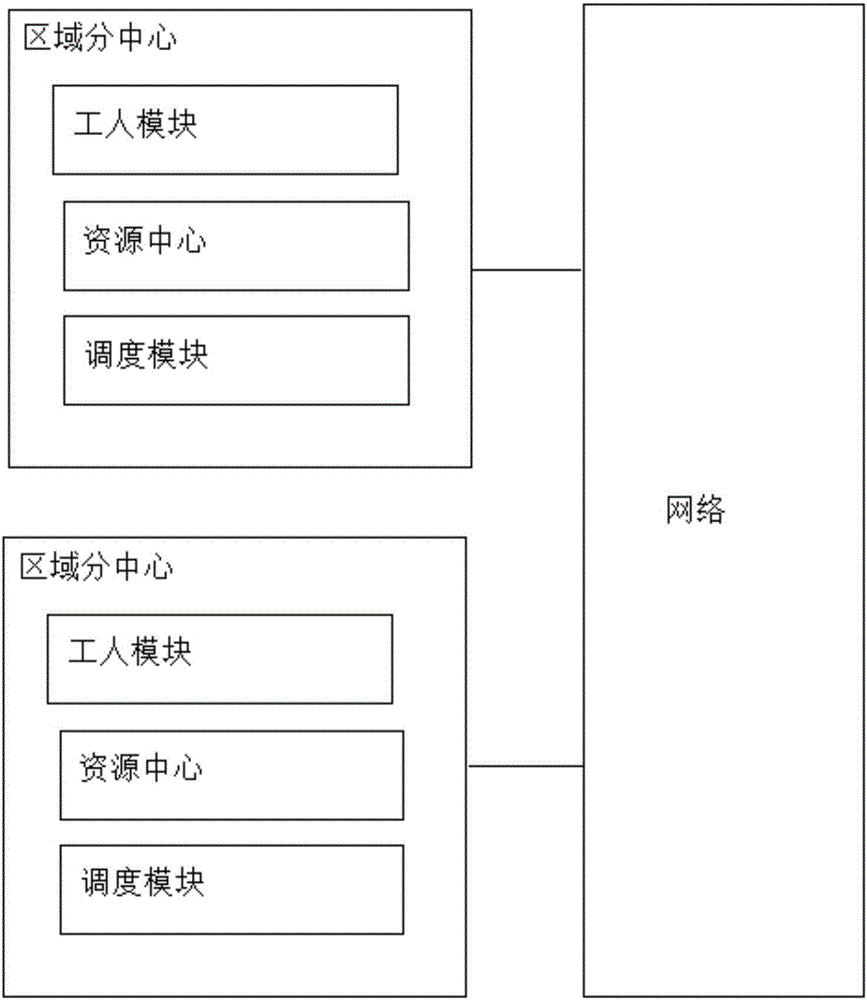

Cloud platform configuration and method for laboratory engineer arrangement

The present invention provides a cloud platform configuration and method for laboratory engineer arrangement. The configuration comprises more than two region branch centers which are connected by the network; each region branch center comprises a worker module, a resource center and at least one dispatching module; three modules of one region branch center can be dispatched on one server, the resource center module and the dispatching module are dispatched on one server; the worker module is dispatched at another server; the worker module includes a worker market and an information receiving and sending interface module, wherein the work market includes at least one worker and / or work group, the worker and / or the worker group emit registering information and a heartbeat package to the resource center, and the worker and / or work group receives the task data sent by the dispatching module so as to avoid adding the manpower cost burden caused by non-uniform manpower resource distribution by employing the mode of directly sending orders through manual work.

Owner:北京戴纳实验科技有限公司

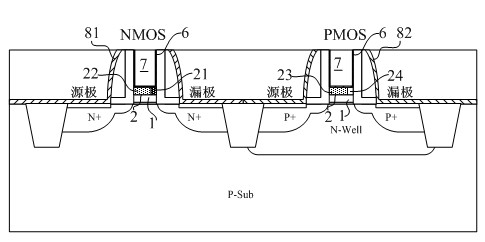

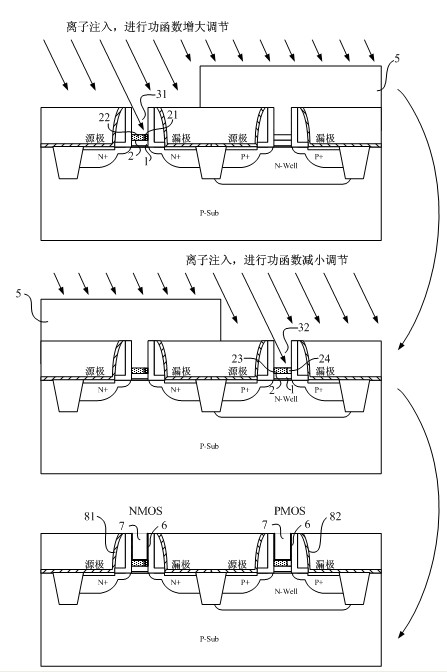

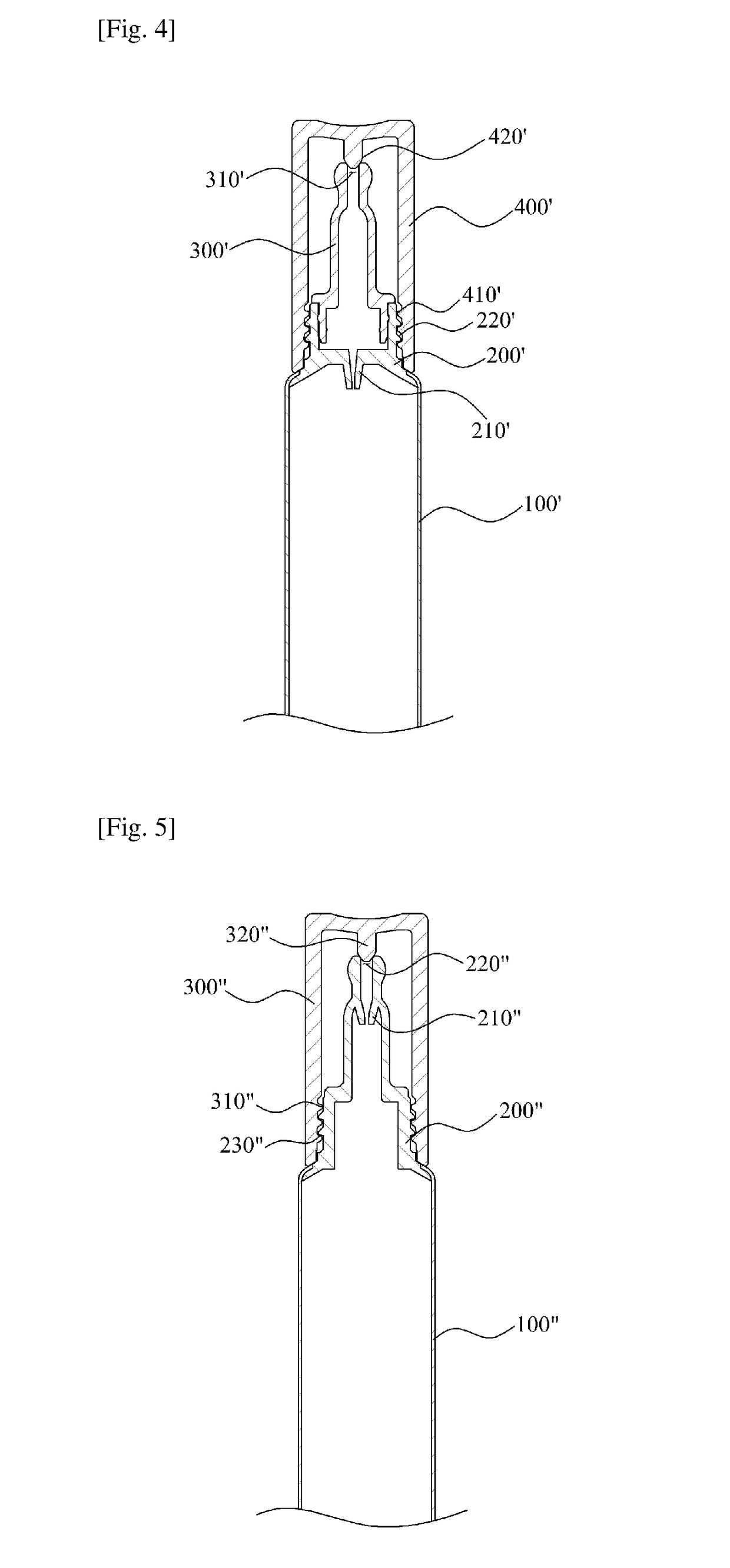

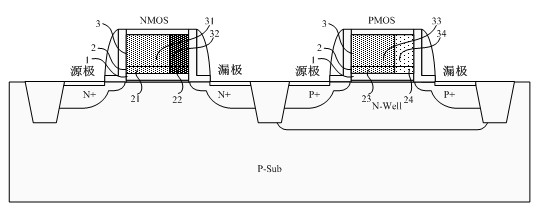

Under-gate technology CMOS (complementary metal oxide semiconductor) device for inhibiting drain induction barrier lower effect and preparation method thereof

ActiveCN102420227AImprove performanceInhibition of DIBL effectTransistorSemiconductor/solid-state device manufacturingElectricityCMOS

The invention provides an under-gate technology CMOS (complementary metal oxide semiconductor) device for inhibiting drain induction barrier reduction effect and a preparation method thereof. The CMOS device comprises an N-type MOS (metal oxide semiconductor) transistor and a P-type MOS (metal oxide semiconductor) transistor, wherein gate grooves of N-type MOS transistor gate and a P-type MOS transistor gate comprise a metal oxide dielectric material layer respectively; ions with different work functions are injected to the metal oxide dielectric material layer, so that the work functions of the N-type MOS transistor gate close to a drain end or two ends of a drain and a source are increased, and the work functions of the P-type MOS transistor gate close to the drain end or close to two ends of the drain and the source are decreased, thus the drain induction barrier lower effect of the CMOS device is inhibited. According to the invention, leakage current of a PN junction at the drain end can not be caused while changing the working functions of the drain end of the CMOS device or the working functions close to two ends of the drain or source so as to inhibit DIBL (drain induction barrier lower) effect effectively, thus the performances of a semiconductor chip are improved effectively; and the method has simple process flow, low implementation cost and no additional cost burden.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Tube-type cosmetics container for discharging liquid contents in form of droplet

ActiveUS10179680B2Reduce cost burdenShorten production timeClosures with discharging devicePackaging toiletriesCost burdenTubes types

Provided is a tube-type cosmetic container which discharges a liquid content in a form of droplet. The tube-type cosmetic container reduces the cost burden in accordance with shortening of the manufacturing time and reducing cost, by allowing a liquid content to be discharged in a form of droplet through a simple content discharging structure that becomes gradually wider from a lower portion to an upper portion thereof.

Owner:YONWOO CO LTD

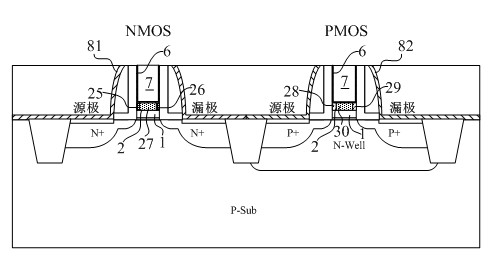

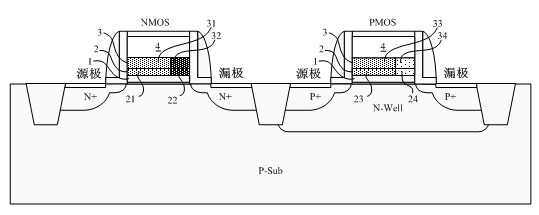

CMOS (Complementary Metal-Oxide-Semiconductor Transistor) for inhibiting drain induced barrier lowering effect and manufacturing method of CMOS

ActiveCN102420226ANo extra growthImprove performanceTransistorSemiconductor/solid-state device manufacturingCMOSCost burden

The invention provides a CMOS (Complementary Metal-Oxide-Semiconductor Transistor) for inhibiting a drain induced barrier lowering effect and a manufacturing method of the CMOS. The CMOS comprises an N-type MOS (Metal-Oxide-Semiconductor) transistor and a P-type MOS transistor, wherein a gate of the N-type MOS transistor and a gate of the P-type MOS transistor respectively comprise a high dielectric layer, a metal oxide dielectric material layer and polysilicon or a metal layer; and ions with different work functions are implanted in the metal oxide dielectric material layer and the polysilicon or the metal layer, so that a work function of the gate of the N-type MOS transistor, which is close to the drain electrode end, is increased, a work function of the gate of the P-type MOS transistor, which is close to the drain electrode end, is reduced and further the drain induced barrier lowering effect of the CMOS is inhibited. While the DIBL (Drain Induced Barrier Lowering) effect is effectively inhibited by changing the work function of the gate of the CMOS, which is close to the drain electrode end, extra increase of drain end PN (Peripheral Node) leakage current can be avoided and the performance of a semiconductor chip is effectively improved; in addition, the manufacturing method has the advantages of simple process flow, low implementation cost and avoidance of extra cost burden.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP