Under-gate technology CMOS (complementary metal oxide semiconductor) device for inhibiting drain induction barrier lower effect and preparation method thereof

A gate-last process and inductive barrier technology are applied in the field of gate-last process CMOS devices to achieve the effects of low implementation cost, improved performance and simple process flow

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

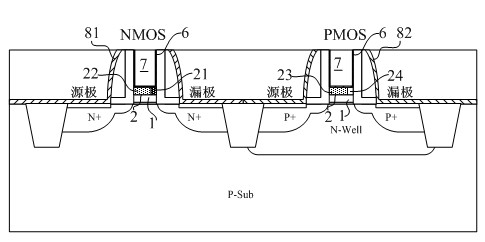

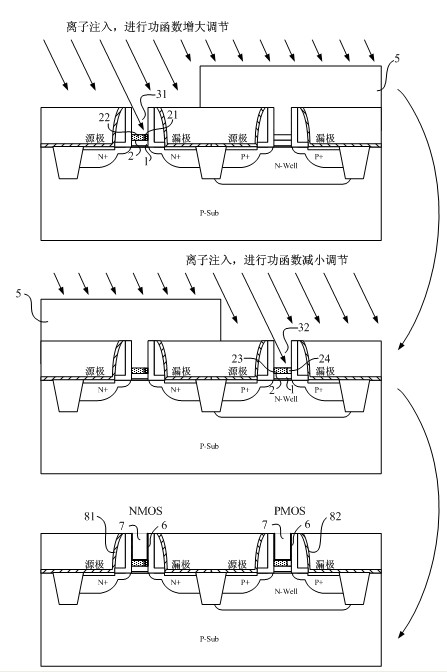

[0047] Such as figure 1 As shown, the present invention provides a gate-last process CMOS device that suppresses the drain-induced barrier lowering effect, and the gate-last process CMOS device includes an N-type MOS transistor and a P-type MOS transistor. In the gates of the N-type MOS transistor and the P-type MOS transistor, a high dielectric layer 1 and a metal oxide dielectric material layer 2 covering the high dielectric layer 1 are included, and the high dielectric Below layer 1 may also include optionally growing a thin oxide layer.

[0048] Wherein, in the metal oxide dielectric material layer 2 of the N-type MOS transistor, ions with a large work function are implanted into the part 21 close to the drain terminal, which improves the performance of the metal oxide dielectric material layer 2 close to the drain terminal. The work function of part 21 increases the flat-band voltage required by the gate at the drain terminal during use, so that in its channel, the elect...

Embodiment 2

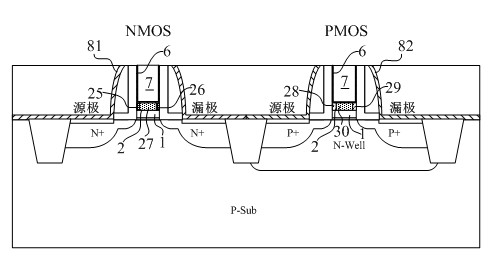

[0063] Such as figure 2 As shown, the difference between the CMOS structure of this embodiment and the above-mentioned embodiment 1 is that,

[0064] In this embodiment, the metal oxide dielectric material layer 2 in the gate groove 31 of the N-type MOS transistor is implanted with ions having a large work function near the source end portion 25 and the drain end portion 26, thereby improving the dielectric strength. The work function of the electrical material near the source terminal portion 25 and the drain terminal portion 26 makes the work function of both of them greater than the work function of the middle portion 27 between the drain terminal and the source terminal. In this way, the flat-band voltage required by the gate at the drain terminal and the source terminal can be increased, and in its channel, the electronic potential barrier close to the source and drain terminals can be increased at the same time, thereby effectively suppressing the N-type semiconductor d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More