Circuit structure of first-in-first-out memory based on random access memory

A circuit structure, first-in-first-out technology, applied in the field of rapid implementation of parallel scheduling, can solve the problems of increased design structure links, increased processing links, increased delays, etc., to reduce design complexity, speed up processing procedures, and reduce data delays Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] Referring to the accompanying drawings, a brief description will be given below of the implementation of the content of the present invention.

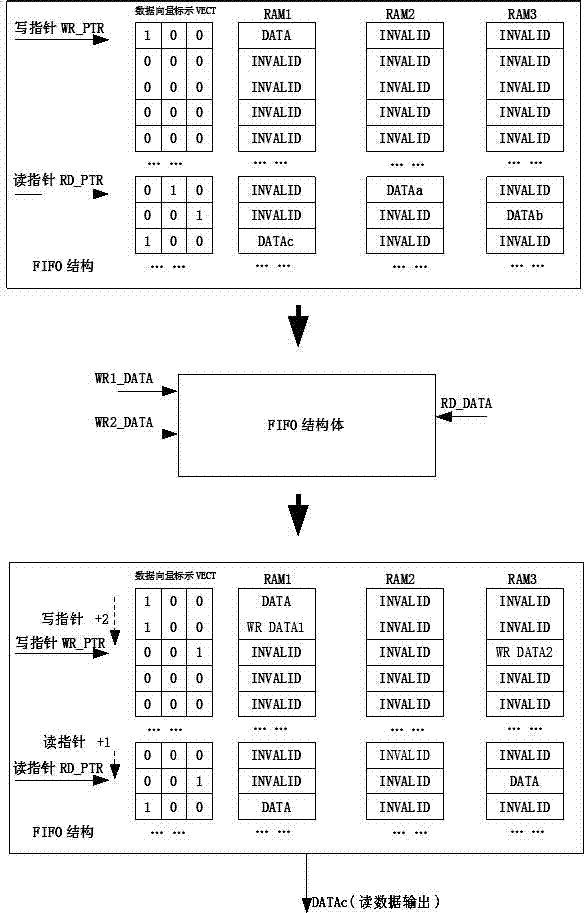

[0017] Taking the currently designed high-speed network protocol chip as an example, in the design, after the multi-channel message data is received in parallel through the interface module, it enters the protocol processing module at the same time, and the multi-channel input and single-output FIFO is used for receiving and sorting, and then sequentially output to the Protocol processing module. Here, taking a FIFO with 2 channels of input and 1 channel of output as an example, the circuit structure and operation mode of this type of FIFO design are explained: when two channels of messages arrive at the FIFO at the same time and the FIFO read data signal is enabled at the same time, the FIFO simultaneously receives For the two-way message data, first obtain the writable address information in the current RAM according to the w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More