VDMOS (Vertical double-diffused metal oxide semiconductor) and manufacturing method thereof

A manufacturing method and body region technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as channel length and accuracy cannot be guaranteed, and achieve the effect of controllable channel length and accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

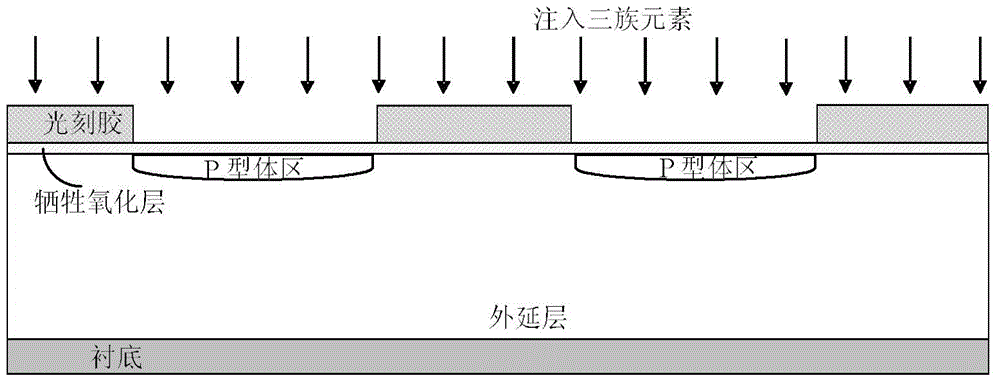

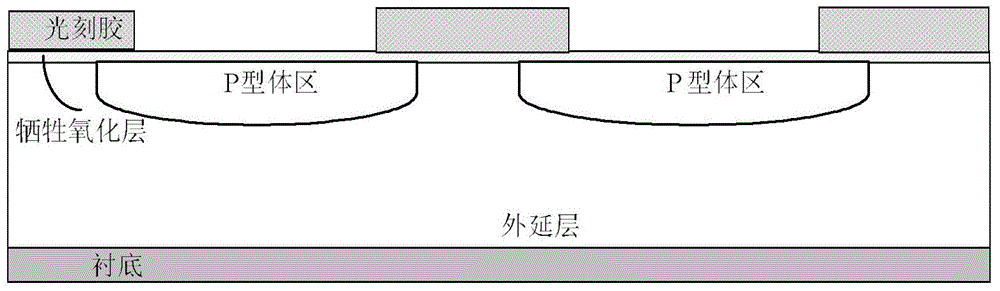

[0036] Embodiments of the present invention provide a vertical double-diffused field effect transistor VDMOS and a manufacturing method thereof, which are used to solve the problem in the prior art that there is a cumulative deviation in the manufacture of the polysilicon layer and the P-type body region, which causes the P-type body region to be separated from the polysilicon layer. The length and accuracy of the channel formed between them cannot be guaranteed.

[0037] Embodiments of the present invention will be specifically described below in conjunction with the accompanying drawings.

[0038] The embodiment of the present invention provides a method for fabricating VDMOS, such as Image 6 As shown, the method includes:

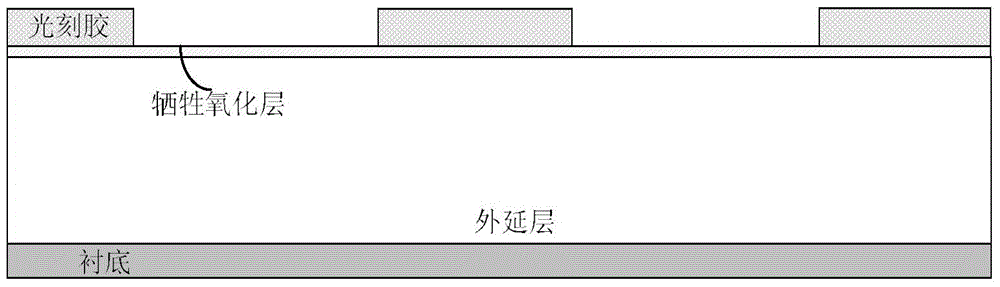

[0039] S1: Form an oxide layer on the epitaxial layer, such as Figure 7 shown;

[0040] The thickness of the oxide layer is preferably in the range of about 0.05 μm to 0.15 μm. The growth temperature of the oxide layer is about 1000°C to 1150°C.

...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More