Method for reducing number of cables through interconversion between parallel bus and serial bus

A mutual conversion and bus technology, applied in the direction of electrical digital data processing, instruments, etc., can solve the problems that the FPC line is difficult to pass through the rotating parts, it is difficult to accurately detect the assembly in place, and the number of cables is large, so as to reduce the number and performance requirements , The effect of high circuit integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

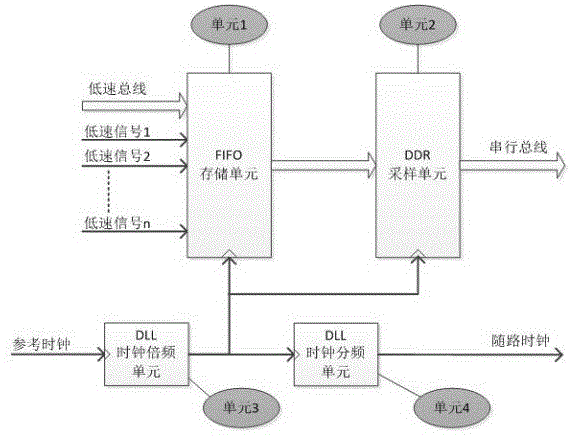

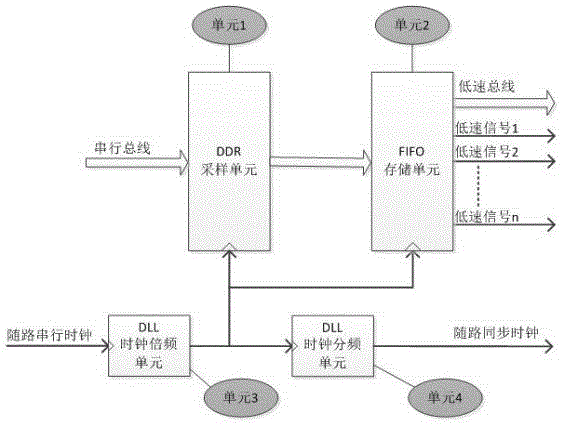

[0021] This embodiment describes a method for reducing the number of cables by converting between serial and parallel buses, using hardware description language to realize serial-to-parallel, parallel-to-serial functions, and DLL (digital phase-locked loop) frequency multiplication and DDR (Double Edge Sampling) function, and burn the compiled program into a small package CPLD or FPGA.

[0022] The present invention adopts a programmable logic chip of CPLD or FPGA, and requires DLL and DDR functions inside the chip. The pin rate and system clock rate of the chip should be at least twice that of all low-speed signals (need to satisfy the Nyquist sampling theorem).

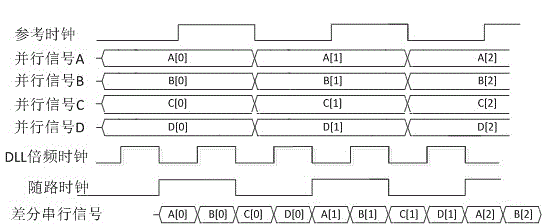

[0023] For the implementation method of parallel to serial function, please refer to figure 1 . figure 1 Various low-speed bus signals on the left and various low-speed signals are sent to the programmable logic chip, and the synchronous clock or other clocks of the low-speed bus are also sent to the programmable ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More