A Reliability Evaluation Method for Multi-Abstract Level Circuits

An abstract level and reliable technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., to achieve low cost, avoid rapid expansion, and avoid unreliable results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

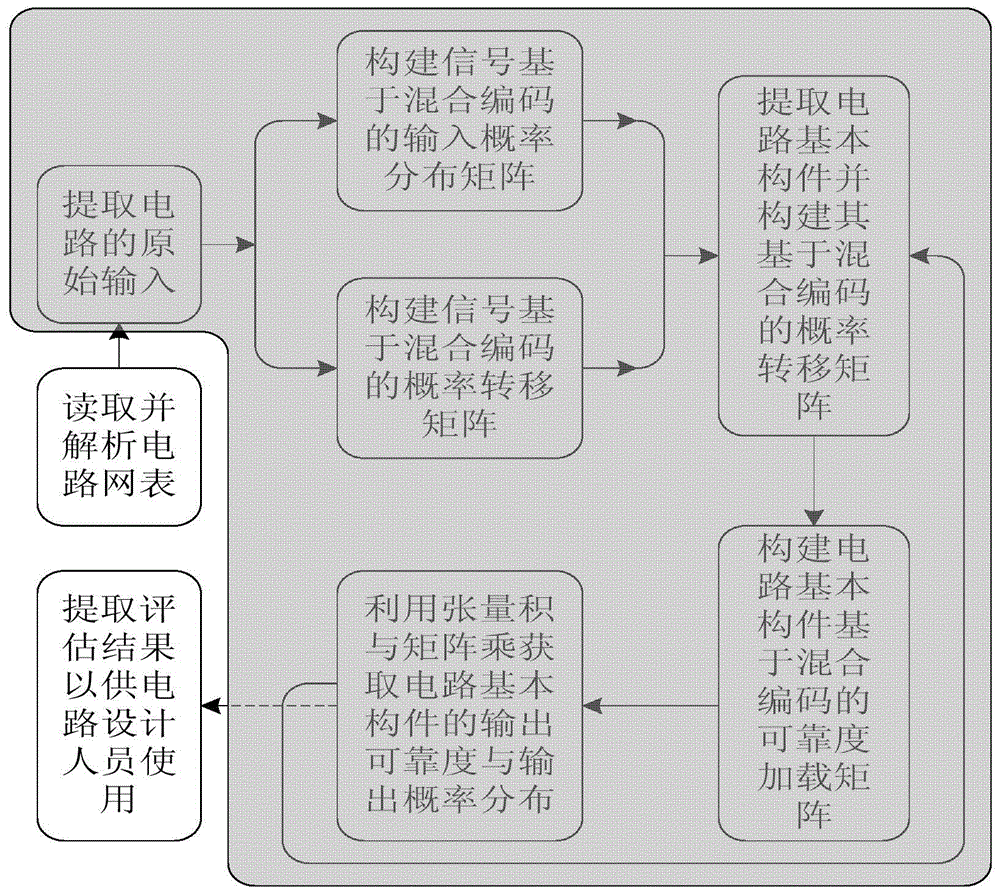

[0024] Referring to the attached picture:

[0025] A kind of reliability evaluation method for multi-abstraction level circuit of the present invention, comprises the following steps:

[0026] Step 1: Netlist analysis and initialization of related quantities.

[0027] 1) Read the circuit netlist.

[0028] 2) Detect the interconnection structure between the basic components of the circuit, and display the implicit series-parallel relationship; then implement layering on the circuit, and extract its original input terminal number (indicated by n) and original output terminal number (indicated by m).

[0029] 3) Extract the i-th original input signal of the circuit, and construct its probabilistic transfer matrix (PTM) based on mixed coding (using PMs i representation), the ideal transfer matrix (ideal transfermatrix, ITM) (using IMs i Represented) and the input probability distribution (with pds i express).

[0030] Among them, i refers to the serial number of the original in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More