Inverted structure of III conductor light-emitting device

一种发光器件、半导体的技术,应用在半导体器件、电固体器件、电气元件等方向,能够解决蚀刻孔洞高、工艺复杂、生产成本高等问题,达到简化制程的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

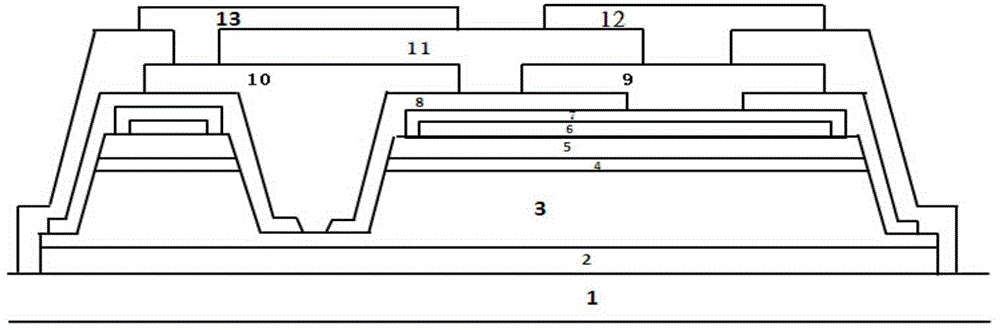

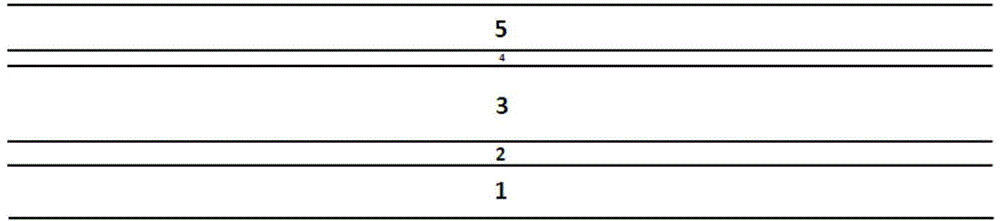

[0060] combine Figure 2a-Figure 13 , an object of the present invention is to provide a novel flip-chip structure of a Group III semiconductor light emitting device, comprising: a substrate 1, a buffer layer 2, an n-type nitride semiconductor layer 3, an active layer 4, a p-type nitride semiconductor Layer 5, first insulating layer structure 8-1, P-type contact metal 9, N-type contact metal 10, second insulating layer structure 11-1, flip-chip P-type electrode 12, flip-chip N-type electrode 13 and transparent conductive layer 14;

[0061] Wherein, the substrate 1, the buffer layer 2, the n-type nitride semiconductor layer 3, the active layer 4, and the p-type nitride semiconductor layer 5 arranged in sequence from bottom to top form a nitride semiconductor layer with a linear convex mesa 19. structure.

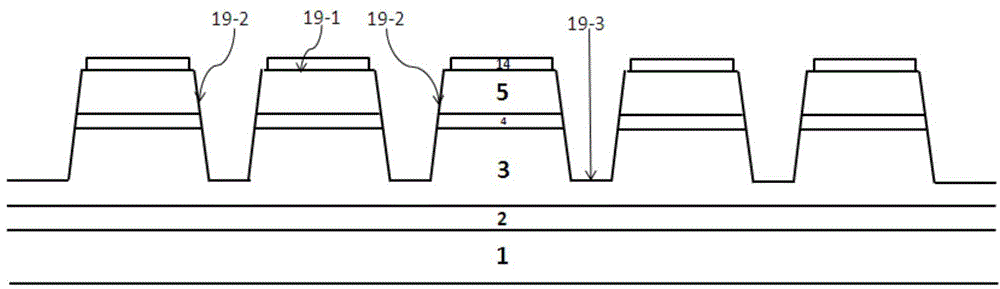

[0062] The linear convex mesa 19: includes a first upper surface 19-1, a side surface 19-2 and a second upper surface 19-3, the first upper surface 19-1 and the second uppe...

Embodiment 2

[0108] The flip-chip structure in this embodiment all adopts the technology of line convex mesa 19 instead of the technology of multiple vias.

[0109] Such as Figure 3a Shown is a top view of a plurality of vias in the prior art, Figure 3b for Figure 3a Sectional view along the A-B direction.

[0110] Such as Figure 4a Shown is a top view of a linear convex table top, Figure 4b for Figure 4a Sectional view along C-D direction.

[0111] The etched area of the line convex mesa 19 is single or multiple lines;

[0112] The substrate 1, the buffer layer 2, the n-type nitride semiconductor layer 3, the active layer 4 and the p-type nitride semiconductor layer 5 form a nitride semiconductor structure with a line convex mesa 19;

[0113] The linear convex mesa includes a first upper surface 19-1, a side surface 19-2 and a second upper surface 19-3, and the two ends of the first upper surface are respectively provided with the side surface and the second upper surface. ...

Embodiment 3

[0116] On the basis of Embodiment 2, the lower end of the P-type wire electrode 15 in this embodiment is arranged on the transparent conductive layer 14 (such as Figure 5a shown) or arranged on the surface of the first insulating layer structure 8-1 and on the transparent conductive layer 14 (such as Figure 5b shown).

PUM

| Property | Measurement | Unit |

|---|---|---|

| wavelength | aaaaa | aaaaa |

| wavelength | aaaaa | aaaaa |

| wavelength | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More