Method for forming insulating structure and semiconductor structure

An insulating structure, semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

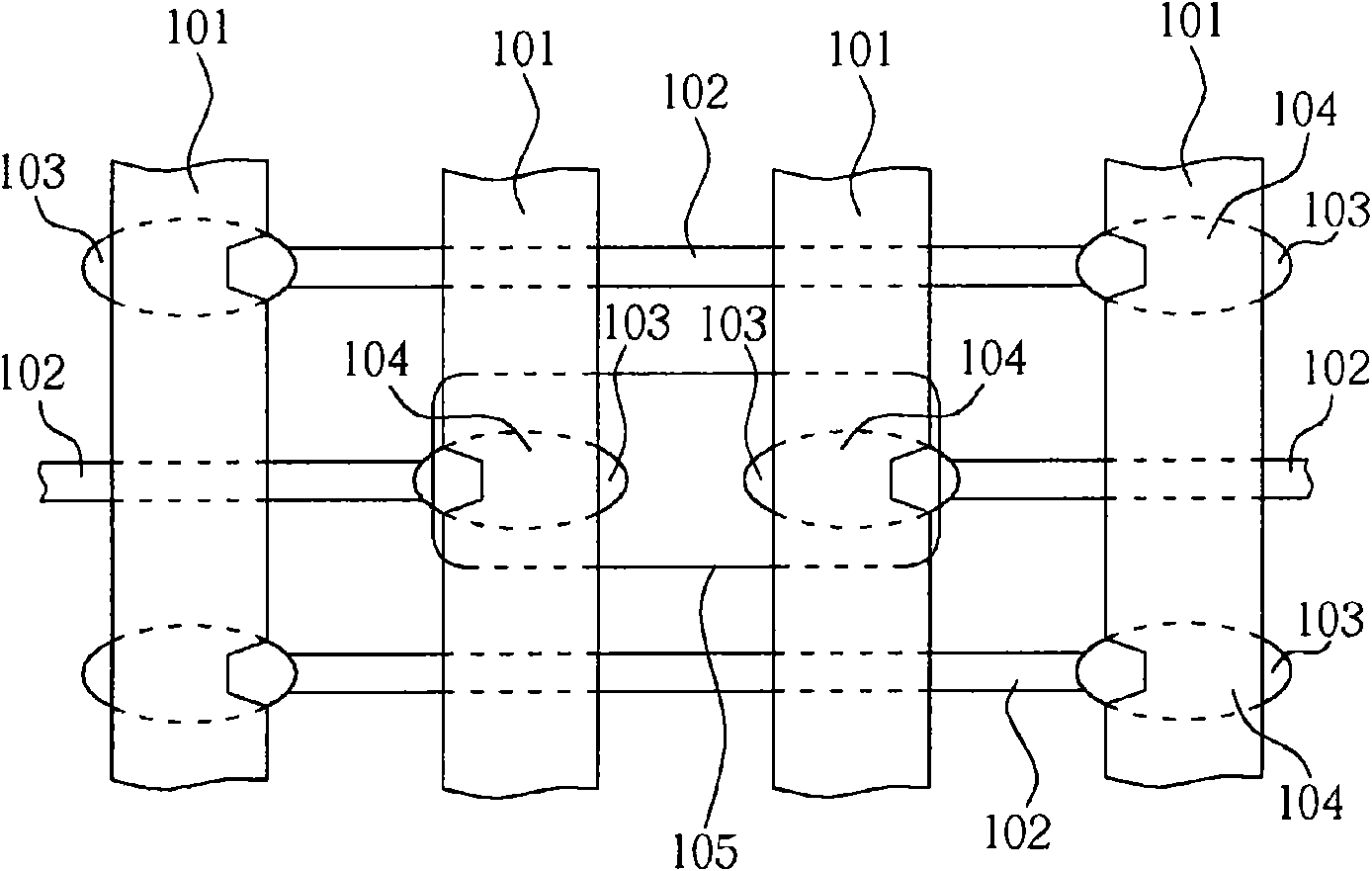

[0027] The present invention is to provide a novel method of forming a self-aligned insulating structure for via gates, which avoids the use of additional photomasks to define the position of the insulating structure, and solves the problem of the isolation structure and the depth of the insulating structure. The problem of alignment between trench capacitors, and the shallow trench isolation and deep trench capacitance will not be exposed before the insulation structure is completed, which can effectively protect the exposed shallow trench isolation and deep trench capacitance from ion trap implantation, Cleaning, high-temperature tempering and other process damage can greatly improve the yield rate of dynamic random access memory (DRAM) and other processes.

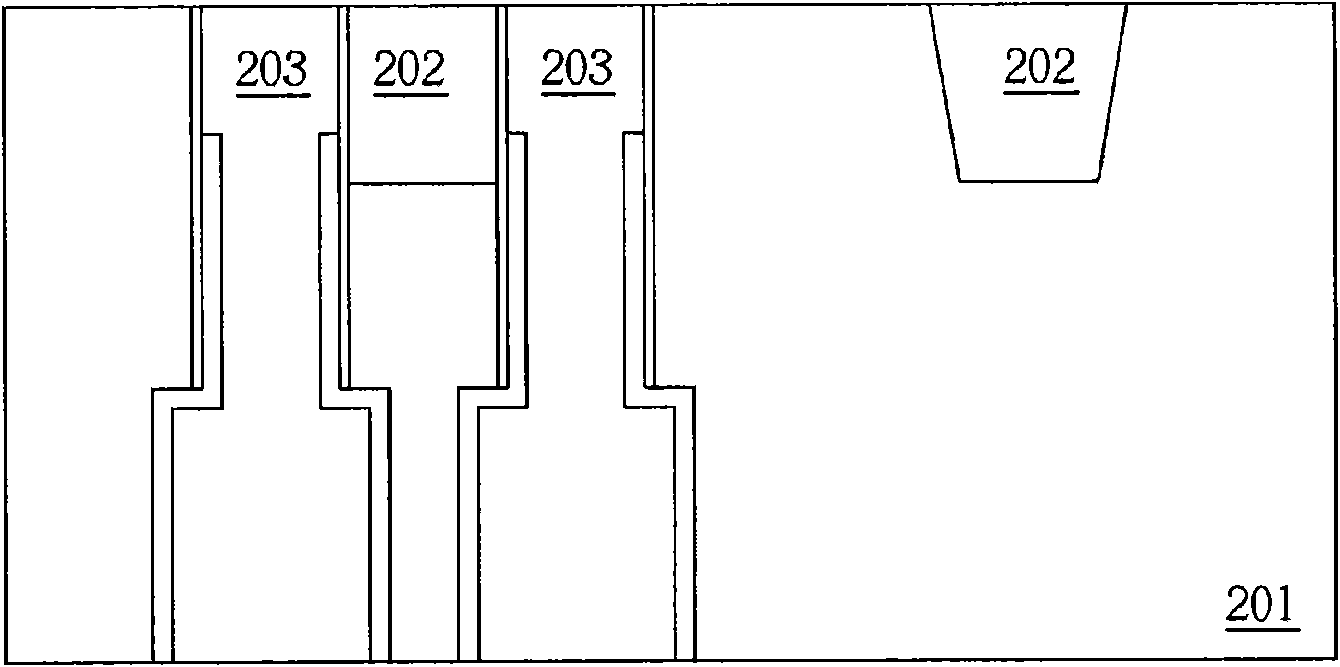

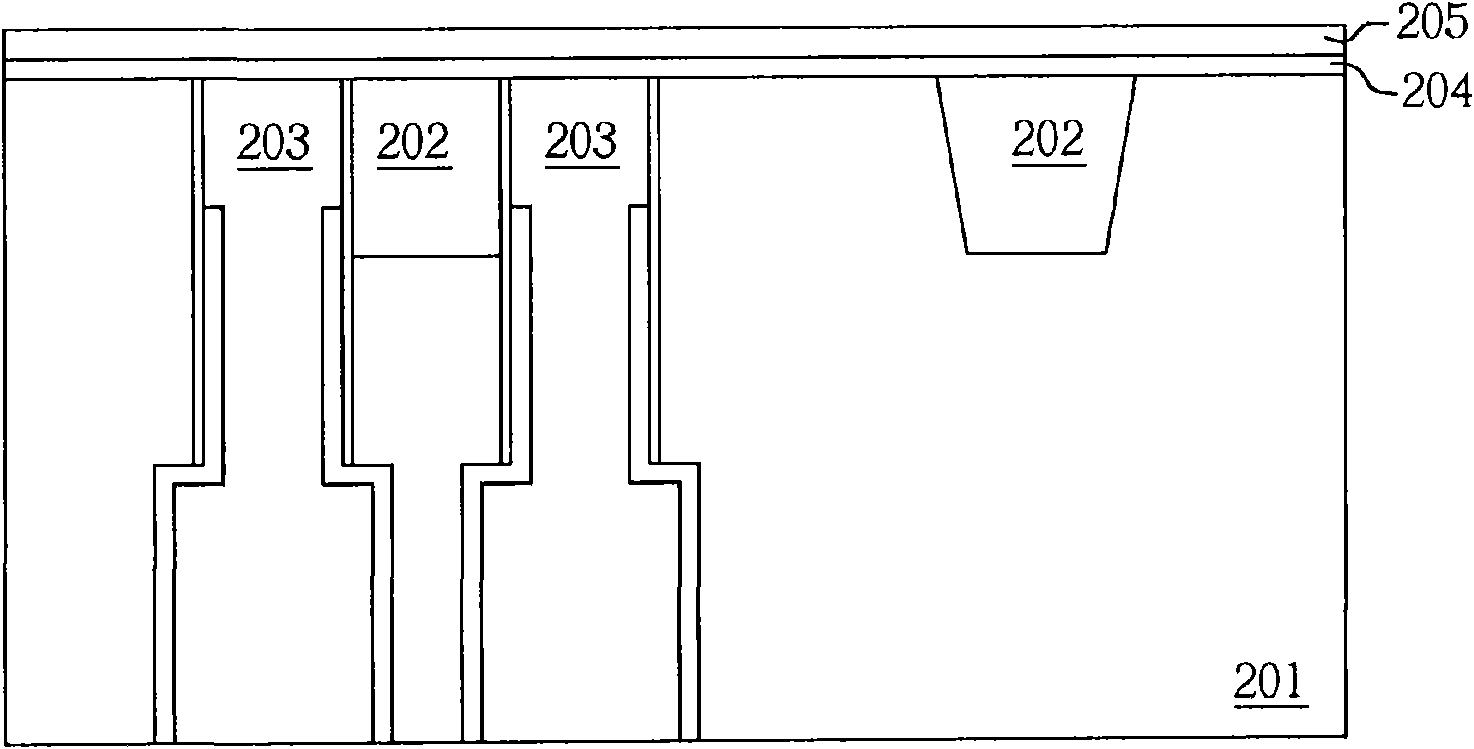

[0028] Figure 9-17 A preferred embodiment of the method of forming the insulating structure of the present invention is illustrated. First, if Figure 9 As shown, a substrate 301 is provided. The substrate 301 inclu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More