Grid electrode formation method and transistor formation method

A transistor and gate technology, applied in the field of semiconductor manufacturing, can solve problems affecting the performance of semiconductor devices and processes, and achieve the effects of reducing energy, reducing the degree of influence, and reducing the temperature of electrons

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

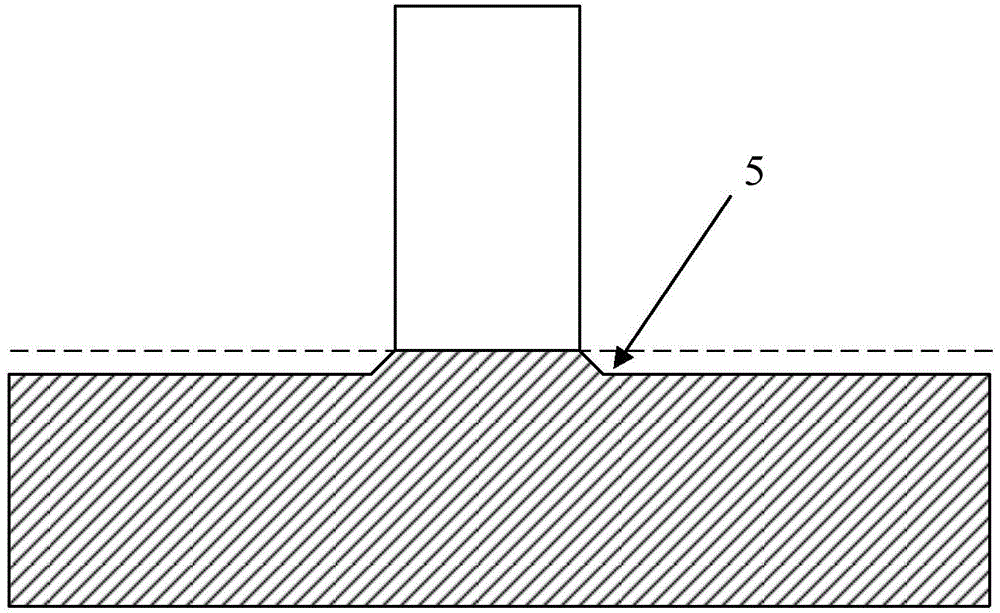

[0044] In the existing process of etching the gate material layer to form the gate, it is easy to cause a certain degree of loss (loss) to the substrate, resulting in recesses (recesses) being formed on the substrate surface on both sides of the formed gate.

[0045] For example, when the etching process is carried out to a certain extent, a part of the substrate will be exposed, and it is easy to cause a certain loss to the substrate at this moment; Penetration into the substrate and consequent loss of the substrate.

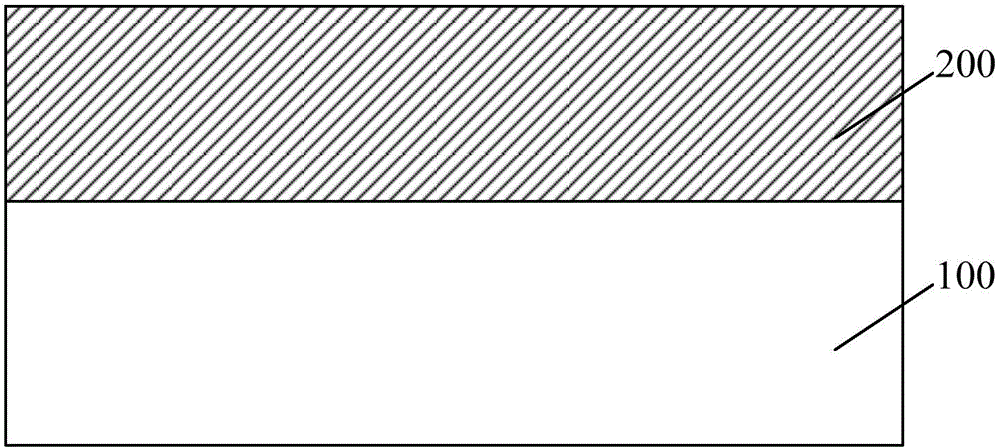

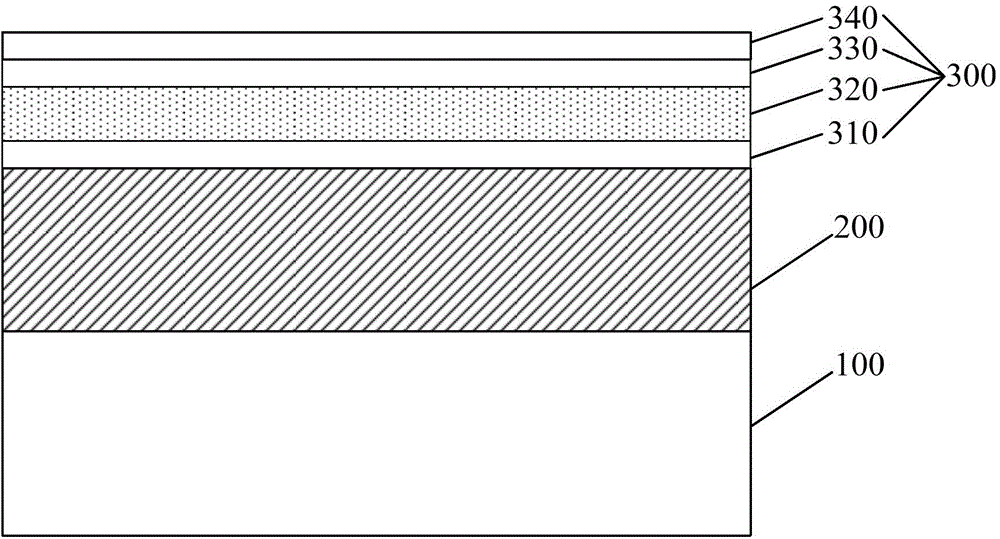

[0046] To this end, the present invention provides a method for forming a gate, comprising the following steps: providing a substrate; forming a gate material layer on the substrate; performing plasma etching on the gate material layer to form a gate ; Wherein, the power output by the etching machine is in the form of pulses, and the gate material layer is pulsed etched.

[0047] Through the above steps, the etching machine is made to output pulsed power to pe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More