Device and method for correcting error estimation of analog-digital converter

一种模数转换器、误差估计的技术,应用在模数转换器、模/数转换、模拟/数字转换校准/测试等方向,能够解决估计校正收敛速度慢、增加单次估计所需的时间等问题,达到减少采样的样本点数、降低持续时间的要求、缩减校正收敛速度的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

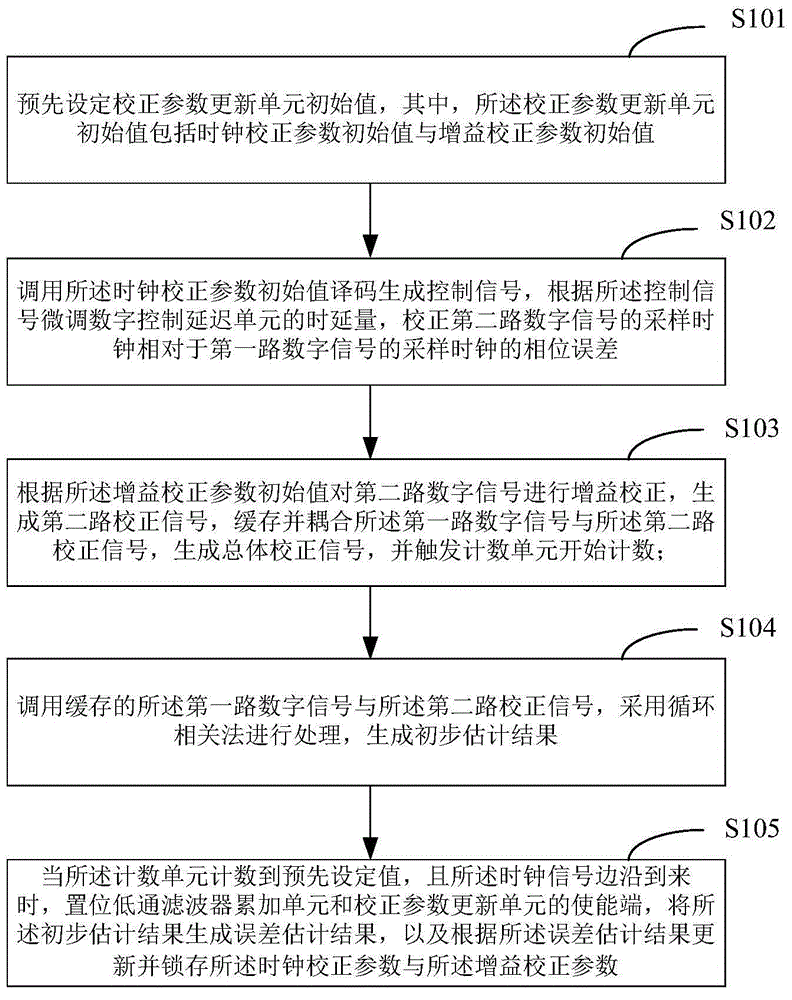

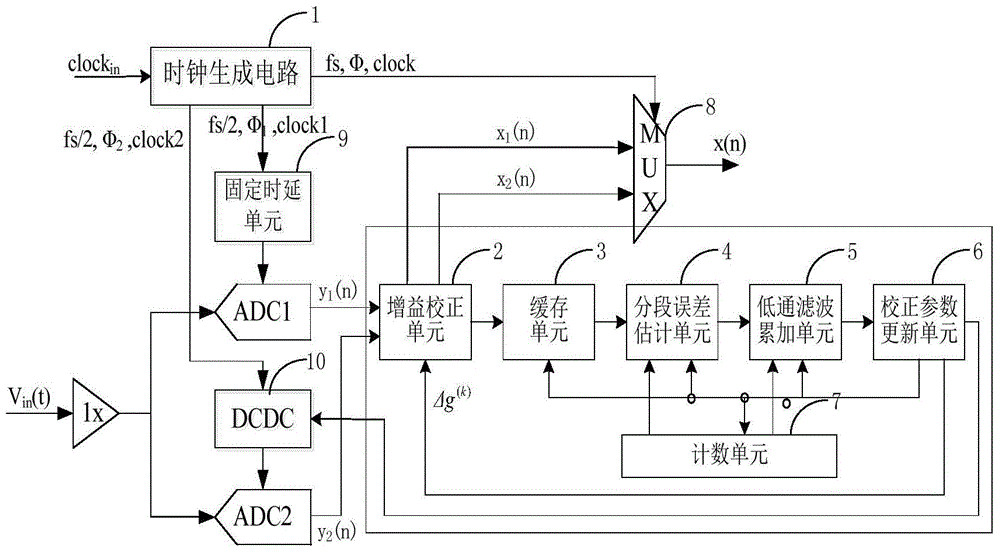

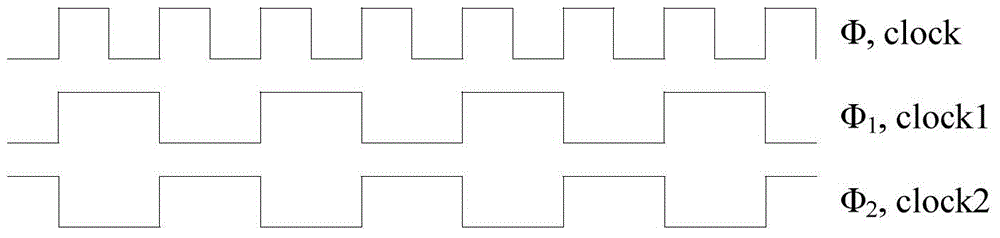

[0075] In the correction of the dual-channel time division multiplexing analog-to-digital converter (TI ADC), the clock signal generator of the TI ADC generates a first clock signal and a second clock signal according to the clock signal; the first clock signal and the The second clock signal is a clock signal with the same period and a phase difference of 180 degrees, and the first channel sub-ADC samples and holds the input signal on the period of the first clock signal to provide the first channel The digital signal is a reference signal; the second channel sub-ADC samples and holds the input signal on the period of the two clock signals, so as to provide the second digital signal as a signal to be corrected.

[0076]And a digital control analog delay cell 10 (digital control delay cell, DCDC) is set in the sampling clock path of the second digital signal, which can fine-tune the clock phase so as to correct the second clock signal relative to the first clock signal. phase ...

Embodiment 2

[0097] Take the single-channel 250MHz, dual-channel time-interleaved 500MHz sampling rate 14-bit A / D converter as an example for specific description. When the two channel sub-ADCs sample the input signal in parallel, between the sampling clocks, the phase difference between the first clock signal and the second clock signal is 180 degrees, and the sampling period is 4 ns. Set the reference channel ADC output data to y 1 (n); Correction channel ADC output data is y 2 (n). DCDC is a digitally controlled analog delay unit 10, controlled by 8-bit binary codes (0-255), with a total of 256 codes, and the delay step adjusted corresponding to the unit code is 60 fs. Insert the same DCDC in the ADC clock path of the reference channel as that in the ADC clock path of the correction channel; the control code of the DCDC in the ADC clock path of the reference channel is fixed at 128, and the fixed delay is 7.68ps; the ADC clock path of the correction channel The DCDC control code is d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More