Thin-film transistor, manufacturing method thereof, array substrate and display device

A technology of thin film transistor and manufacturing method, which is applied in the direction of transistor, semiconductor/solid-state device manufacturing, electric solid-state device, etc., can solve the problems of large equipment loss, difficult mass production, and low yield rate.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

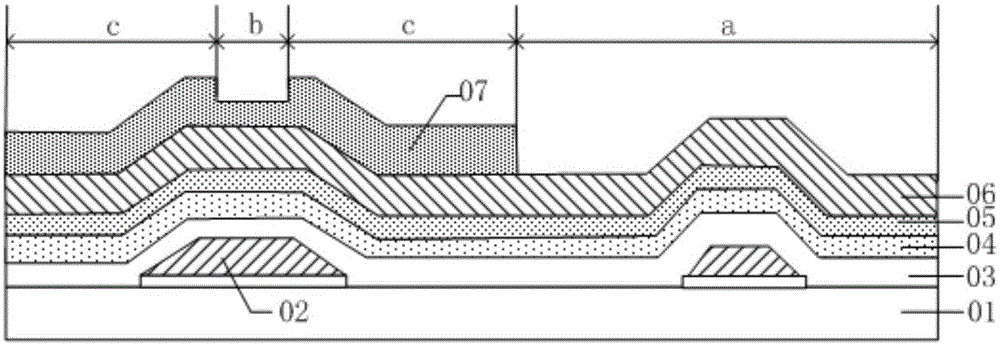

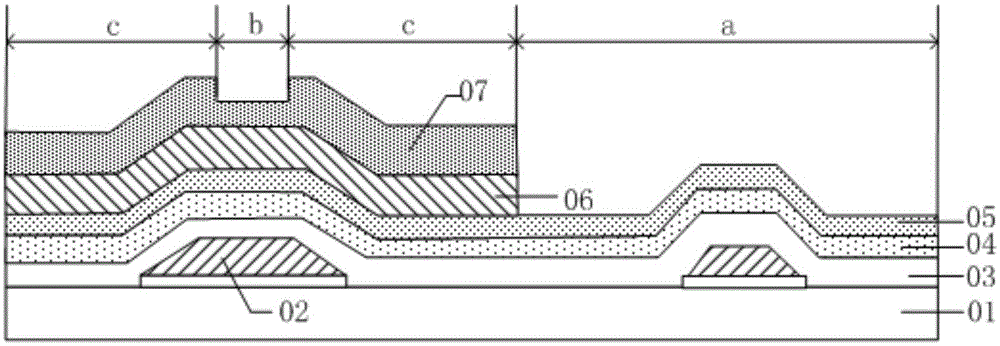

[0039] The specific implementation manners of the thin film transistor, the manufacturing method thereof, the array substrate and the display device provided by the embodiments of the present invention will be described in detail below with reference to the accompanying drawings.

[0040] Wherein, the thickness and shape of each film layer in the drawings do not reflect the real scale of the thin film transistor, and the purpose is only to illustrate the content of the present invention.

[0041] An embodiment of the present invention provides a method for manufacturing a thin film transistor, such as figure 2 shown, including:

[0042] S201, sequentially forming a gate pattern, a gate insulating layer film, an active layer film and an ohmic contact layer film on the base substrate;

[0043] S202, forming a first etch stop module on the ohmic contact layer film in the channel region to be formed;

[0044] S203, forming a source-drain metal layer thin film on the base substr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More