Delay-locked loop adopting novel error lock detection circuit

A delay-locked loop and lock detection technology, applied in the field of delay-locked loops, can solve small lock-in errors, errors, etc., and achieve the effect of eliminating harmonic lock-in and high lock-in accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The present invention will be further described below in conjunction with the accompanying drawings.

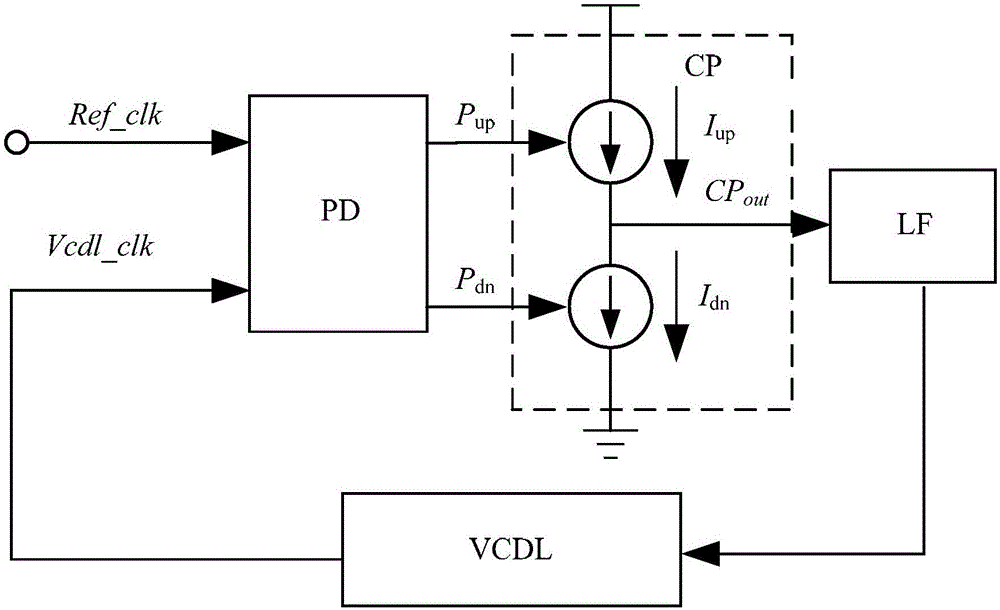

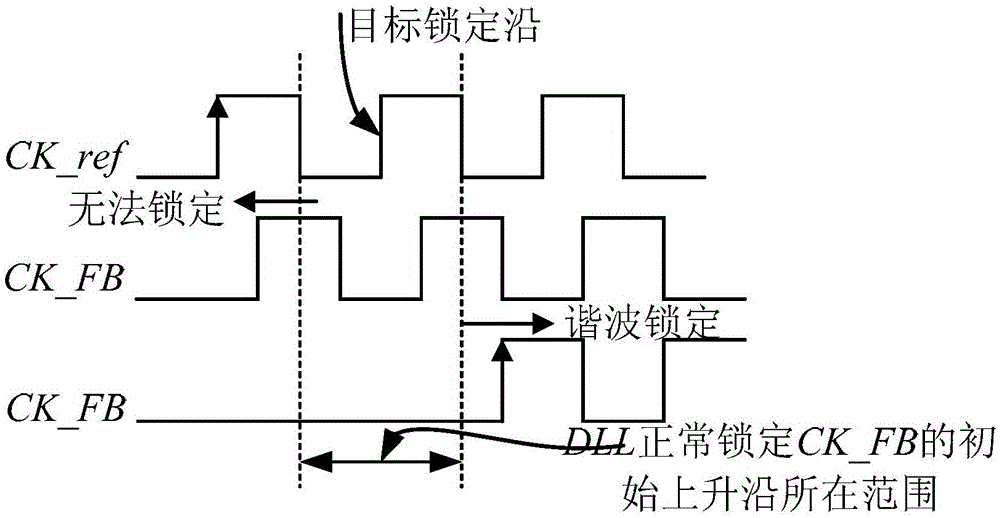

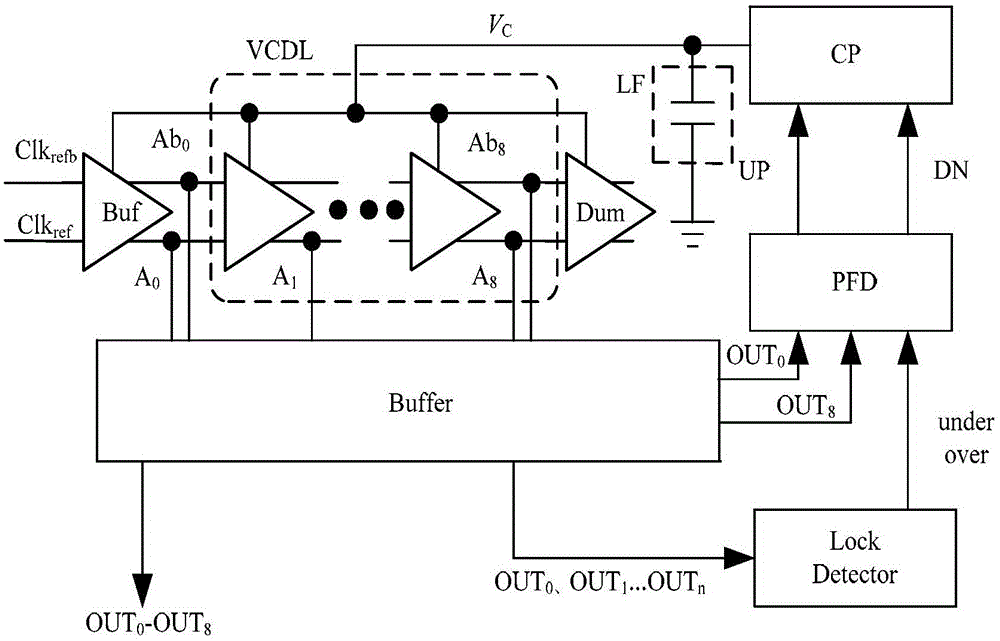

[0019] A system block diagram of a delay-locked loop using a new type of error lock detection circuit is shown in image 3 , its working timing diagram is as follows Figure 4 ; The delay-locked loop includes an error lock detection circuit, a phase detector, a charge pump, a low-pass filter and a voltage-controlled delay line, and the voltage-controlled delay line includes a differential to single-ended conversion circuit, and the voltage-controlled delay line VCDL converts the phase clock signal out 0 ~OUT 6 Input error lock detection circuit, the 0th phase clock signal OUT 0 As the reference clock input phase detector of the phase detector PFD, the last stage phase clock OUT 8 As a feedback clock input phase detector; the error lock detection circuit is used according to the input phase clock signal OUT 0 ~OUT 6 Output the under signal or over signal to the ch...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More