Chip packaging structure and manufacture method thereof, and chip packaging substrate

A technology of chip packaging structure and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve the problems of insufficient welding height, the chip cannot be firmly packaged, and the diameter of the solder ball becomes smaller. The effect of improving welding yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

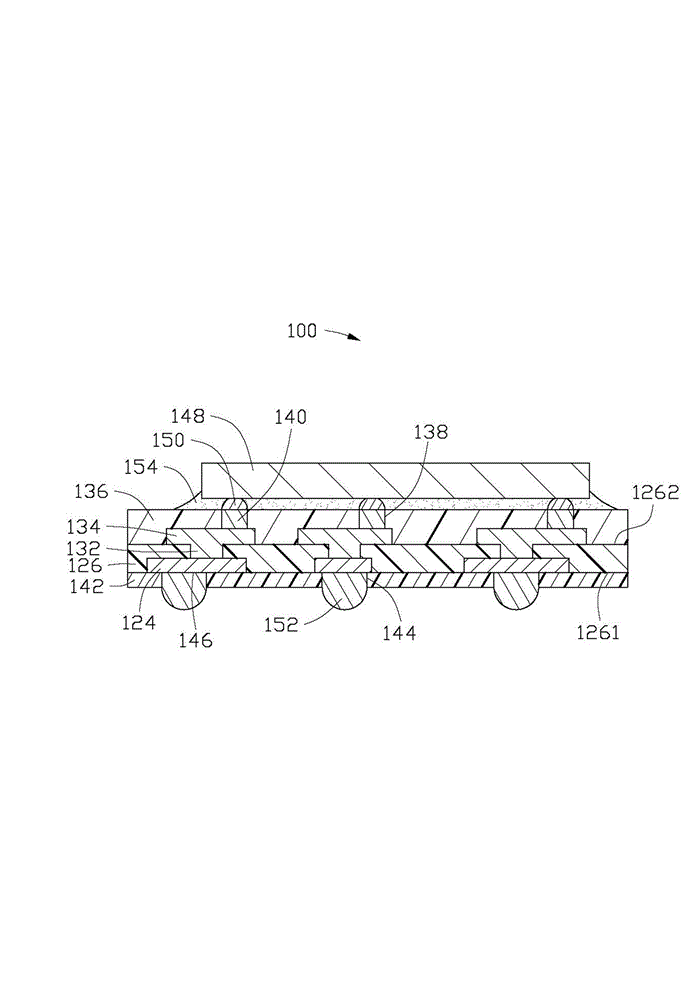

[0055] see figure 1 , the first embodiment of the present invention provides a chip packaging structure 100, including: a first dielectric layer 126, the first dielectric layer 126 includes a first surface 1261 and a second surface 1262 opposite; a first conductive Circuit layer 124, the first conductive circuit layer 124 is formed on the first surface 1261 of the first dielectric layer 126 and embedded in the first dielectric layer 126, and the first conductive circuit layer The surface of 124 away from the second surface 1262 is flush with the first surface 1261; a second conductive circuit layer 134, the second conductive circuit layer 134 is formed on the second surface 1262, the second The conductive circuit layer 134 is electrically connected to the first conductive circuit layer 124 through a plurality of first conductive columns 132; a second dielectric layer 136, the second dielectric layer 136 is formed on the second surface 1262 and On the surface of the second con...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More