Method of manufacturing transverse MOSFET device

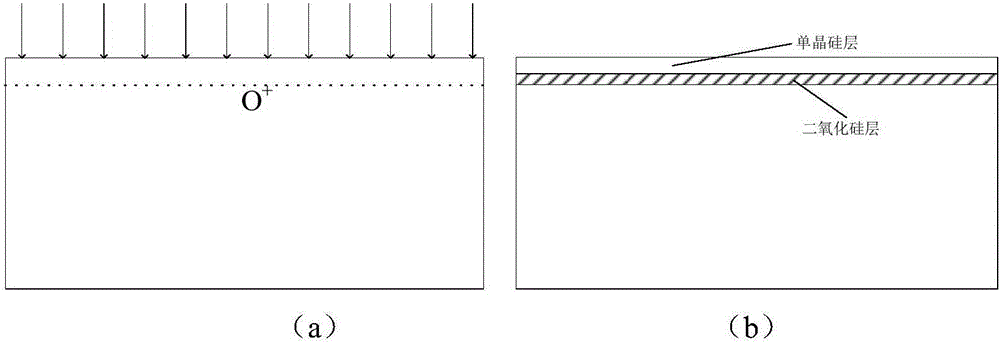

A manufacturing method and device technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as difficulty in obtaining monocrystalline silicon, achieve the effects of avoiding large leakage currents and alleviating conflicting relationships

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0049] The manufacturing process of the lateral MOSFT device in this example is as follows:

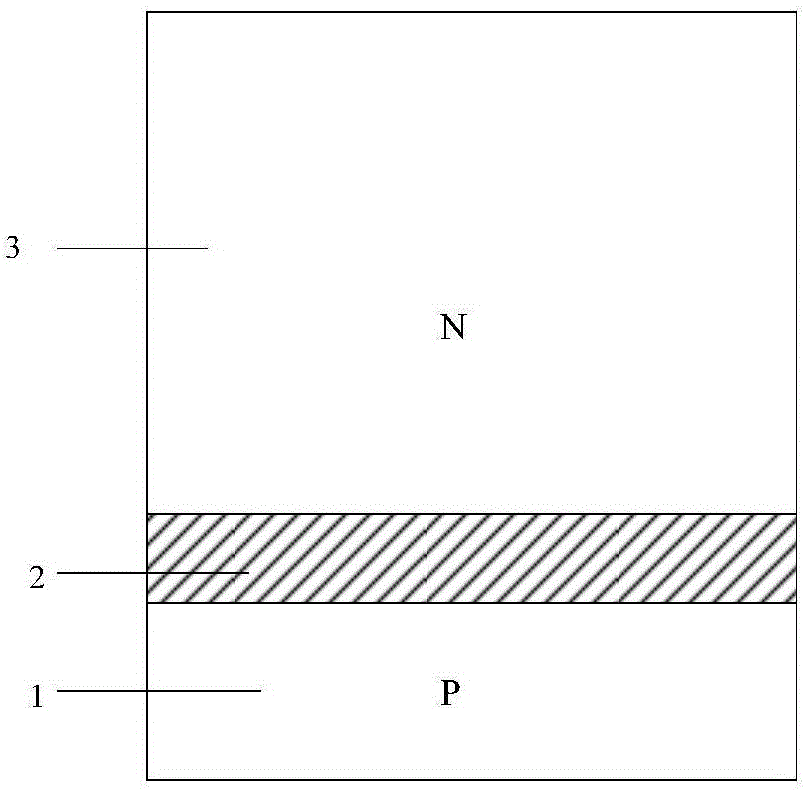

[0050] Preparation materials: SOI materials (such as figure 2 shown) includes a bottom-up substrate layer 1, a dielectric buried layer 2 and an active layer 3, wherein the conductivity type of the substrate layer 1 is not limited, and the conductivity type of the active layer 3 is the first conductivity type:

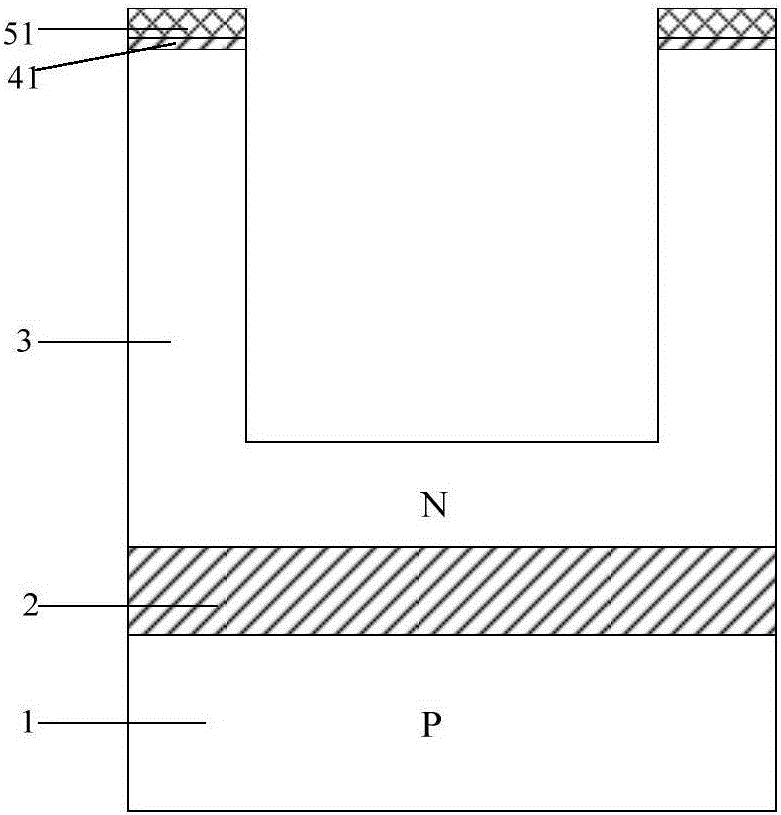

[0051] Step 1: forming a first groove. A thermal oxidation process is used to grow an oxide layer 41 on the surface of the active layer 3, and deposit Si on the surface of the oxide layer 41 3 N 4 Layer 51, according to the photolithography window, sequentially etches Si 3 N 4 layer 51, oxide layer 41 and active layer 3 to a set depth to form a first trench (such as image 3 shown);

[0052] Step 2: forming a dielectric layer inside the active layer, and leaving single crystal silicon inside the dielectric layer. Forming the gate dielectric layer adopts an inclined ion ...

Embodiment 2

[0066] The difference between this example and Example 1 is that the ions implanted in step 2 can be oxygen ions, nitrogen ions, or other ions that can react with the active layer material to form an insulating dielectric layer; the gate dielectric layer obtained by reacting the ions with silicon 6 can be silicon dioxide, silicon nitride or other insulating media.

Embodiment 3

[0068] This example differs from Example 1 in that step 6 is performed by thermal growth or deposition when filling the insulating medium 8 in the second trench; the medium grown by deposition is not as dense as the medium grown by thermal growth, and can be High temperature densification is selected, and in the case of thicker insulating medium in the first trench, multiple depositions are used to fill it.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More