Error correction method used for NAND-FLASH-adopted electric power acquisition terminal

A technology of power collection and error correction method, which is applied in the direction of response error generation, redundant code error detection, etc., can solve the problems of large memory occupation, high operation cost, and increase the production cost of power collection terminals, etc., to achieve small memory , Improve the running speed and reduce the capacity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

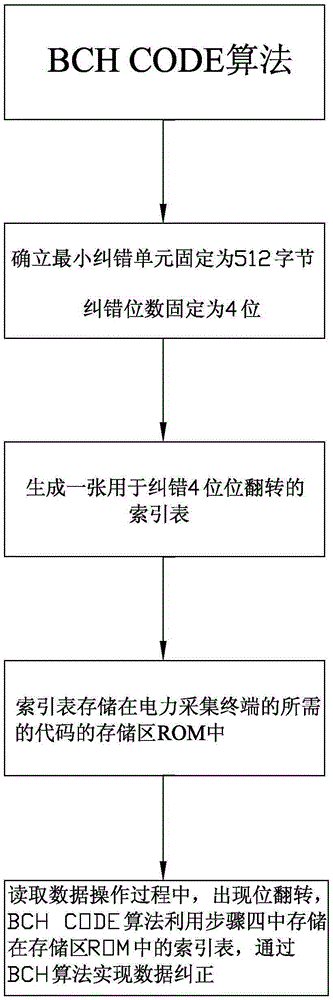

[0014] Attached below figure 1 The present invention is described in further detail.

[0015] as attached figure 1 As shown, the present invention is used for the error correction method of the power collection terminal that has adopted the NANDFLASH of MLC type,

[0016] Step 1: Establish the use of BCHCODE algorithm to realize data error correction;

[0017] Step 2: In the BCHCODE algorithm, establish that the minimum error correction unit is fixed at 512 bytes, and the number of error correction bits is fixed at 4 bits;

[0018] Step 3: Using the rule that the minimum error correction unit is fixed at 512 bytes and the number of error correction bits is fixed at 4 bits, an index table for error correction bit flipping is generated;

[0019] Step 4: Store the index table in the storage area ROM of the required code of the power collection terminal;

[0020] Step 5: When the application program on the power collection terminal writes data to the NandFlash, the BCH algorit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More