A method for detecting the consistency of rom data at the front and rear ends of a soc

A consistent, front-end and back-end technology, applied in the field of detecting the consistency of ROM data between the front and back ends of SoC, and detecting the consistency of ROM data, it can solve the problems of SoC design failure and inconsistent ROM data between the front and back ends, so as to reduce errors and improve work efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

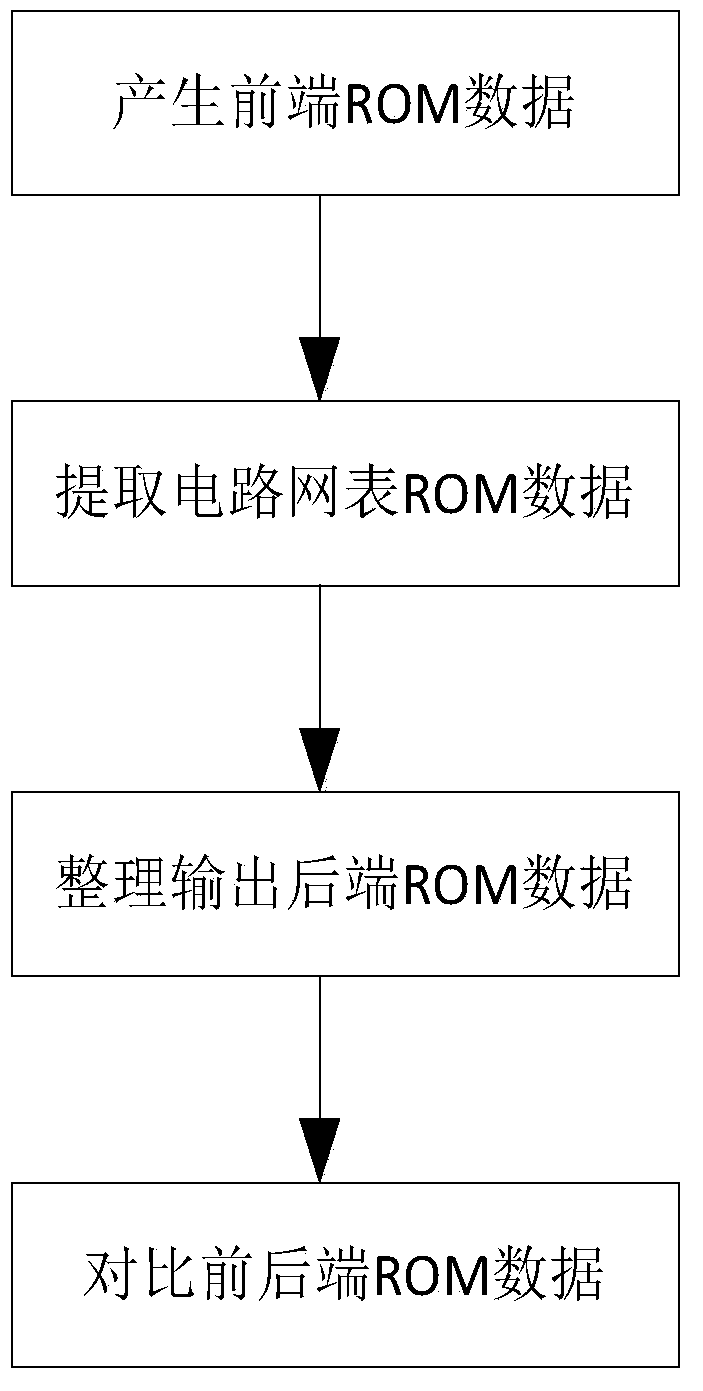

[0020] ROM consistency check means that the data in the simulation model is consistent with the data in the mask layout. Because in the standard SoC back-end design process, the consistency of the mask layout and the circuit netlist can be guaranteed through the LVS (Layout Versus Schematic) step, the ROM simulation model and the mask plate Figure 1 The consistency check can be changed to the consistency check between the simulation model and the circuit netlist.

[0021] The file format of the circuit netlist is ASCII code format, which can be used for general text processing; the circuit netlist records the transistor-level connection relationship of the read-only memory. By studying the circuit principle of the read-only memory, the circuit of data 0 and data 1 of the read-only memory Structural form, the data content of the circuit netli...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More