Method for preparing interface layer of high-k dielectric layer

A technology of dielectric layer and interface layer, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as difficulty in reducing the equivalent thickness of oxides

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be described in detail below in conjunction with specific embodiments and accompanying drawings.

[0032] In the present invention, the combination of in-situ water vapor generation ISSG and flash lamp annealing (Flash Anneal) or rapid thermal oxidation and flash lamp annealing is used for interfacial layer growth to prepare ultra-thin SiO 2 or SiON layer. The interface layer prepared by this method is denser, which can effectively suppress the interface oxide layer formed by subsequent high-K dielectric layer deposition and high-K post-annealing.

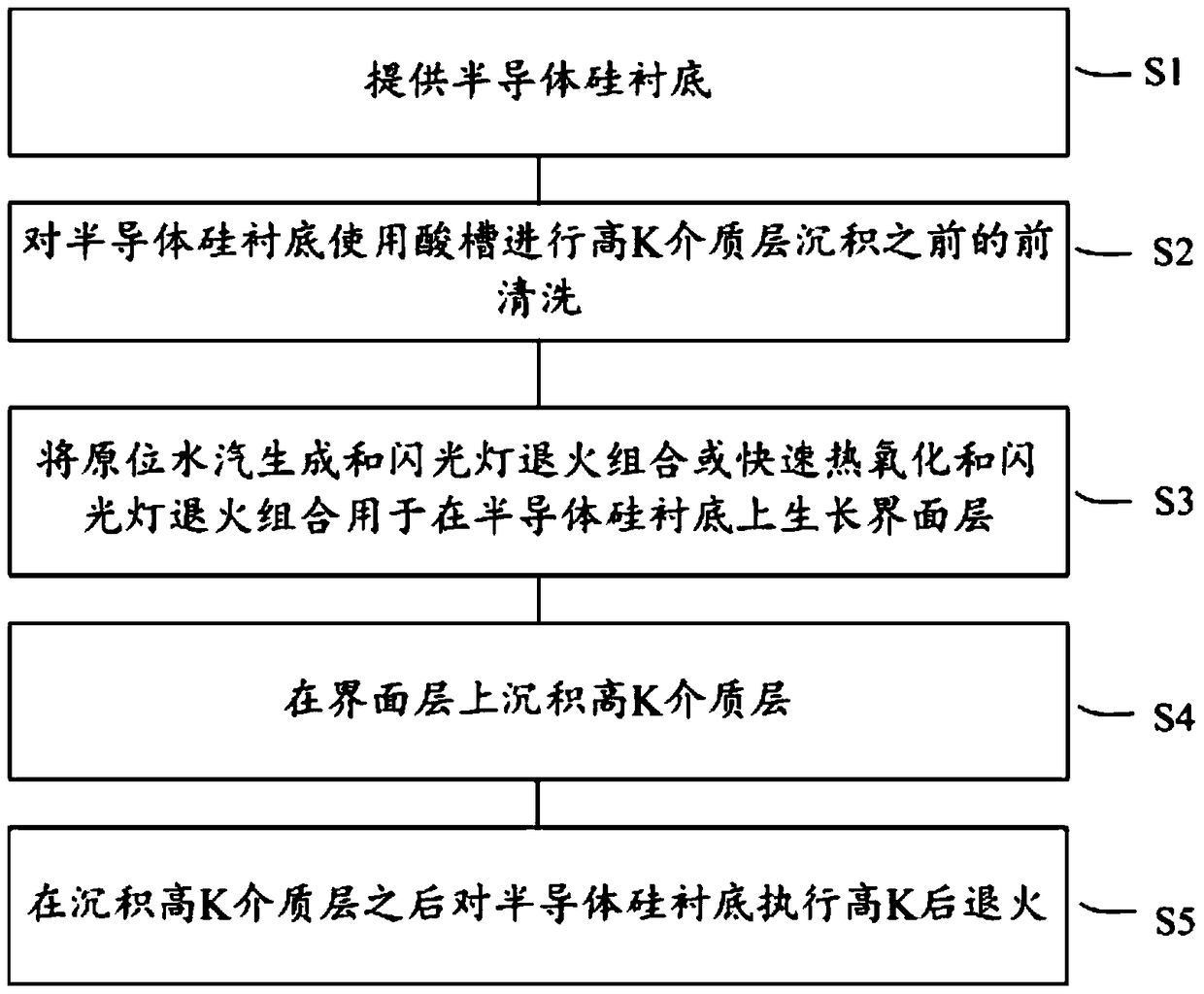

[0033] figure 1 A flow chart of a method for preparing an interface layer of a high-K dielectric layer according to a preferred embodiment of the present invention is schematically shown.

[0034] Such as figure 1 As shown, the method for preparing the interface layer of the high-K dielectric l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More