Routing method and system for non-regular three-dimensional integrated circuit network-on-chip

An integrated circuit and network-on-chip technology, which is applied in the field of routing methods and systems for irregular three-dimensional integrated circuit-on-chip networks, can solve problems such as routing algorithms that cannot be executed, communication reliability indicators that are low, and cannot be guaranteed, and reduce the average communication time. Delay, improve network throughput, reduce the effect of the probability of conflict

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0054] First, briefly introduce the technical background of the present invention, that is, two graph theory concepts introduced in the routing algorithm——Hamilton path and spanning tree.

[0055] Concept 1: Given a graph G, if there is a path that passes through every vertex in the graph exactly once, this path is called a Hamiltonian path of the graph G (EbrahimiM, DaneshtalabM, PlosilaJ. "Fault-tolerant routing algorithm for 3DNoCusing hamiltonian path strategy," inProceedings of Design, Automation & Testin Europe Conference & Exhibition. Los Alamitos: IEEE Computer Society Press, 2013, pp. 1601-1604.).

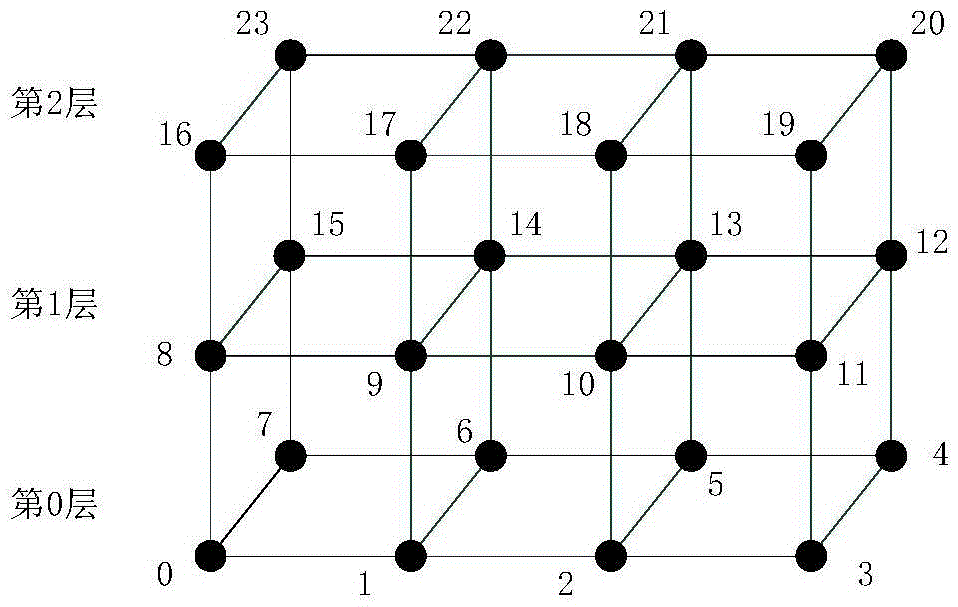

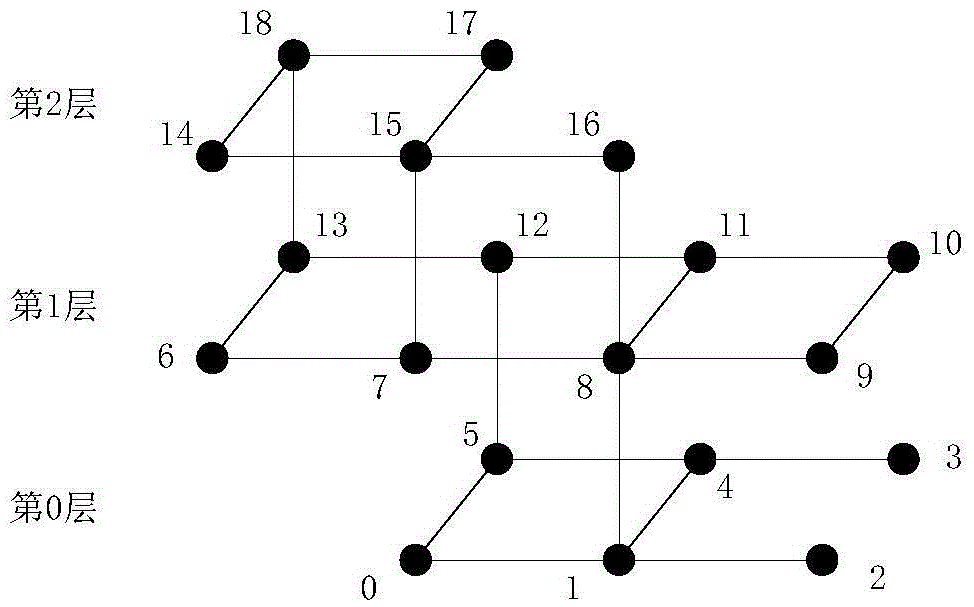

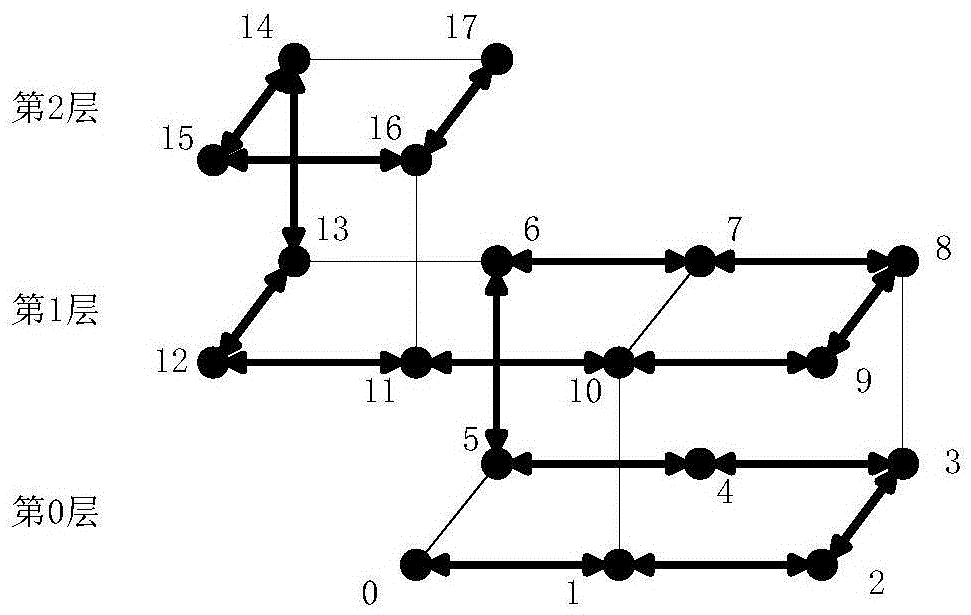

[0056] It can be seen from concept 1 that the Hamiltonian path is a basic concept in graph theory. In a regular three-dimensional Mesh structure, there must be multiple Hamiltonian paths. Arrange all nodes in ascending or descending order of numbers and pass through them exactly once, such as image 3 As shown, it is an irregular three-dimensional network-on-chip, in which...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More