MOS transistor forming method

A technology of MOS transistors and transistors, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of mutual interference of MOS transistor signals, achieve the effect of avoiding signal mutual interference and improving insulation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

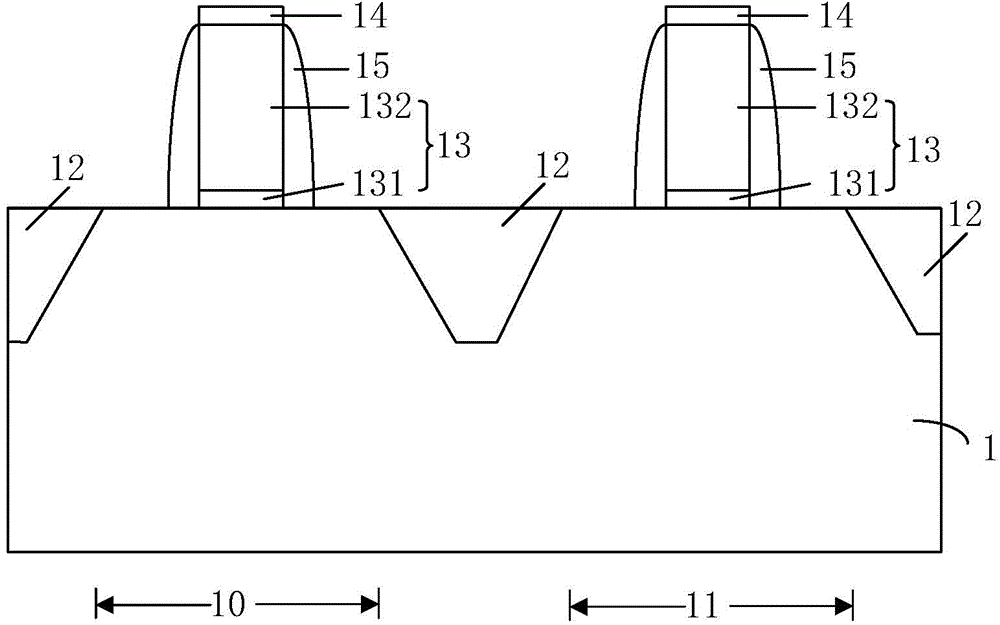

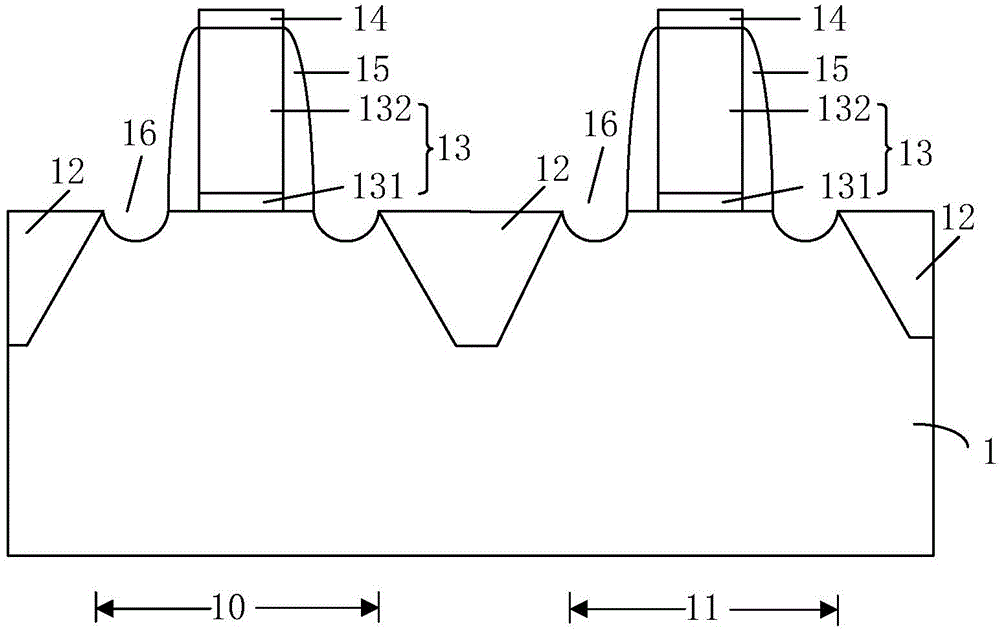

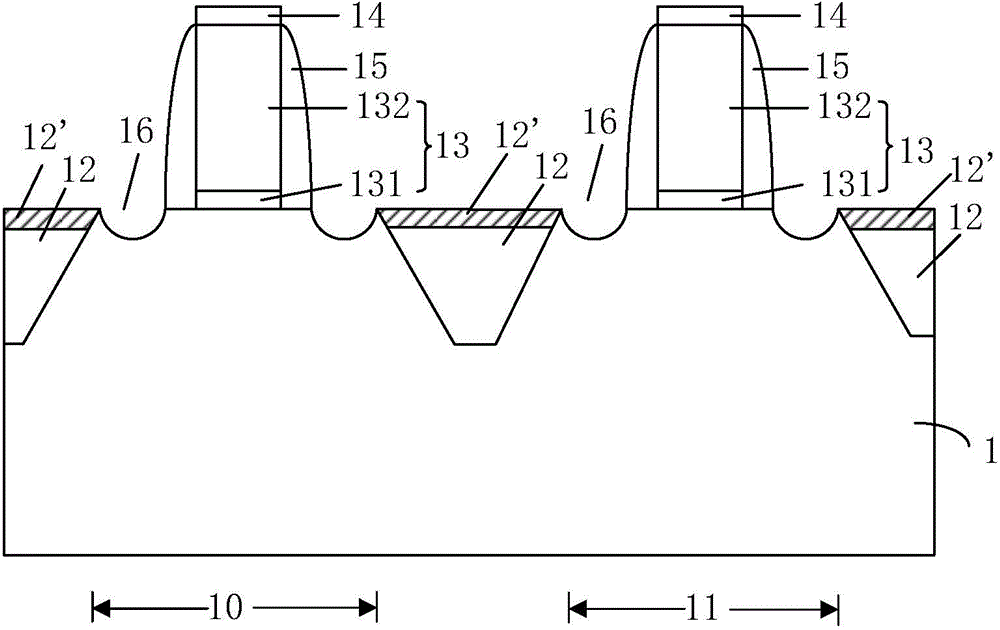

[0027] As mentioned in the background art, mutual interference often occurs between adjacent MOS transistors manufactured by existing processes. For the problems referred to above, the inventor has analyzed and found that the cause of it is: before adopting alkaline solution to corrode the bowl-shaped groove to form the sigma-shaped groove, it is necessary to use HF acid solution to corrode the semiconductor substrate to remove the oxide on the silicon surface , in the above process, the HF acid will corrode the shallow trench isolation structure at the same time, causing holes in it, and the above holes will cause the insulation performance of the shallow trench isolation structure to deteriorate. In addition, when filling the compressive stress material or tensile stress material in the sigma-shaped groove to form the source and drain regions, it is also possible to form a conductive source and drain region filling material at the shallow trench structure removed by etching, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More