Multiplying unit used for RFID (Radio Frequency Identification) security chip, and implementation method

A technology of security chip and implementation method, which is applied to recording carriers used in machines, instruments, and electrical digital data processing. The effect of reducing critical paths, reducing circuit delays, and increasing operating speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

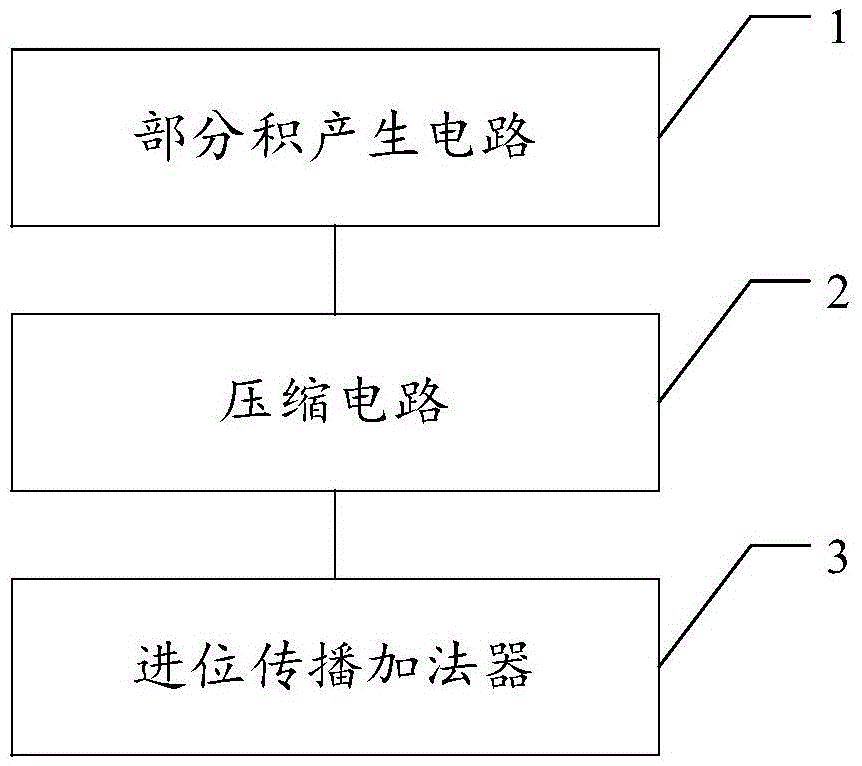

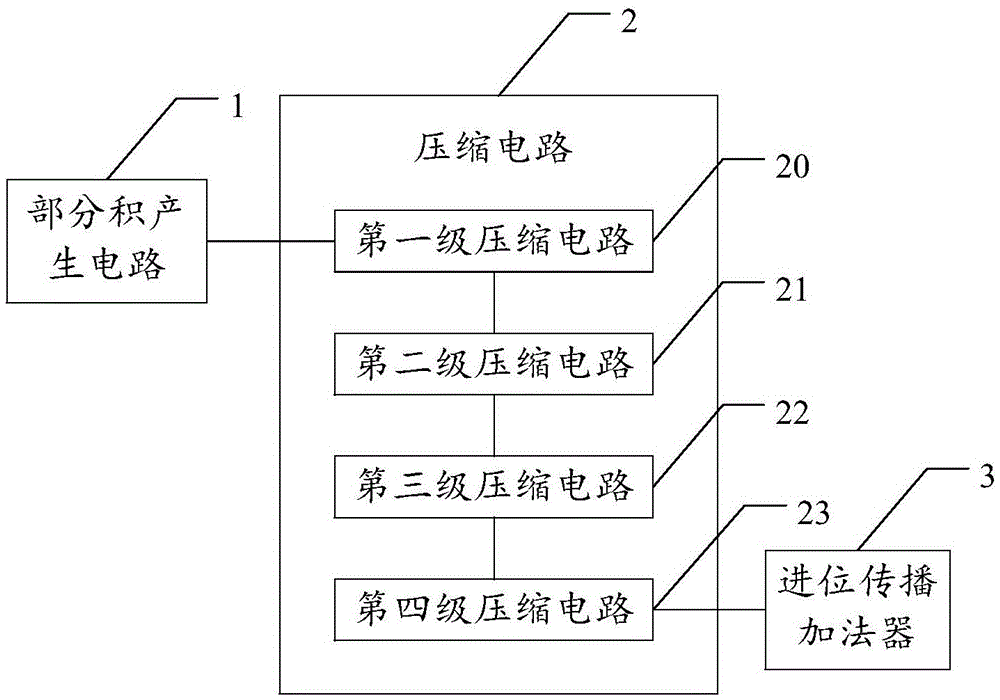

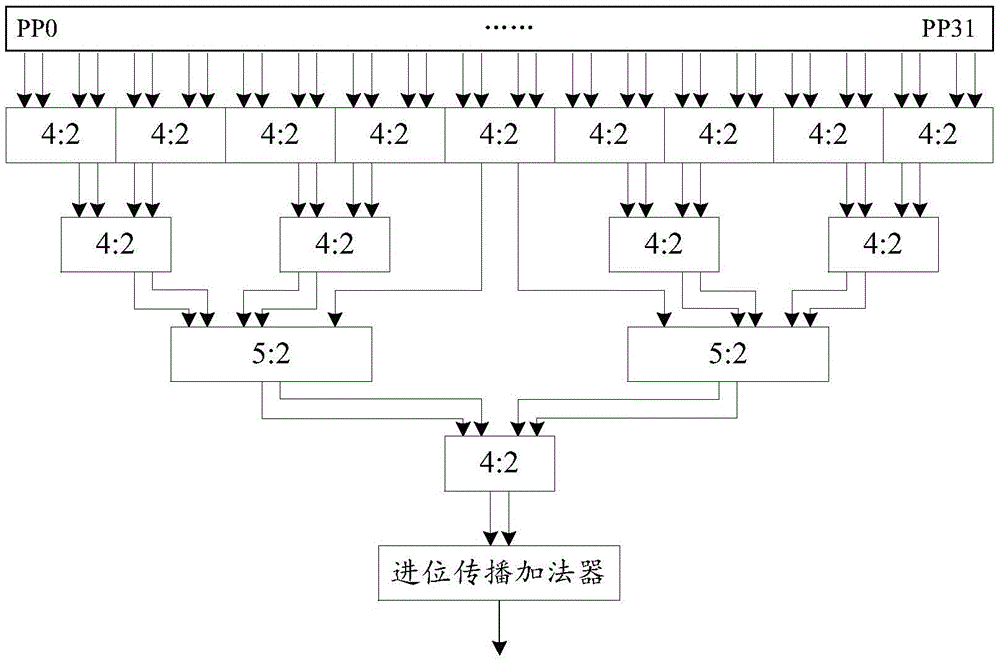

[0036] figure 1 It is a schematic diagram of the structural composition of the multiplier for the RFID security chip of the embodiment of the present invention, as figure 1 As shown, the multiplier consists of:

[0037] A partial product generation circuit 1, used to generate a partial product and input the partial product to the compression circuit;

[0038] The compression circuit 2 is used to receive the partial product generated by the partial product generat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More