Statistical timing analysis method used for post-silicon adjustable register circuits

A timing analysis, register technology, applied in instrumentation, computing, electrical digital data processing, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0097] Embodiment 1 is used to illustrate the main steps of the method of the present invention.

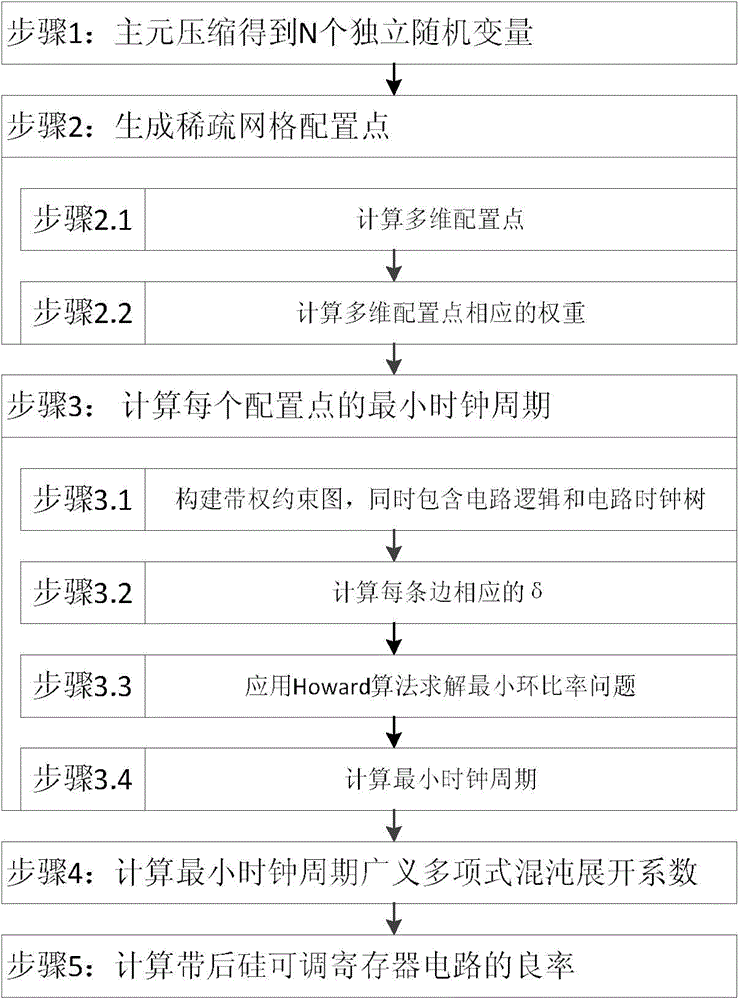

[0098] The present invention is used for the statistical timing analysis method of the post-band silicon adjustable register circuit. The implementation steps are as follows: figure 1 shown.

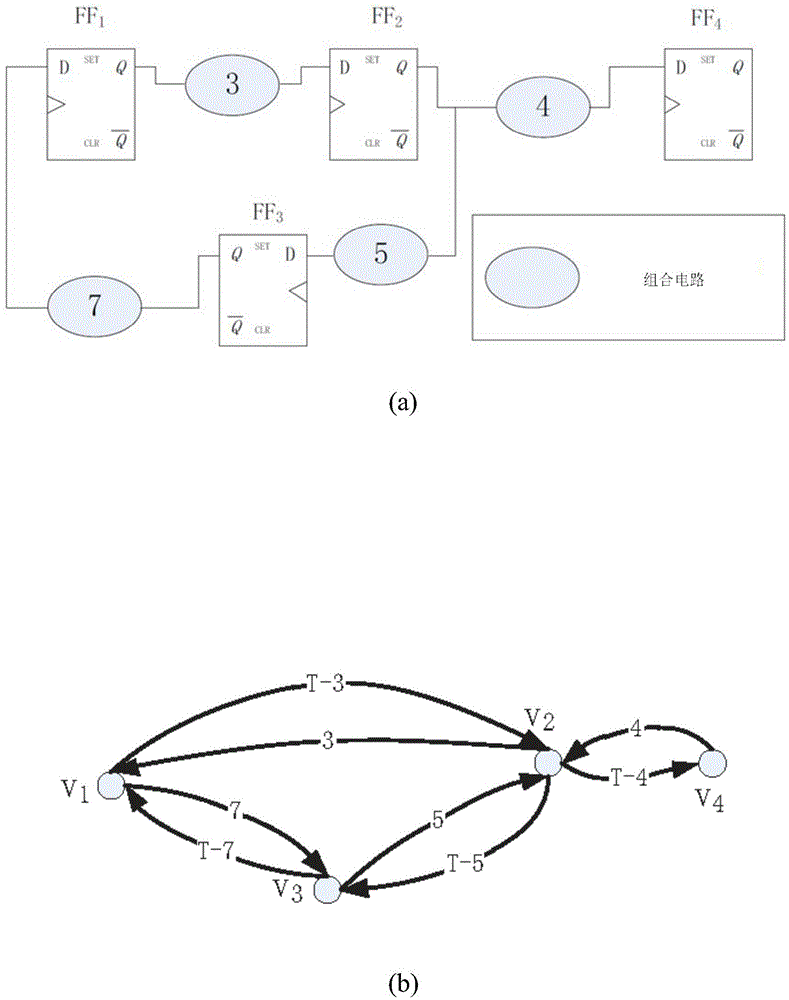

[0099] image 3 (a) is an example of a sequential circuit with logic path delays. image 3 (b) is its corresponding timing constraint. image 3 Each vertex in (b) represents image 3 A register in (a). image 3 Each logical path in (a) corresponds to image 3 (b) Two timing constraint edges. E.g, image 3 (a) from FF 1 to FF 2 The logical path delay for is 3. from FF 1 to FF 2 The maximum and minimum delays are both 3. So, image 3 In (b), two corresponding timing constraint edges should be added. Edge (1, 2) corresponds to the setup time constraint as:

[0100] t i -t j ≤T-3.

[0101] Edge (1, 2) corresponds to the hold time constraint as:

[0102] t i -t j ≤3.

[0...

Embodiment 2

[0122] Example 2 is used to show that the statistical timing analysis method proposed by the present invention can significantly reduce the program running time while obtaining comparable accuracy to the existing method.

[0123] In this embodiment, the settings similar to those in [17] are adopted. The results obtained by the Monte Carlo method with 10,000 sampling points are used as the comparison standard for judging the accuracy. The test circuit is from ISCAS89, and the basic unit gates in the test circuit are mapped to the SMIC 65nm unit library. In this embodiment, each register has a post-silicon adjustable register, and the adjustment range of each register is set to 0.3 times the longest path delay of the circuit. In the Monte Carlo method and the method of the present invention, 6 random variables (transistor length, transistor width, threshold voltage of NMOSFET and PMOSFET) are used to model process fluctuations. The standard deviation of these independent rando...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More