Preparation method of multi-chip parallel illumination module

A lighting module and multi-chip technology, which is applied in the direction of electrical components, electric solid devices, circuits, etc., can solve the problems of poor uniformity, inconsistent height, and the inability to pre-test production efficiency of ordinary integrated parallel chips, so as to achieve consistent uniformity and reduce Difficulty in encapsulation, solving the effect of low encapsulation efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

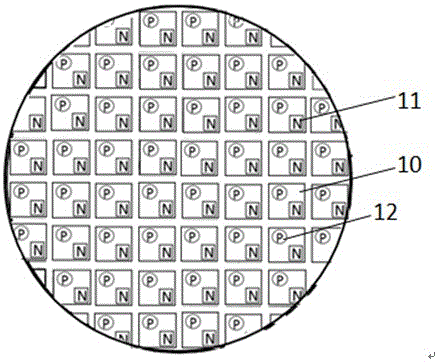

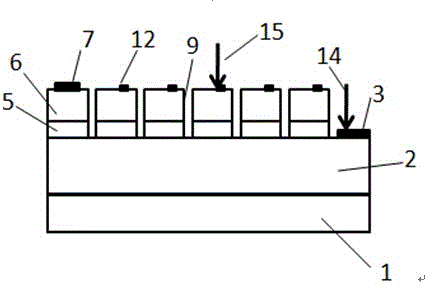

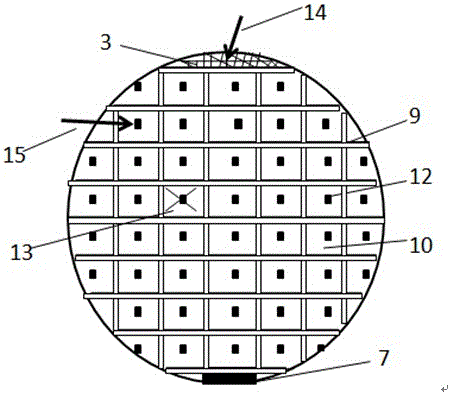

[0037] The multi-chip parallel lighting module of the present invention is prepared by using GaN blue light epitaxial wafers. The structure of the GaN blue light epitaxial wafers includes a sapphire substrate 1, an N-type GaN layer 2, a quantum well active region 5 and a P-type GaN from bottom to top. Layer 6. Concrete preparation method comprises the following steps:

[0038] (1) Preparation of N electrode pad 3

[0039] Such as figure 2 and image 3 As shown, using the existing photolithography mask technology to make an N electrode pattern on one end of the GaN blue epitaxial wafer, and etch from the P-type GaN layer 6 to the N-type GaN layer 2, as the N-electrode pad of the parallel lighting module 3.

[0040] (2) Preparation of electrode pads

[0041] The P electrode pads referred to in this step include the P electrode pads of the entire parallel lighting module (the entire module P electrode pads) and the P electrode pads on the chip unit 10 (chip unit P electrode...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More