Method of forming memory device

A storage device and device layer technology, applied in the direction of semiconductor devices, electric solid state devices, electrical components, etc., can solve the problem of large space area, achieve the effect of reducing space area, reducing bit cost, and increasing bit density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] As mentioned in the background art, the existing three-dimensional NAND gate flash memory storage unit still occupies a relatively large space area.

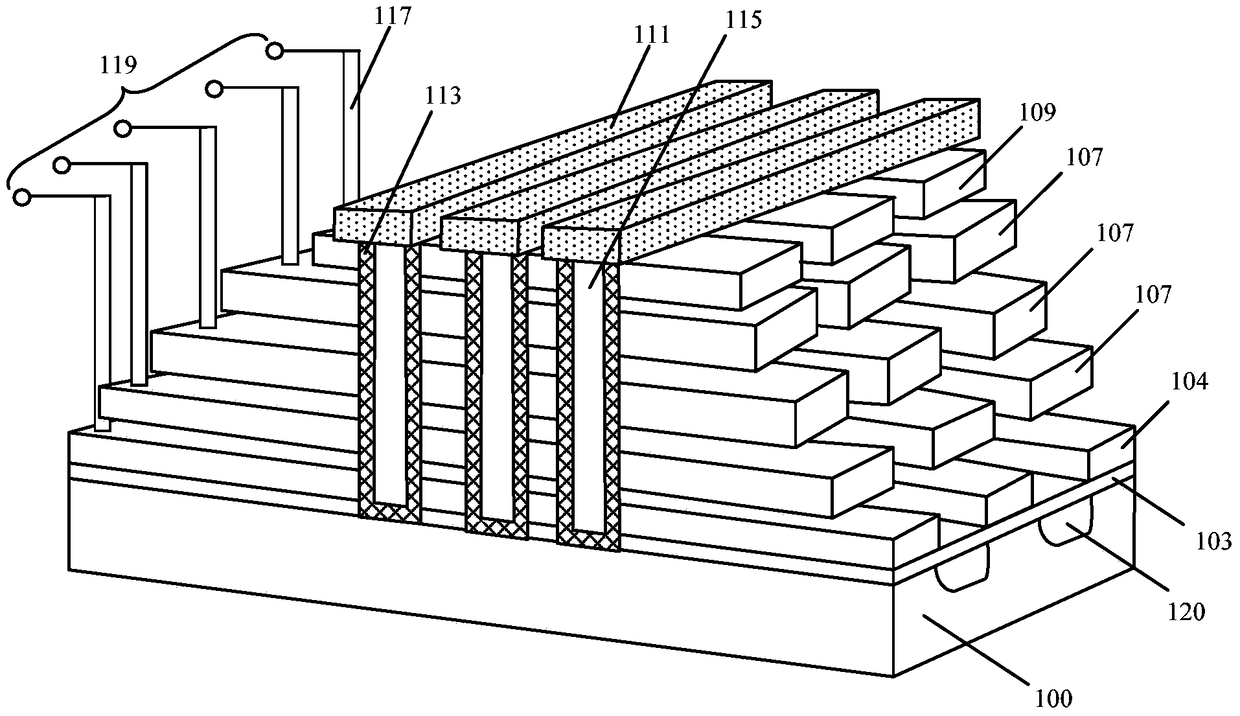

[0035] Please continue to refer figure 1 The pattern size of the overlapping control gates 107 projected on the surface of the substrate 100 decreases layer by layer from bottom to top, so that each control gate layer 107 can expose part of the control gate layer of the next layer, so that it can be used in each layer. A word line plug 117 is formed on the surface of the layer control gate layer 107 , and the word line plug 117 is only connected to one layer of the control gate layer 107 and does not contact with several other layers of control gate layers 107 .

[0036]After research, it is found that a process for forming a flash storage unit of a three-dimensional NAND gate in an embodiment of the present invention includes: providing a substrate; forming several overlapping composite layers on the surface of the subst...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More