Transverse diffusion field effect transistor and manufacturing method therefor

A technology for field effect transistors and manufacturing methods, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., to achieve the effects of reducing the JFET effect, increasing the current conduction area, and reducing the on-resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

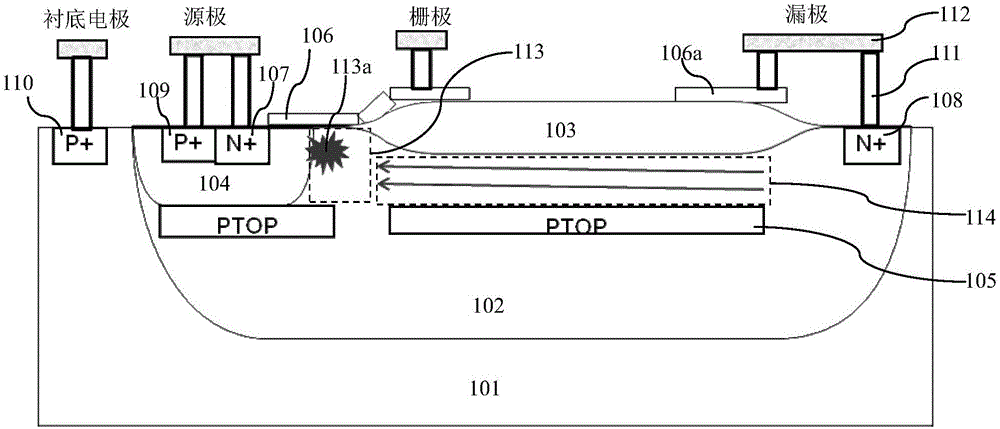

[0072] like Figure 4 As shown, it is a schematic structural diagram of a lateral diffusion field effect transistor according to an embodiment of the present invention; taking an N-type device as an example, a lateral diffusion field effect transistor according to an embodiment of the present invention includes:

[0073] An N-type doped drift region 2 is formed in a P-type semiconductor substrate such as a silicon substrate 1; in Embodiment 1 of the present invention, the drift region 2 is directly composed of an N-type epitaxial layer 2, and the N-type epitaxial layer 2 is formed on the surface of the semiconductor substrate 1.

[0074] The P-type doped channel region 4 is formed in the drift region 2 of the semiconductor substrate 1 .

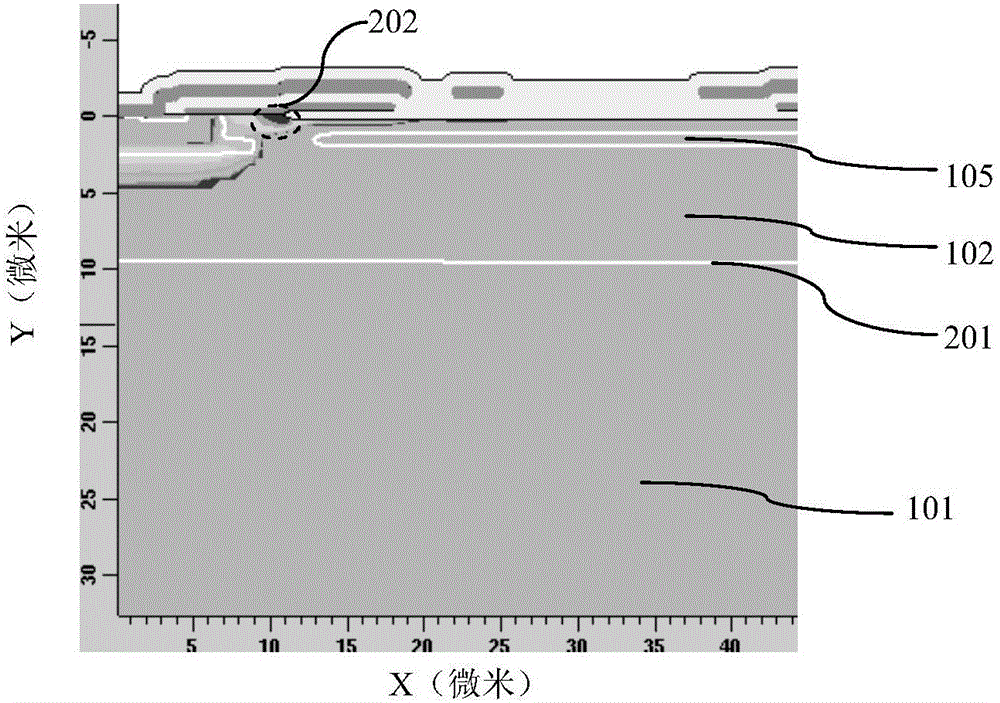

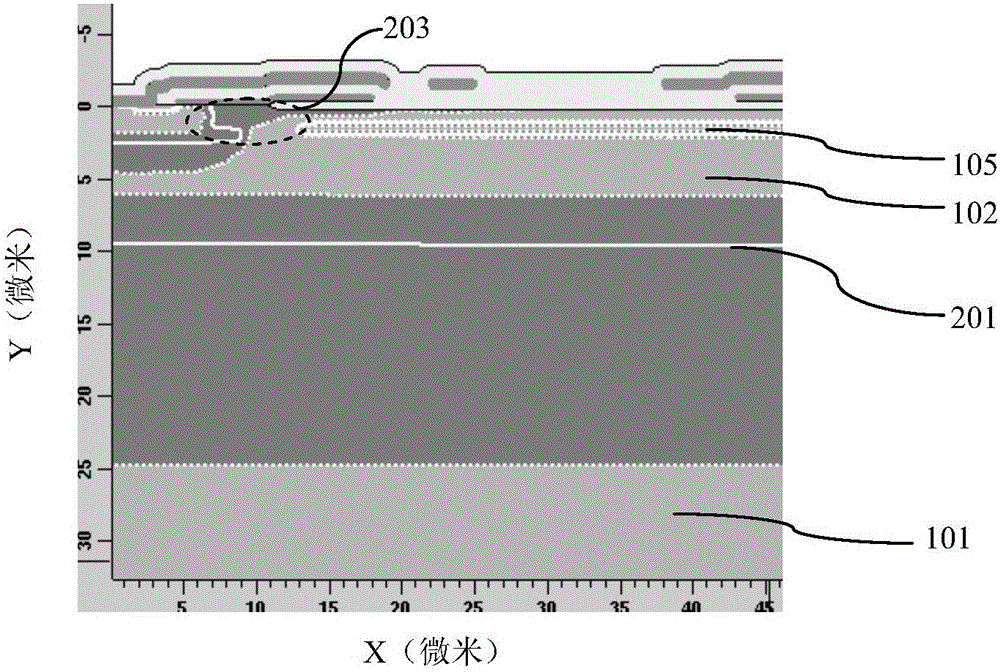

[0075] A P-type doped buried layer, namely PTOP, is formed in the drift region 2, and the buried layer is divided into multiple buried layer segments with different concentrations and different depths, Figure 4 The buried layer segment 5a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More