Semiconductor on insulator (SOI) lateral metal-oxide-semiconductor field-effect-transistor (MOSFET) device and integrated circuit

A technology of integrated circuits and devices, which is applied in the field of SOI lateral MOSFET devices and integrated circuits, can solve problems such as poor process repeatability and sensitivity, and achieve the effects of reducing process costs, increasing withstand voltage, and improving withstand voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

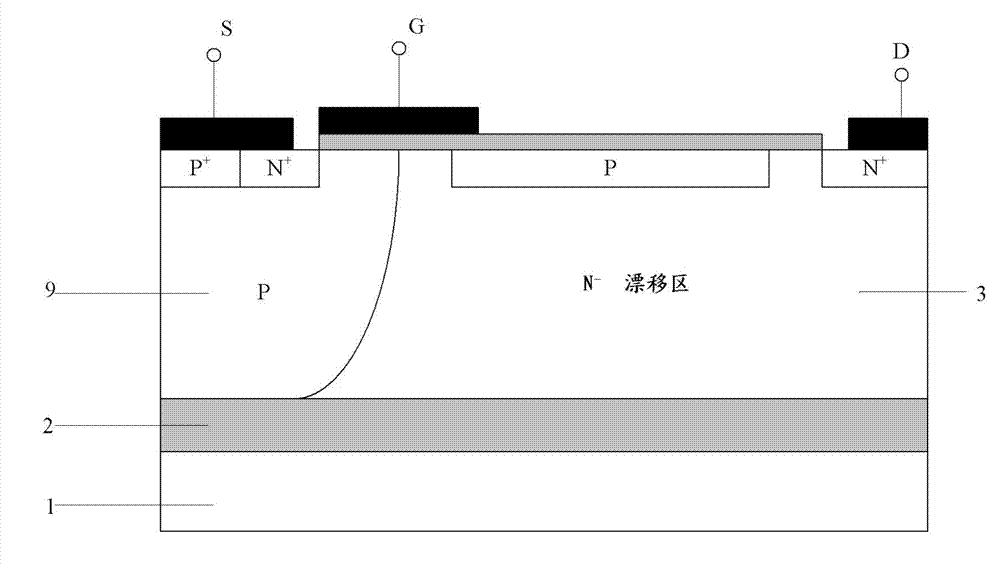

[0055] Fig. 4(a) is a cross-sectional view showing the cell structure of the N-channel double-gate SOI lateral MOSFET device in which the P-type semiconductor buried layer 4 and the body region 9 are in contact with each other according to the present invention. As shown in Figure 4(a), in an SOI lateral MOSFET device, a substrate layer 1, a dielectric buried layer 2, and an active layer 3 are sequentially stacked from bottom to top, and the active layer 3 has surfaces respectively located on the active layer 3 And the body region 9 and the drain region 12 separated from each other, and the planar gate channel region 14 ′, source region 11a, body contact region 10 and The source region 11b, the active layer 3 located between the body region 9 and the drain region 12 is a drift region, its conductivity type is opposite to that of the body region 9, and the active layer 3 is provided with a semiconductor buried layer 4 below its surface, The semiconductor buried layer 4 and the ...

Embodiment 2

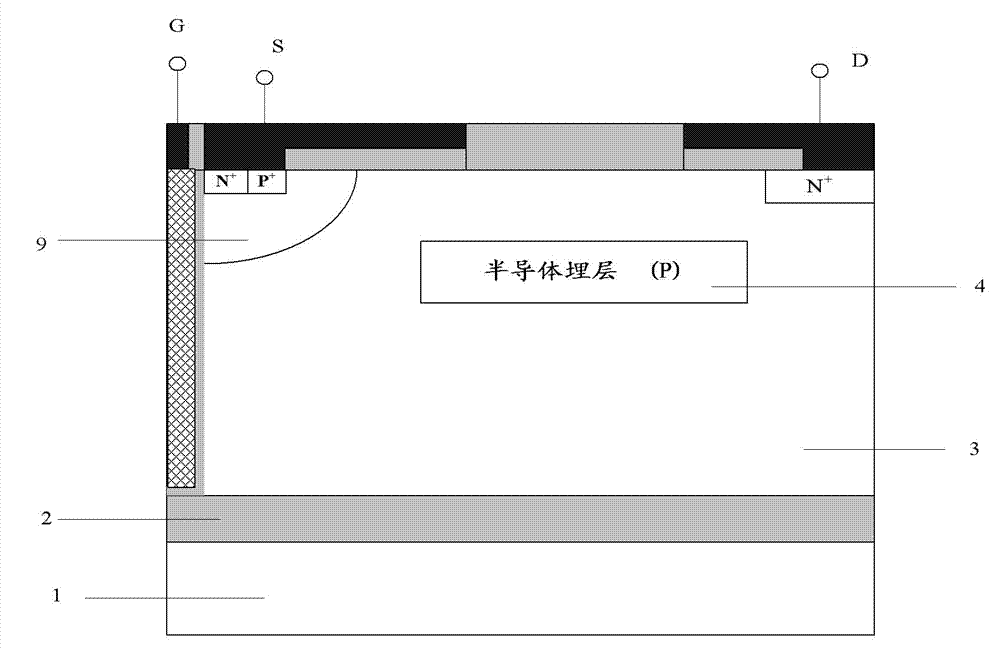

[0058] Figure 5 It is a cross-sectional view showing the cell structure of the P-channel double-gate SOI lateral MOSFET device with the N-type semiconductor buried layer 4 of the present invention. Such as Figure 5 As shown, the only difference between it and FIG. 4(a) is that the active layer 3, semiconductor buried layer 4, source regions 11a, 11b, drain region 12, body region 9 and body contact region 10 of the device in this example are The conductivity type of the material is opposite to that of the corresponding region of the N-channel double-gate SOI lateral MOSFET device, and the same technical effect as that of Embodiment 1 can also be obtained. That is to say, the double-gate MOS controlled lateral SOI device with semiconductor buried layer of the present invention can be used to manufacture both N-channel devices and P-channel devices.

Embodiment 3

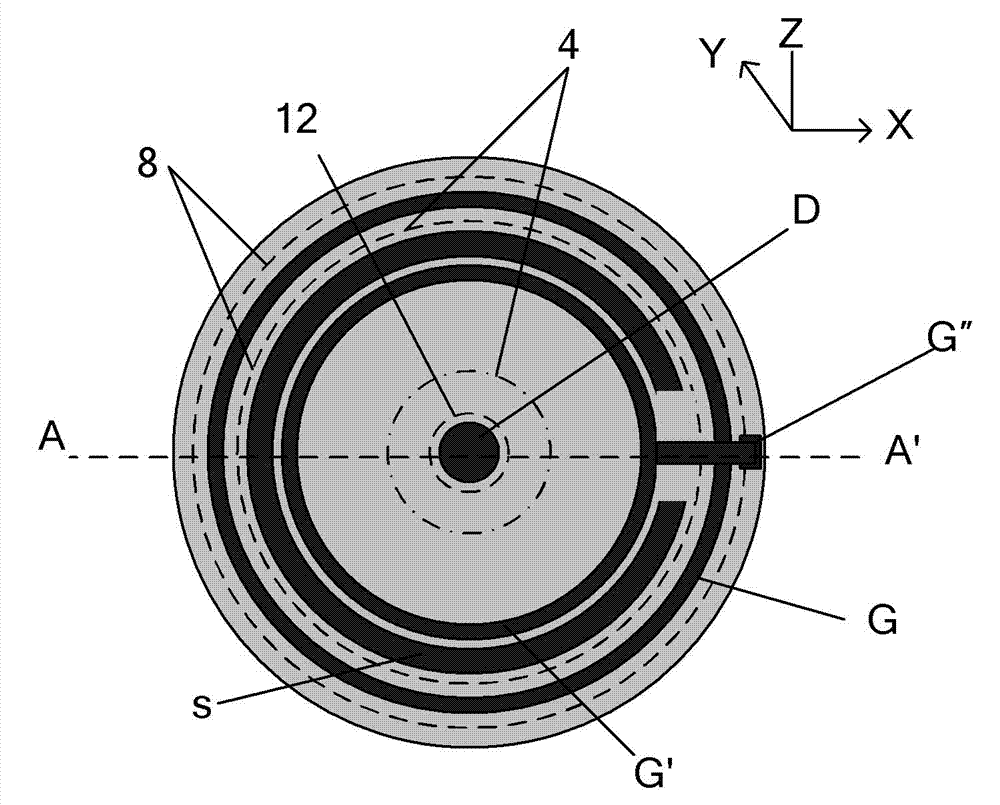

[0060]In this embodiment 3, the top view of the device is a symmetrical structure, the drain region 12 is located at the center of the device, and from the drain region 12 to the outside are the semiconductor buried layer 4, the body region 9, the source region 11a, the body contact region 10, and the source region 11b and the trench gate structure 8, the trench gate structure 8 is located at the periphery of the device. Below, according to Figure 6 and Figure 7 , the present embodiment 3 will be described.

[0061] Figure 6 It is a schematic diagram showing the cell layout of an SOI lateral MOSFET device with an axisymmetric structure of the present invention, that is, the xz plane view, wherein AA' is along the x direction, and the vertical direction perpendicular to the paper is the y direction. Should Figure 6 Take the circular figure as an example to describe the axisymmetric structure. The drain electrode D is located at the center of the device. The device tak...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More