CMOS Transistor Junction Regions Formed By A CVD Etching And Deposition Sequence

A junction and crystalline technology, used in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as large diffusion resistance and insufficient optimization of diffusion resistance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

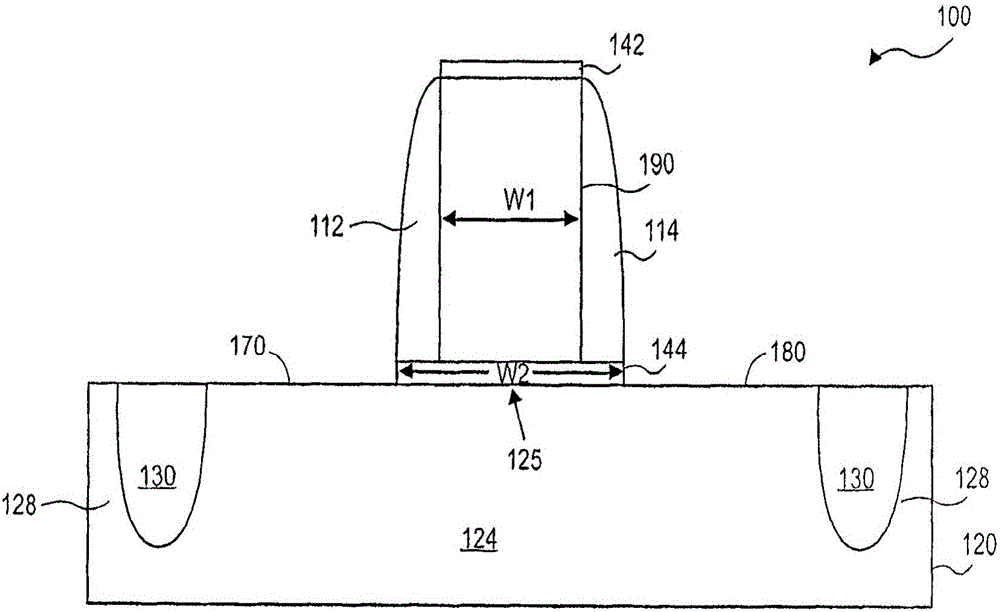

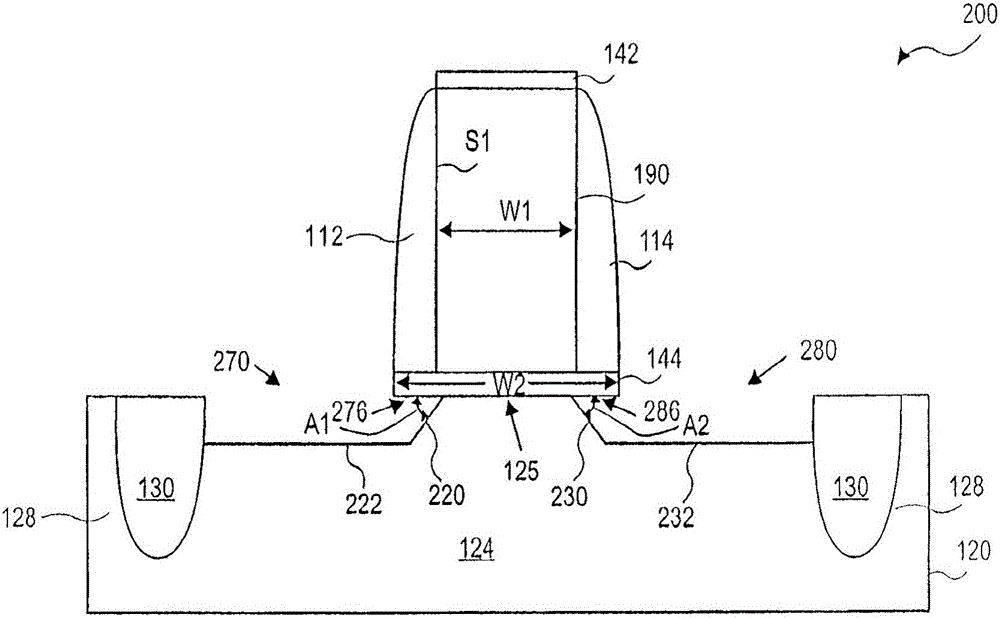

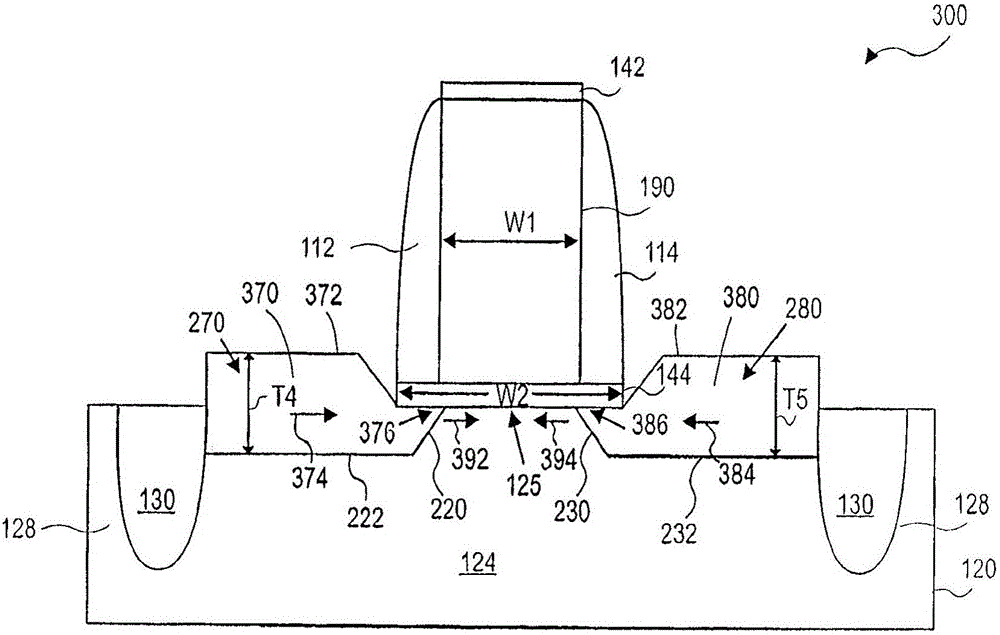

[0024] Locally strained transistor channel regions can be accomplished by forming source-drain regions in the channel region of a MOS transistor by selective epitaxy of a strain-generating material. Such a process flow may include etching substrate material in a source-drain region of a transistor in one process operation with an etch reactor. Subsequent operations may include replacing the removed material with Si alloy material in the deposition reactor. The etch reactor and the deposition reactor may be physically distinct and separate. Thus, before starting the Si alloy deposition process, the substrate must be removed from the etch reactor and exposed to atmospheric pressure. The above Si alloy can be pure Si or Si 1-x Ge x or Si 1-x C x , and can be undoped or doped with P-type or N-type dopants. The deposition process described above may be selective or non-selective. According to the examples presented herein, the etch reactor and the deposition reactor may be p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More