One-bit full adder based on Fin FET mixed logic

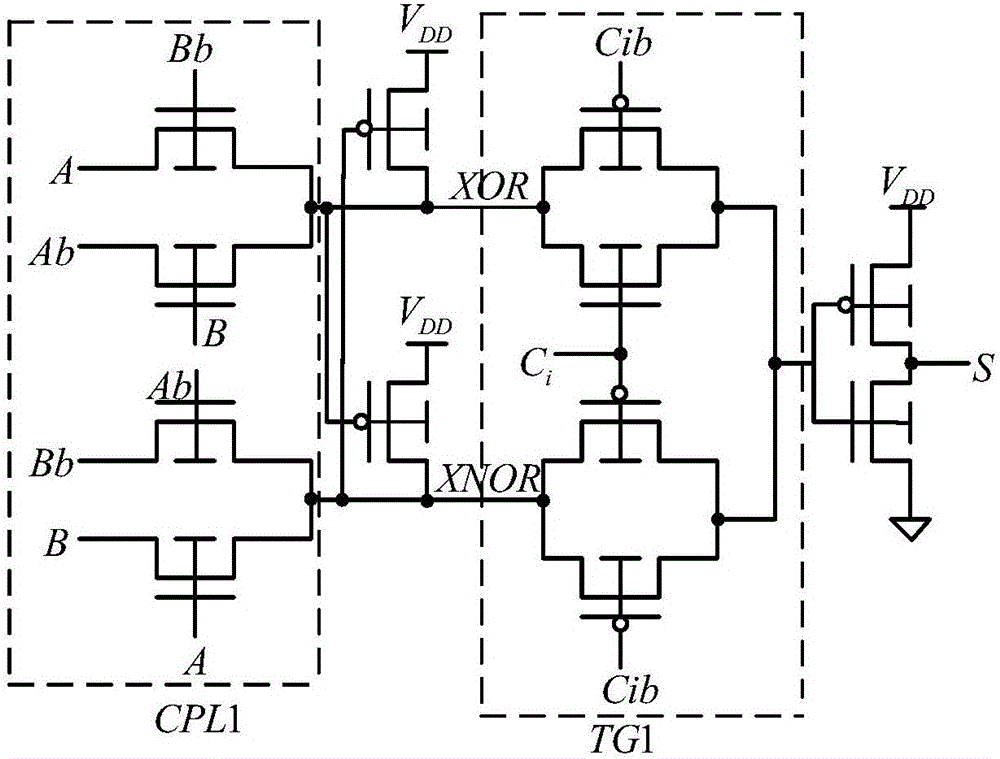

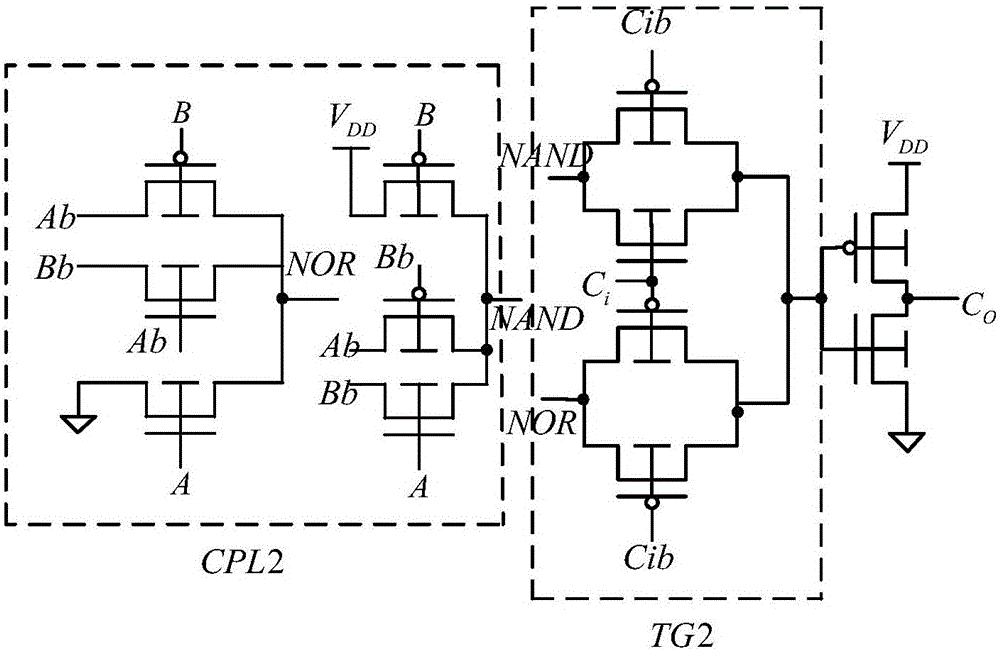

A technology of mixed logic and full adder, which is applied in the direction of logic circuits with logic functions, etc., can solve the problems of large power consumption and power consumption delay product, increase of key jump nodes, increase of circuit power consumption and delay, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

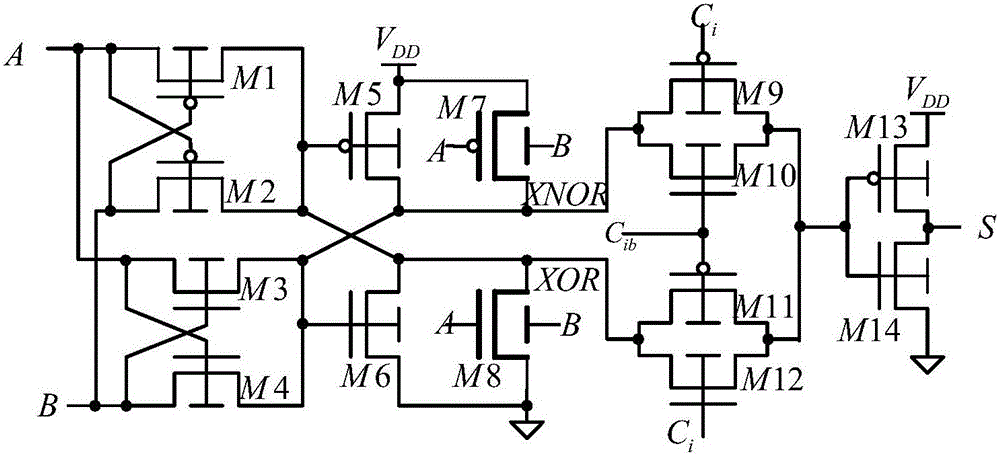

[0015] Embodiment one: if image 3 with Figure 4As shown, a one-bit full adder based on FinFET hybrid logic includes a summation output circuit and a carry output circuit. The summation output circuit includes a first FinFET tube M1, a second FinFET tube M2, a third FinFET tube M3, and a first FinFET tube M3. The fourth FinFET tube M4, the fifth FinFET tube M5, the sixth FinFET tube M6, the seventh FinFET tube M7, the eighth FinFET tube M8, the ninth FinFET tube M9, the tenth FinFET tube M10, the eleventh FinFET tube M11, the tenth The second FinFET tube M12, the thirteenth FinFET tube M13 and the fourteenth FinFET tube M14, the first FinFET tube M1, the second FinFET tube M2, the fifth FinFET tube M5, the seventh FinFET tube M7, the ninth FinFET tube M9, the The eleventh FinFET tube M11 and the thirteenth FinFET tube M13 are P-type FinFET tubes, the third FinFET tube M3, the fourth FinFET tube M4, the sixth FinFET tube M6, the eighth FinFET tube M8, the tenth FinFET tube M1...

Embodiment 2

[0016] Embodiment two: if image 3 with Figure 4As shown, a one-bit full adder based on FinFET hybrid logic includes a summation output circuit and a carry output circuit. The summation output circuit includes a first FinFET tube M1, a second FinFET tube M2, a third FinFET tube M3, and a first FinFET tube M3. The fourth FinFET tube M4, the fifth FinFET tube M5, the sixth FinFET tube M6, the seventh FinFET tube M7, the eighth FinFET tube M8, the ninth FinFET tube M9, the tenth FinFET tube M10, the eleventh FinFET tube M11, the tenth The second FinFET tube M12, the thirteenth FinFET tube M13 and the fourteenth FinFET tube M14, the first FinFET tube M1, the second FinFET tube M2, the fifth FinFET tube M5, the seventh FinFET tube M7, the ninth FinFET tube M9, the The eleventh FinFET tube M11 and the thirteenth FinFET tube M13 are P-type FinFET tubes, the third FinFET tube M3, the fourth FinFET tube M4, the sixth FinFET tube M6, the eighth FinFET tube M8, the tenth FinFET tube M1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More