Self-adaptive duty cycle detection and adjustment receiver and control method thereof

A technology of adaptive duty ratio and control method, which is applied in the direction of pulse generation, electrical components, and electric pulse generation, and can solve signal duty ratio deviation, system function failure, input signal duty ratio deviation that cannot be corrected and adjusted, etc. question

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The present invention will be further described in detail below in conjunction with specific embodiments, which are to explain rather than limit the present invention.

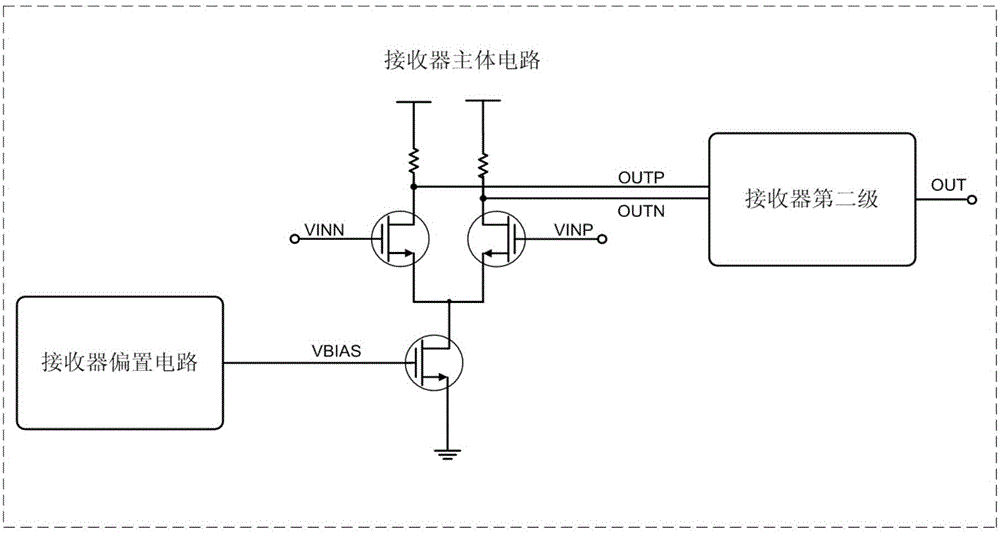

[0036] The invention solves the problem of signal integrity restoration of the input signal in the receiver (Receiver), and provides a detection and adjustment circuit and method for correcting the duty ratio of the DRAM input signal.

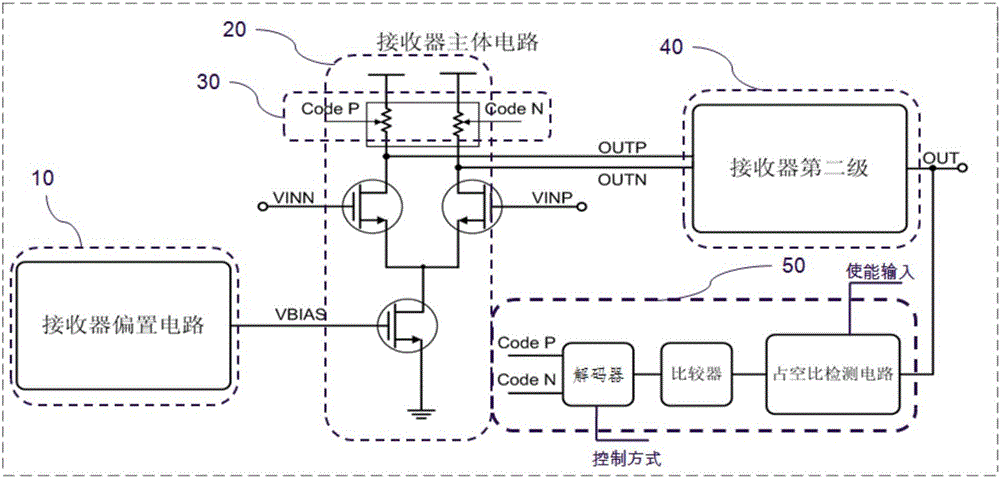

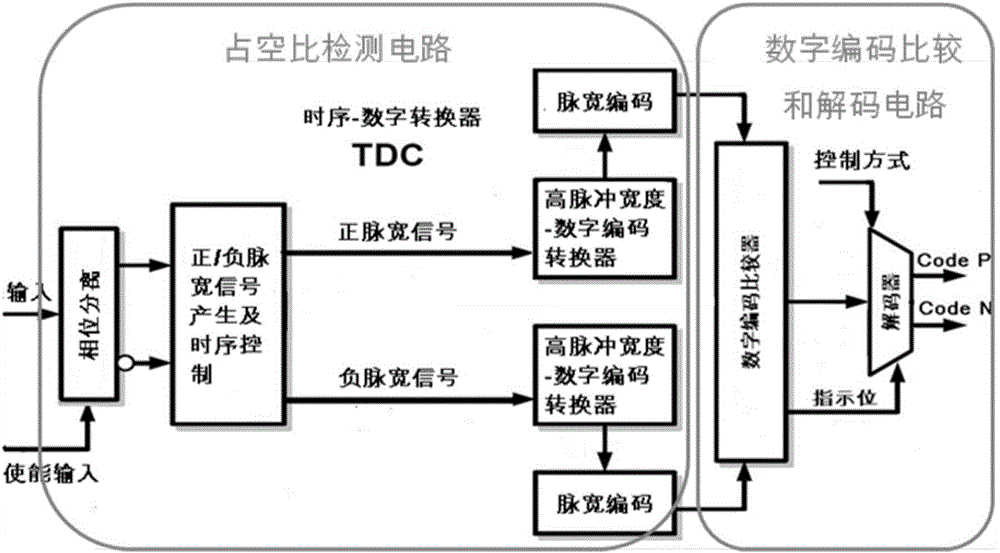

[0037] The present invention is an adaptive duty cycle detection and adjustment receiver, such as figure 2As shown, it at least includes a bias circuit 10, a first-stage amplifier circuit 20, a second-stage amplifier circuit 40 and a duty cycle dynamic detection circuit 50; the load resistance in the first-stage discharge circuit 20 is set as a load resistance array 30;

[0038] The bias circuit 10 is connected to the first-stage amplifying circuit 20 and the second-stage amplifying circuit 40 of the receiver by the bias voltage signal generated by the on-chip active ci...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More