Switch capacitor integrator circuit for eliminating offset voltage

A technology of offset voltage and switched capacitors, which is applied in the direction of voltage/temperature change compensation, reliability improvement and modification, etc. It can solve the problems that the final parameters cannot be matched, and the offset voltage of the amplifier is not considered, so as to achieve simple structure, high precision and wide application foreground effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

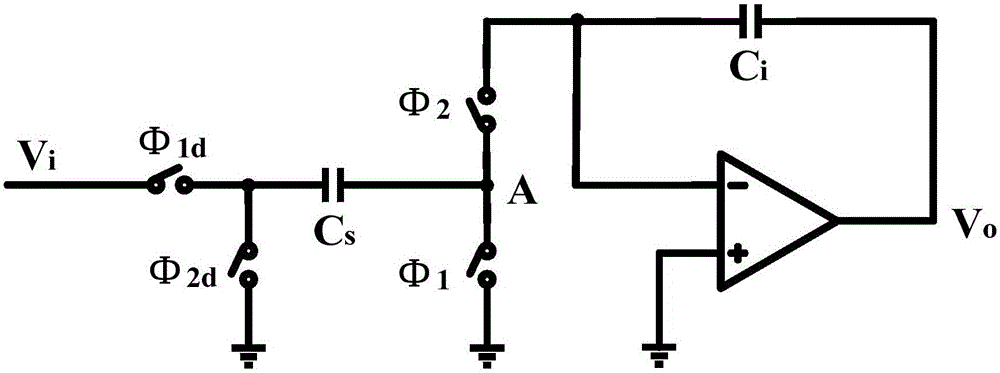

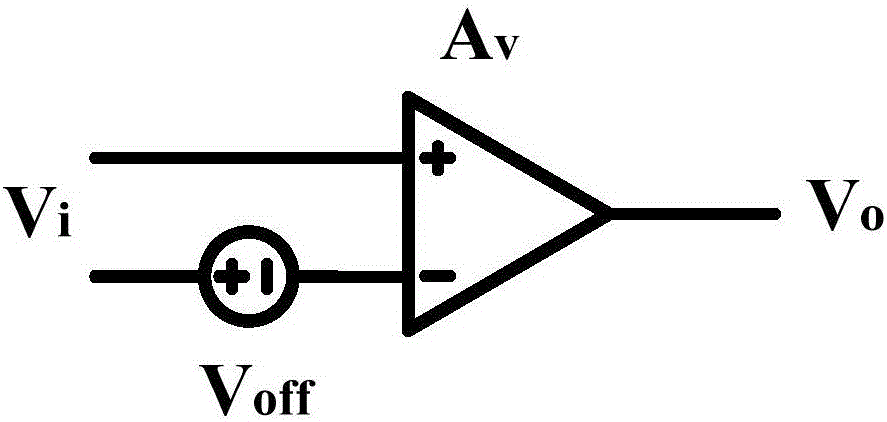

[0054] figure 1 Shown as a traditional switched capacitor integrator circuit, the traditional switched capacitor integrator circuit shown does not take into account the offset voltage present in the amplifier. During the manufacturing process of the amplifier, its final parameters cannot be completely matched with the design situation, so that the output voltage is not equal to the input voltage multiplied by the gain. In order to facilitate the analysis, an offset voltage V is generally superimposed on the input of the amplifier. off to simulate such non-ideal factors, such as figure 2 shown. At this time, the relationship between the output and input of the amplifier is equivalent to:

[0055] V o =A v (V i +V off )

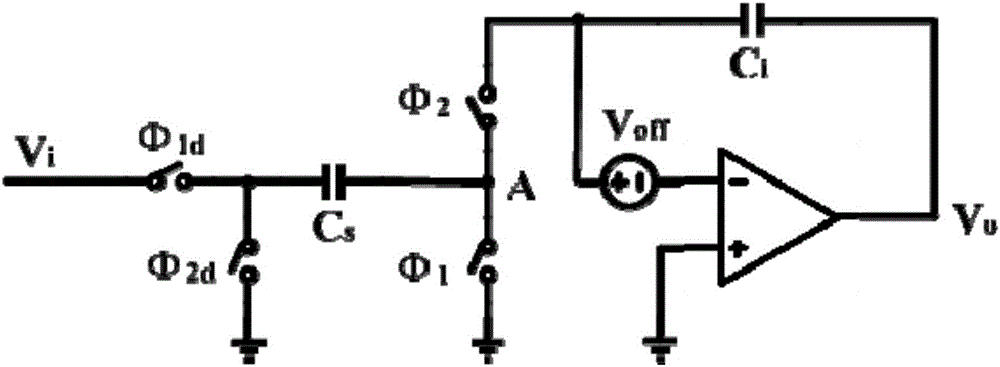

[0056] Among them, A v is the gain factor of the amplifier, when considering the offset voltage of the amplifier, the output value of the switched capacitor integrator is also affected by the offset voltage. image 3 is the switched capacitor integra...

Embodiment 2

[0078] Such as Figure 5 ~ Figure 7 As shown, this embodiment provides a switched capacitor integrator circuit for eliminating offset voltage.

[0079] In the analysis of embodiment 1, it is mentioned that some special occasions will use the inverter as the amplifier, and its structure is as follows Figure 5 shown. In a digital circuit, the input and output of the inverter are either 0 or 1, and its actual voltage value can only be close to the power supply voltage or ground. In this case, the inverter does not have an amplification function. In general, an inverter as an amplifier needs to bias its input and output bias voltages near half the power supply voltage in order to achieve a more ideal amplification effect. But because of this, an inverter cannot zero the voltage at its input through a "virtual ground" like a normal amplifier. exist Figure 5 In , the inverter will form a stable DC bias state through the feedback network, and at this time there will be a bias ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More