Plasma enhanced chemical vapor deposition of films for improved vertical etch performance in 3D NAND memory devices

A plasma and film technology, applied in gaseous chemical plating, electrical components, electrical solid devices, etc., can solve problems such as plasma damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

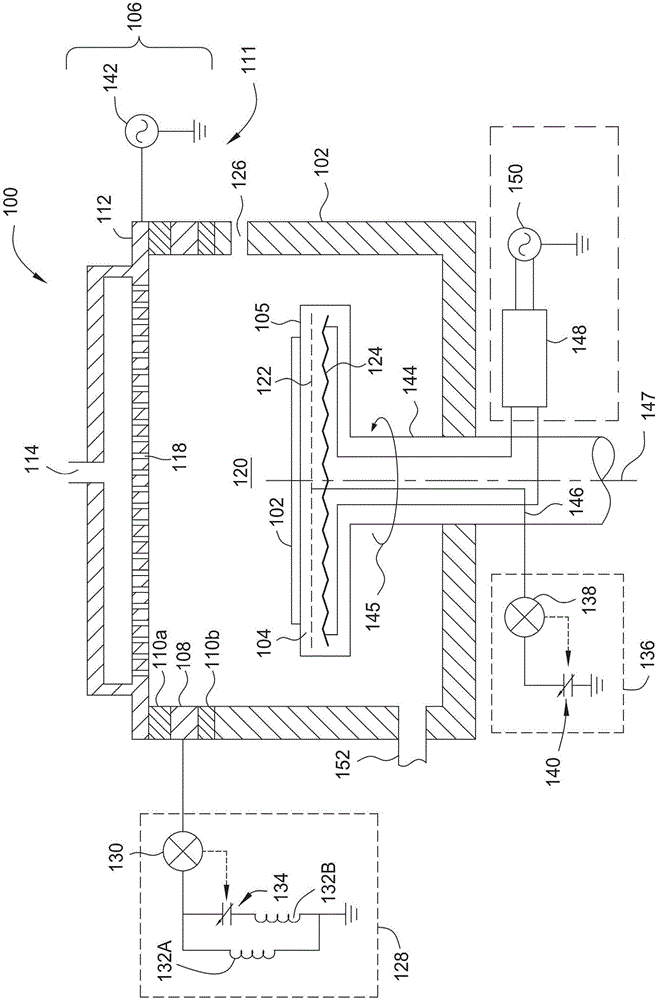

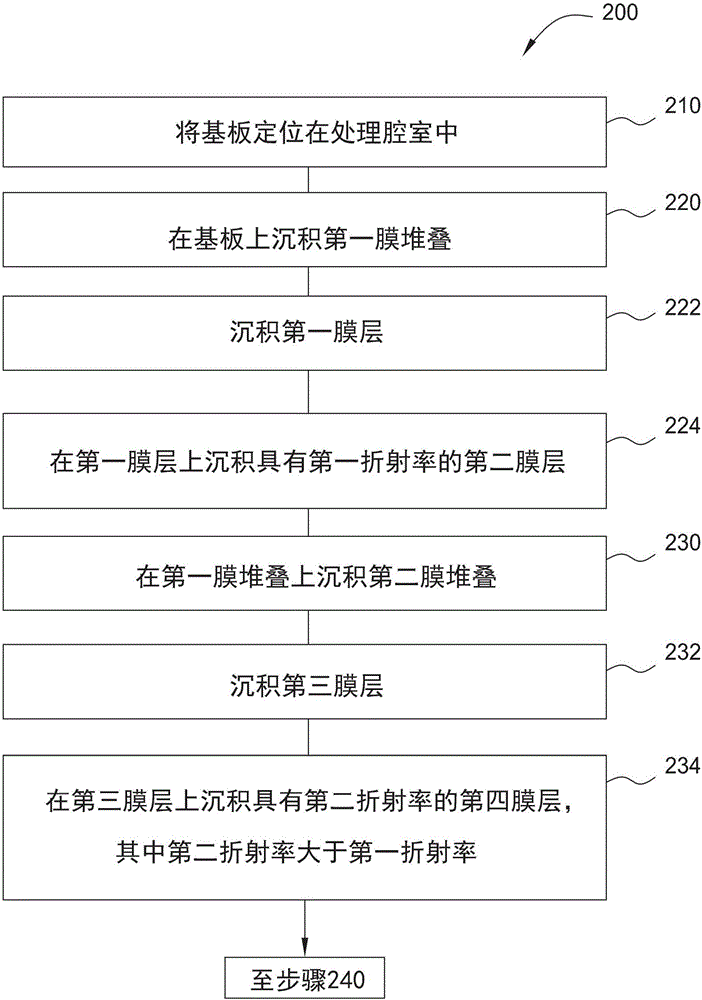

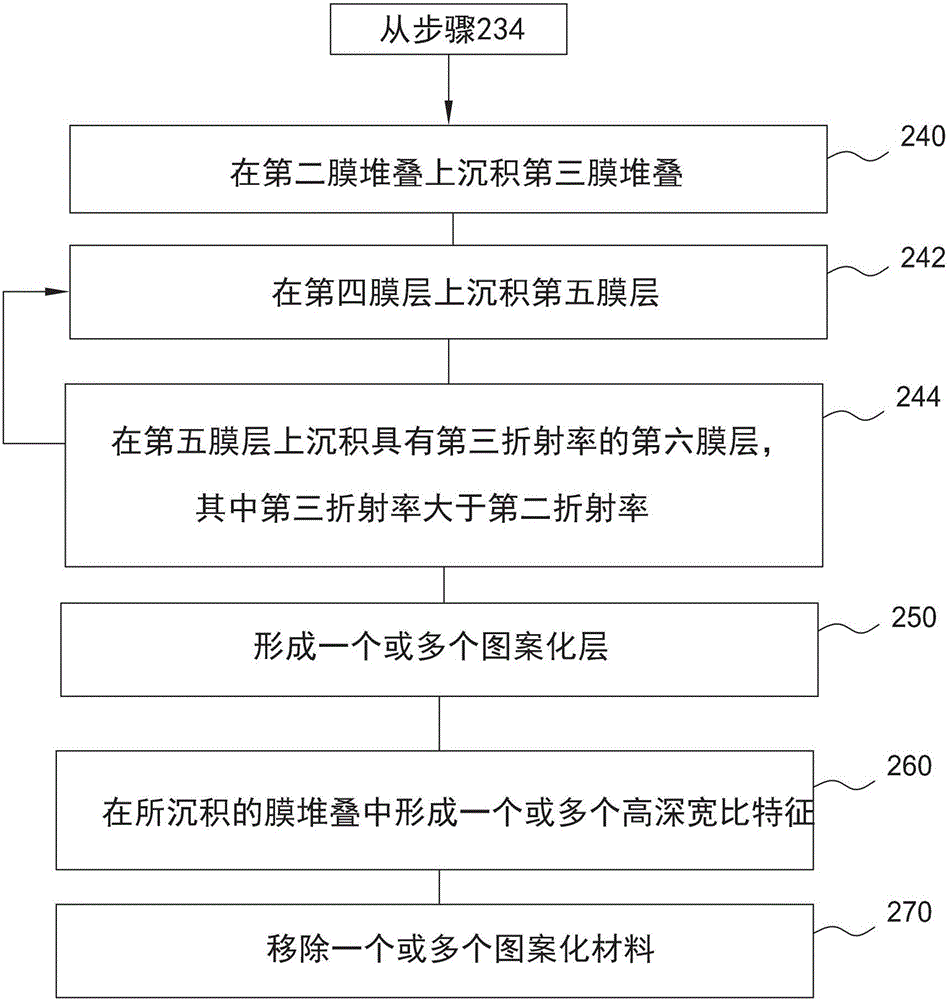

[0018] The following disclosure describes thin films having high aspect ratio features formed therein, processes for depositing the thin films and forming high aspect ratio features therein, and apparatus for accomplishing the above processes. in the description below and in the figure 1 Specific details are set forth through Figure 5 to provide a thorough understanding of various implementations of the present disclosure. Additional details describing well-known methods and systems commonly associated with the deposition of thin films are not set forth in the following disclosure in order to avoid unnecessarily obscuring the description of various implementations.

[0019] Many of the details, components, and other features described herein are merely illustrative of particular implementations. Accordingly, other implementations may have other details, components, and features without departing from the spirit or scope of the present disclosure. Additionally, additional im...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| diameter | aaaaa | aaaaa |

| diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More