A digital-analog mixed-signal chip testing system and method

A technology of chip testing and digital-analog mixing, which is applied in the field of chip test systems for digital/analog and analog/digital converters, can solve problems such as poor reliability and stability, reduced authenticity of test data, and strong module coupling. Increase reliability and stability, ensure test effectiveness, and ensure the effect of communication rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

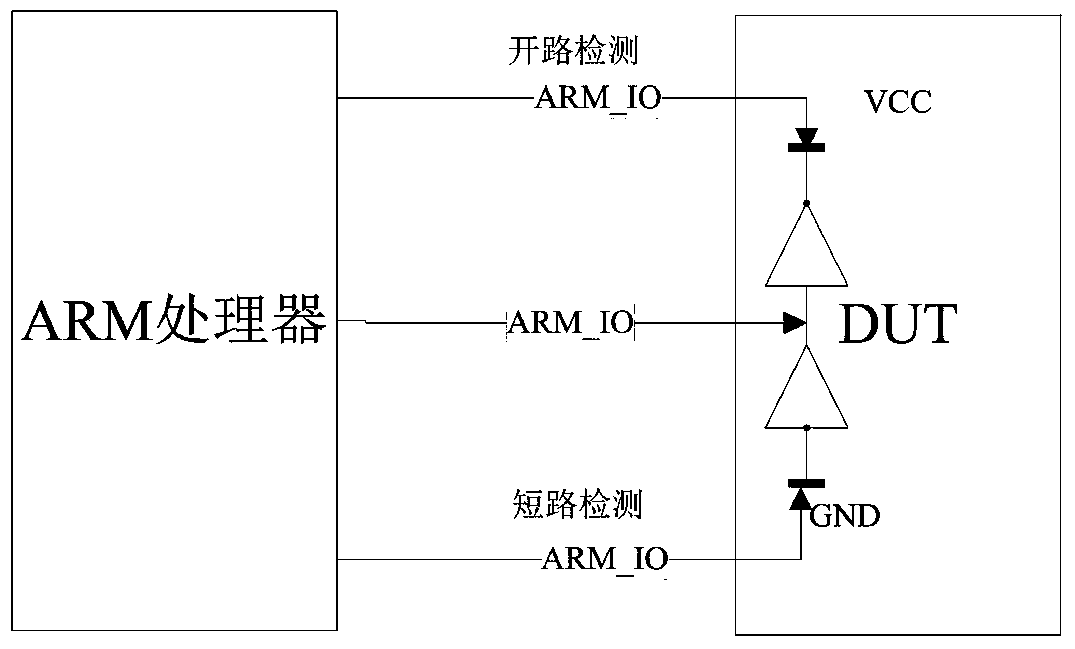

[0046] figure 1 Shown is the structural representation of the system realized by the present invention. As shown in the figure, the test device can test the digital / analog and analog / digital modules in addition to the MCU and the dedicated DAC and ADC with built-in digital-analog modules; On the other hand, it can be used as a system to display chip performance parameters to customers who use the chip. By operating a PC, it can display 12-digit / analog and analog / digital chip performance parameters to designers or customers.

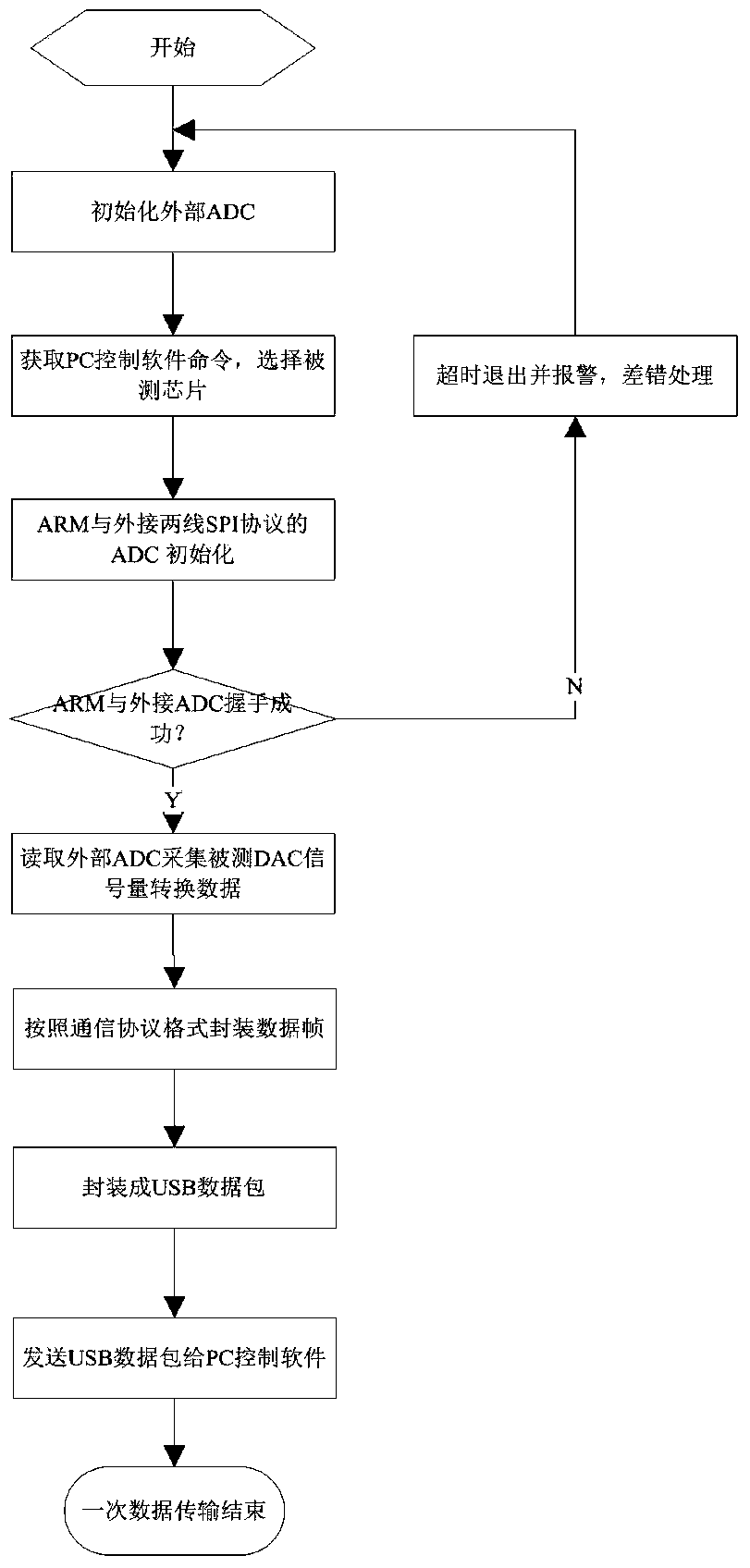

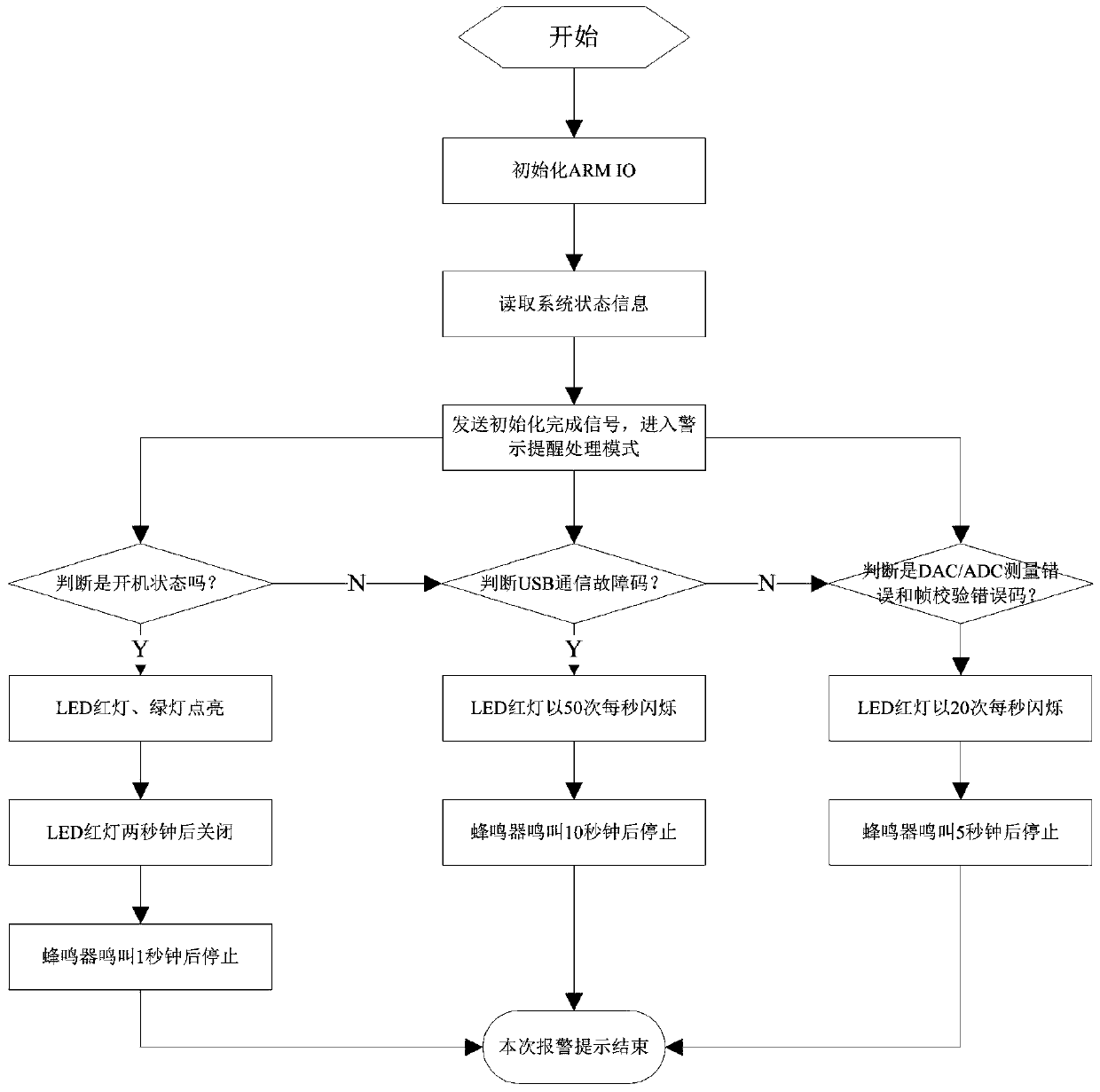

[0047] The digital / analog and analog / digital chip test system developed ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More