Semiconductor device and manufacturing method therefor

A manufacturing method and semiconductor technology, applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of technical difficulty, shallow depth, narrow width, etc., and achieve the effect of increasing the installation strength

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

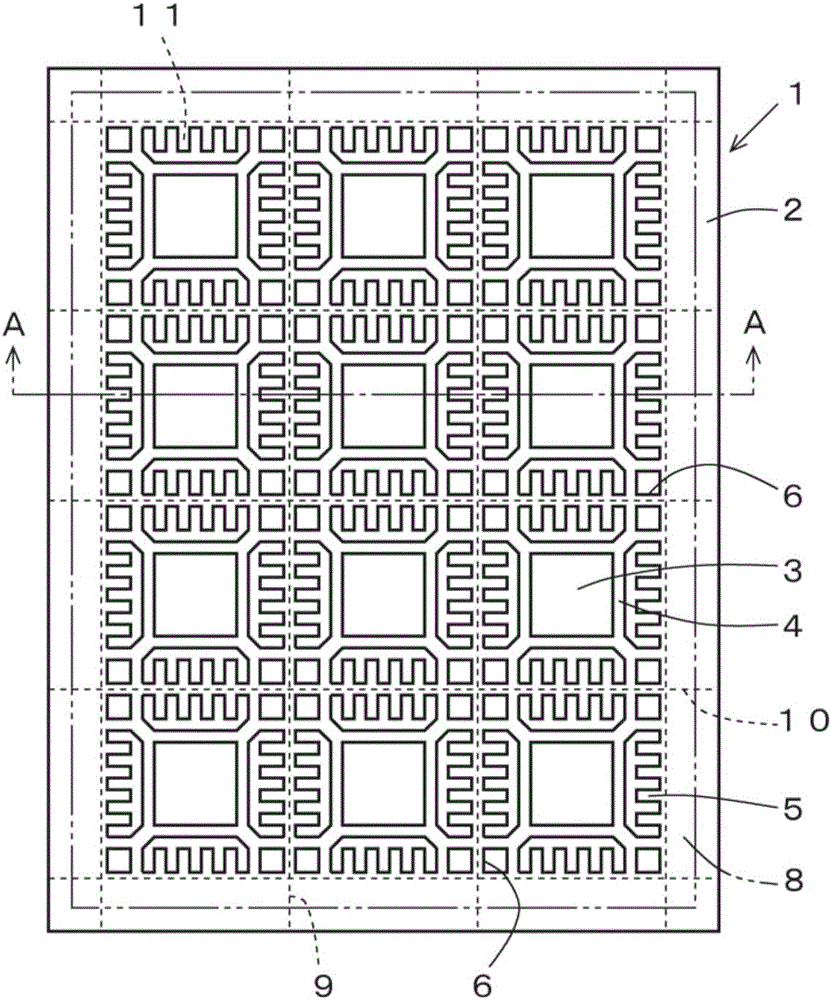

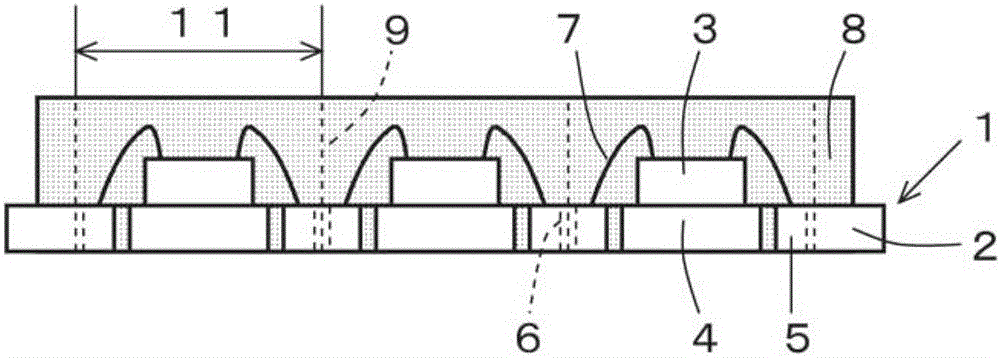

[0037] refer to Figure 1A ~ Figure 5B Embodiment 1 of the semiconductor device according to the present invention will be described. For ease of understanding, each drawing in this application is appropriately omitted or exaggerated and schematically drawn. Mark the same mark on the same structural element, and omit the description appropriately.

[0038] Such as Figure 1A As shown, the QFN substrate 1 is a to-be-cut object to be finally cut and separated into pieces. The QFN substrate 1 has a lead frame 2 . In the lead frame 2 , semiconductor chip mounting portions (die pads) 4 on which semiconductor chips (functional elements) 3 are respectively mounted are arranged in a matrix. The lead frame 2 contains metal such as copper (Cu) and 42 alloy (Fe—Ni). Lead-free metal plating or lead-free solder plating (not shown) is often formed in advance on the surface of the lead frame 2 . A large number of leads 5 serving as connection terminals for connection to the outside are...

Embodiment 2

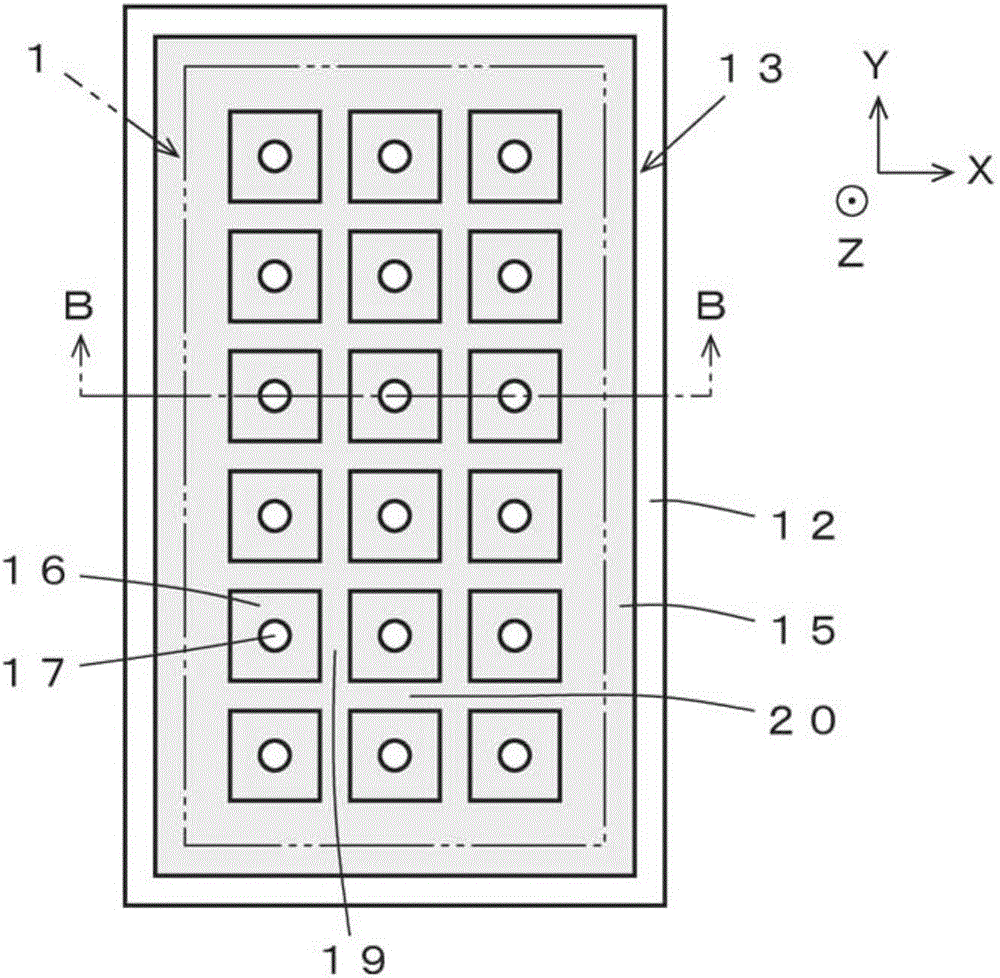

[0069] refer to Figure 6A , Figure 6B , Figure 7A , Figure 7B The method of performing the electroplating treatment on the QFN substrate 1 according to the present invention will be described respectively. Figure 6A , Figure 6B The illustrated QFN substrate 1 is a QFN substrate in which nine die pads 4 are arranged along the long-side direction and three die pads 4 are arranged along the short-side direction. Figure 6A , Figure 6B , Figure 7A , Figure 7B The illustrations of the lead wires are omitted.

[0070] about Figure 6AFor example, the cutting groove 22 (the portion indicated by the solid line in the figure) is formed in a portion where the sealing resin 8 is formed in a plan view (area surrounded by a dotted line in the figure). Therefore, the cutting grooves 22 are not formed in the offcut portions 32a, 32b, 32c, and 32d (portions indicated by hatching in the figure) included in the lead frame 2 . In this case, at one end of each dicing line (part...

Embodiment 3

[0078] refer to Figure 8 A dicing device used when manufacturing the semiconductor device according to the present invention will be described. Such as Figure 8 As shown, the dicing device 34A is, for example, a device for singulating the QFN substrate 1 to be cut into a plurality of QFN products 26 . The cutting device 34A includes a receiving unit A, a cutting unit B, and a delivery unit C as constituent elements, respectively. Each component (accepting unit A, cutting unit B, delivery unit C) is replaceable and can be attached and detached from other components.

[0079] The receiving unit A is provided with a preparation stand 35 . The QFN substrate 1 is received from the resin sealing device which is the device of the previous step. The QFN substrate 1 is arranged on the preparation table 35 with the sealing resin 8 side facing downward. The receiving unit A is provided with a control unit CTL that sets and controls the operation, cutting conditions, and the like of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More