Formation method of semiconductor structure

A semiconductor and gate structure technology, which is applied in the field of semiconductor structure formation, can solve the problem that shallow doped regions are difficult to meet the requirements of the process, and achieve the effect of reducing performance dependence and reducing cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

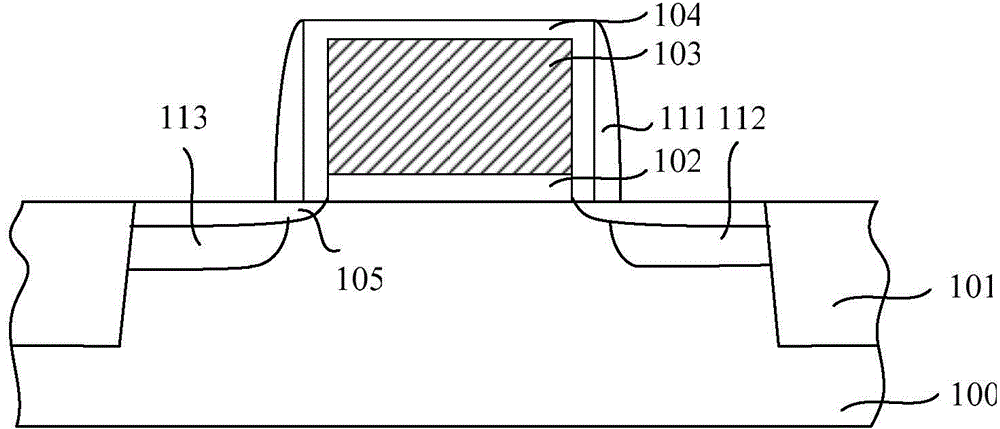

[0036] As mentioned in the background technology, the lightly doped region of the transistor formed in the prior art is difficult to meet the requirements of the process. The depth is still difficult to control.

[0037] Studies have found that in order to form a shallow doped region with a very shallow depth (15-30 angstroms), generally lower implantation energy (for example, less than 2Kev) is required, but ultra-low implantation energy (for example, less than 500ev) has a great impact on the implantation machine. The performance requirements of the MOS are improved, and the purchase of a new implantation machine will undoubtedly increase the production cost. In addition, depending on the type of implanted ions, the implantation depth is also difficult to control, especially in the production process of PMOS, by implanting boron ions to form ultra-shallow In the shallow doped region, because the mass of boron ions is relatively light and the particles are small, under the sa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More