Binary field bit-width-variable modular multiplication operator

An operator and binary field technology, applied in instruments, calculations, and calculations using non-numerical representations, etc., can solve problems affecting performance, line delay, waste of resources, etc., to enhance applicability and reduce area. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The preferred embodiments of the present invention will be described below in conjunction with the accompanying drawings. It should be understood that the preferred embodiments described here are only used to illustrate and explain the present invention, and are not intended to limit the present invention.

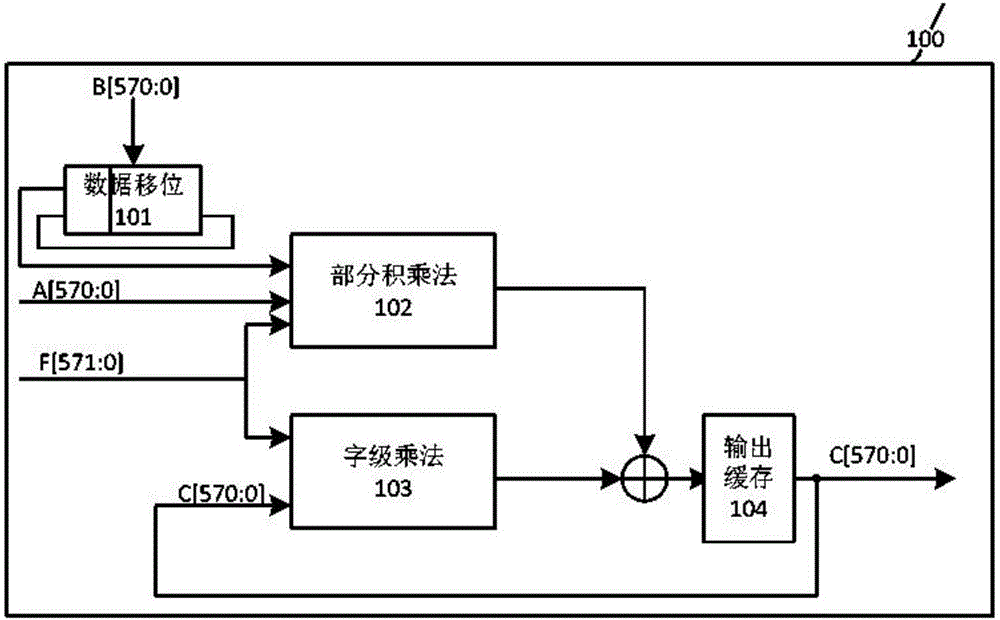

[0039] figure 1 It is a schematic diagram of the overall hardware structure of the modulo multiplier with variable bit width of the present invention. The binary domain bit-width variable modular multiplication operator includes a partial product multiplication unit 102, a word-level multiplication unit 103, an output buffer unit 104, and is characterized in that it also includes a data shift unit 101 and a control unit;

[0040] The control unit is simultaneously connected to the data shift unit, partial product multiplication unit, word-level multiplication unit and output buffer unit; the control unit is a state machine, which controls the data shift unit, partia...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More